TTL与三态门(第六讲)2014

实验一 TTL、三态门电路参数测试(实验内容)_2013.04

实验一 TTL 和 三态门电路参数测试

杭州电子科技大学

电工电子实验中心

一、实验所用器件型号及管脚排列

VCC

14

4A

13

4B

12 &O &O

4Y

11

3A

10

3B

9 &O &O

3Y

8

VCC

14

4E

13

4A

12

1

EN EN

4Y

11

3E

10

3A

9

1

EN EN

3Y

8

1

1

1

2

3

4

5

6

7

0 1 0 1

4.用2输入与非门(74LS00)实现三人参加的

表决电路。

VoL 0 VI(V) VoFF VTH VoN Vo(V) VoH

90%*VoH

高电平噪声容限NH。

3、三态门功能测试

选用型号为74LS126的集

成电路,参考其引脚排列 及逻辑符号,按右边电路 图测试高阻状态,将实验 结果填入下表。

输入

输出Y(接上拉 电阻)

输出Y(接下拉电 阻)

E

A

Y

0 1

10K

&

V V

VI VO

0

0.3

0.5

0.85

0.9

0.95

1.0

1.05

1.1

1.15

1.2

1.3

1.4

1.5

TTL与非门参数测试

调节电位器,测出相应的输出电压,在坐标纸上画出电压传输特性

曲线,并在曲线中求得以下参数: 输出高电平VOH, 关门电平VOFF, 阈值电压VTH, 输出低电压VOL, 开门电平VON, 低电平噪声容限VNL,

TTL逻辑门电路

TTL逻辑门电路原文TTL逻辑门电路以双极型半导体管为基本元件,集成在一块硅片上,并具有一定的逻辑功能的电路称为双极型逻辑集成电路,简称TTL逻辑门电路。

计算机/外设下面首先讨论基本的BJT反相器的开关速度不高的原因,再讨论改进的TTL反相器和TTL逻辑门电路。

一、基本的BJT反相器的动态性能BJT开关速度受到限制的原因主要是由于BJT基区内存储电荷的影响,电荷的存进和消散需要一定的时间。

考虑到负载电容CL的影响后基本反相器将成为如下图所示的电路。

图中CL包含了门电路之间的接线电容以及门电路的输进电容。

当反相器输出电压vO由低向高过渡时,电路由VCC通过Rc对CL充电。

当vO由高向低过渡时,CL又将通过BJT放电。

这样,CL的充、放电过程均需经历一定的时间,这必然会增加输出电压vO 波形的上升时间和下降时间。

特别是CL充电回路的时间常数RcCL较大时,vO 上升较慢,即增加了上升时间。

基于器件内部和负载电容的影响,导致基本BJT反相器的开关速度不高。

寻求更为实用的TTL电路结构,是下面所要讨论的题目。

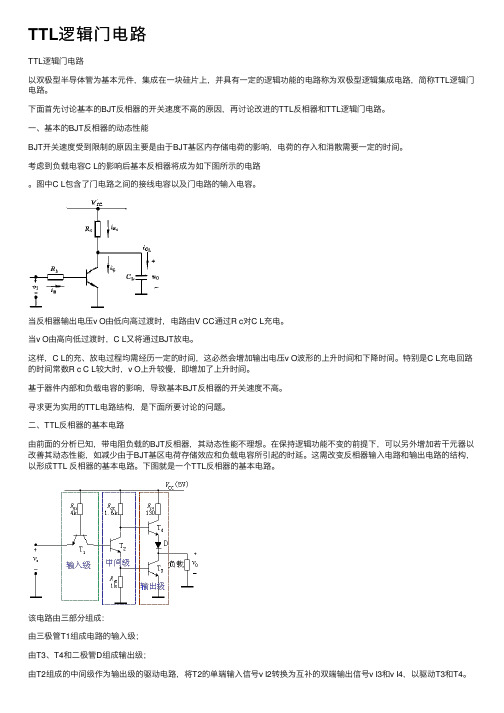

二、TTL反相器的基本电路由前面的分析已知,带电阻负载的BJT反相器,其动态性能不理想。

在保持逻辑功能不变的条件下,可以另外增加若干元器以改善其动态性能,如减少由于BJT基区电荷存储效应和负载电容所引起的时延。

这需改变反相器输进电路和输出电路的结构,以形成TTL反相器的基本电路。

下图就是一个TTL反相器的基本电路。

该电路由三部分组成:由三极管T1组成电路的输进级;由T3、T4和二极管D组成输出级;由T2组成的中间级作为输出级的驱动电路,将T2的单端输进信号vI2转换为互补的双端输出信号vI3和vI4,以驱动T3和T4。

1.TTL反相器的工作原理这里主要分析TTL反相器的逻辑关系,并估算电路中有关各点的电压,以得到简单的定量概念。

(1)当输进为高电平,如vI=3.6V时,电源VCC通过Rbl和T1的集电结向T2、T3提供基极电流,使T2、T3饱和,输出为低电平,如vO=0.2V。

详解TTL电路

详解TTL门电路一、什么是TTL门电路TTL 是一种集成电路,通过使用双极性晶体管组合来做到具有驱动能力的逻辑输出。

TTL 最重要的特性是门的输入在未连接时将为逻辑高电平。

在硬件电路中,会用到逻辑门这样的数字器件,对于这样的数字器件,从内部工艺结构来份的话主要有两个大的分支:一个是晶体管构成的,另一个是场效应管构成的。

而晶体管构成的门电路,被称为TTL门电路。

二、TTL电路工作原理TTL门电路也分很多种,比如说非门、与非门、或非门、与或非门以及OC输出的与非门。

虽然种类多,但是基本的工作原理都是类似的。

以常用的与非门电路为例对其工作原理进行介绍。

图 1 非门的TTL电路从图1中可以看出非门电路是由Q1输入级、Q2中间级以及Q3、Q4输出级组成。

1、输入级:Q1从结构上把它看成由二极管构成的,两个二极管的P结背靠背,N结分别连接输入和Q2的基极。

2、中间级:由三极管Q2和电阻R2、R4组成。

在电路的开通过程中利用Q2的放大作用,为输出管Q3和Q4提供较大的基极电流,加速了输出管的导通。

所以,中间级的作用是提高输出管的开通速度,改善电路的性能。

3、输出级:由三极管Q3、Q4、二极管D1和电阻R3组成。

从图中可以看出,输出级由三极管Q4实现逻辑非的运算。

但在输出级电路中用三极管Q3、二极管D1和R3组成的有源负载来使输出级具有较强的负载能力。

其中D1可以起到三极管be反向击穿的保护作用。

工作原理:1、当输入端Input为逻辑低电平时,电流流经R1至Input,Q1晶体管导通,此时Vb(Q2)的电压小于Vbe导通电压0.7V,Q2晶体管截止。

此时由于R2与R4的存在,使Q3导通、Q4截止,在Out上输出高电平。

由图1中输出结构可知,此时输出高电平电压将为:Vout=Vcc−Vce−V D1≈Vcc-1V。

2、当输入端Input为逻辑高电平时,Q1晶体管截止,此时电流流经R1和Q1的PN结,流向Q2的基极,Q2晶体管导通。

实验三、TTL集电极开路门与三态输出门的应用

实验三、TTL集电极开路门与三态输出门的应用一、实验目的1、掌握TTL集电极开路门(OC门)的逻辑功能及应用。

R对集电极开路门的影响。

2、了解集电极负载电阻L3、掌握TTL三态输出门(TSL门)的逻辑功能及应用。

二、仪器和用具OL iH I —负载门高电平输入电流(<50uA ) iL I —负载门低电平输入电流(<1.6mA )C E —L R 外接电源电压n —OC 门个数 N —负载门个数m —接入电路的负载门输入端总个数L R 值须小于max L R ,否则OH U 将下降,L R 值须大于min L R ,否则L R OL U 将上升,又由于LR 的大小会影响输出波形的边沿时间,在工作速度较高时,L R 应尽量选取接近min L R . 2. TTL 三态输出门(TSL 门)TTL 三态输出门是一种特殊的门电路,它与普通的TTL 门电路结构不同,它的输出端除了通常的高电平、低电平两种状态外(这两种状态均为低阻状态),还有第三种输出状态—高阻状态,处于高阻状态时,电路与负载之间相当于开路。

图2.3-4是三态输出四总线缓冲器的逻辑符号,它有一个控制端(又称禁止端或使能端)E ,E =0为正常工作状态,实现Y=A 的逻辑功能;E =1为禁止状态,输出Y 呈高阻状态。

这种在控制端加低电平电路才能正常工作的工作方式称低电平使能。

三态输出门按逻辑功能及控制方式分有各种不同的类型,在实验中所用的三态门的型号是74LS125,引脚图如图2.3-5所示。

三态电路主要用途之一是实现总线传输,即用一个传输通道以选通方式传送多路信息。

图3-6所示,电路把若干个三态TTL 电路输出端直接连接在一起构成三态门总线,使用时,要求只有需要传输信息的三态控制端处于使能态,其余各门都处于禁止状态。

四、实验内容1. TTL 集电极开路与非门74LS03负载电阻L R 的确定用两个集电极开路与非门“线与”使用驱动一个TTL 非门,负载电阻由一个200Ω电阻和一个470k Ω电位器串接而成,取C E =5V ,OH U =3.6V ,OL U =0.3V ,OL U 按图3-7连接实验电路,接通电源,用逻辑开关改变两个OC 门的输入状态,先使OC 门“线与”输出高电平,调节P R 使OH U =3.5V ,测得此时的L R 即为max L R ,再使电路输出低电平用两个集电极开路与非门“线与”使用驱动一个TTL 非门,负载电阻由一个200Ω电阻和一个470k Ω电位器串接而成,取C E =5V ,OH U =3.6V ,OL U =0.3V ,OL U 按图3-7连接实验345TitleNum berSize B Date:13-Dec-2003File :F:\T UXIN G\ZSW.ddbYA123443211413121110981234567E3CCU +A 1E1地Y1E2A 2Y2Y3Y4E4A3A4图2.3-4 图2.3-5E321DCBA1413121110981234567ABCD6543TitleNum ber RevisionSize 数 据 总 线nA nE 1E CCU +1A 2A .. .2E 地图2.3-6 图2.3-774LS 04电路,接通电源,用逻辑开关改变两个OC 门的输入状态,先使OC 门“线与”输出高电平,调节P R 使OH U =3.5V ,测得此时的L R 即为max L R ,再使电路输出低电平OL U =0.3V ,测得此时的L R 即为min L R ,图2.3-8所示。

数字逻辑课件——TTL集电极开路的门和三态门

当EN1 = 1而其余为0时,门G2和G3呈 高阻,信号A1的非送到了总线Y上;

1

0

0

图2-2-23 用三态非门构 成单向总线

15

当仅有EN2 = 1时,信号A2的非送到 了总线Y上;

当仅有EN3 = 1时,信号A3的非送到 了总线Y上。

这样,就实现了信号A1,A2,A3向总 线Y的分时传送。见表2-2-3所示,

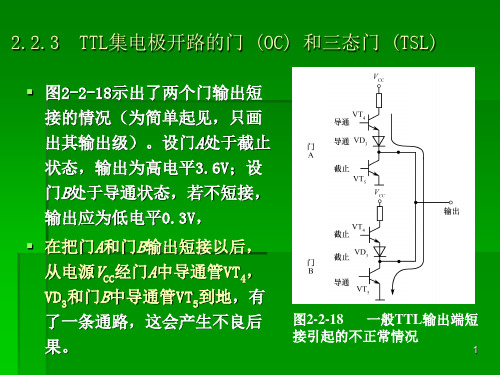

与非门1:

i

功耗

T4热击穿

与非门2:UOL

不允许输出直接“短

接”

2

(1)输出电平既非“1”(3.6V),也非“0”(0.3V),而 是两者之间的某一值,导致逻辑混乱。 (2)导致输出级电流远大于正常值,导致功耗剧增,可能烧 毁管子。 两种允许输出端连接在一起的TTL电路。 (一)集电极开路门电路—OC门(Open-Collector Gate) 集电极开路与非门的电路结构与逻辑符号示于图2-2-19。它

而当两个门的输出端连在一起,只要其中 有一个输出低电平(即VT5和VT’5中至少 有一个饱和),总的输出Y就是低电平;

7

只有当两个门都输出高电平(即VT5和 VT’5都截止)时,总的输出Y才是高电平, 这相当于“与”逻辑关系:

Y Y1 Y2 A1B1 A2B2

8

由于这个“与”关系是通过将输出线Y1和Y2短接实现的,

27

VD3的作用:VD3经过VT2为VT4提 供了一个低电阻放电回路,使

VT4更快地截止,有利于缩短传 输延迟时间。

VD4的作用:Y由高变低时,VD4经 VT2c、VT5b为CL提供另一条放电回 路,既加快了CL的放电速度,又 为VT5增加了基极驱动电流,加 快了VT5的导通。

数电实验二 TTL集电极开路门与三态门的应用

实验内容一:三态门的应用

示波器观察数据总线,并记录后四种情况下的输出波 形,注意画出坐标系,标明周期和幅值。 1 当四个控制端都为高电平时,记录指示灯的状态 2 当1脚为低电平,其余为高电平 3 当4脚为低电平,其余为高电平 4 当10脚为低电平,其余为高电平 5 当13脚为低电平,其余为高电平 注意:同一时刻,四个控制端只能有一个低电平

芯片引脚图

实验内容一:三态门的应用

三态输出的四总线缓冲器

实验内容一:三态门的应用

74LS125(三态输出四பைடு நூலகம்线缓冲器): 14脚接5伏电源,7脚接地; 1、4、10、13脚分别逻辑电平开关上; 3、6、8、11脚接在一起作为数据总线,并 接到电平指示灯; 2脚接10KHZ的数字脉冲信号(由CH1提供, 高电平5V,低电平0V),5脚接5伏,9脚接 地,12脚接500HZ的数字脉冲信号(由CH2 提供,高电平3V,低电平0V)

数电实验二

TTL集电极开路门 与三态门的应用

实验目的

1 学会三态门的逻辑功能的测试方法及其 应用 2 学会TTL集电极开路门电路的逻辑功能 测试方法及其应用

实验器件

电子技术实验台 万用表 示波器 信号源 74LS03:四-二输入与非门,OC门 1片 74LS125:三态输出四总线缓冲器 1片

实验内容二:集电极开路门的应用

集电极开路门应用于信号源电平的转换

实验内容二:集电极开路门的应用

74LS03(四二输入与非门,OC门): 14脚接5伏电源,7脚接地; 1,2脚同时接1KHZ的数字脉冲信号; 3,4,5脚相连,3脚再通过2KΩ的上拉电阻接5 伏 6脚通过2KΩ的上拉电阻接12伏 示波器双踪同时观察2,3脚波形,记录下来,注 意相位关系和幅度大小 示波器双踪同时观察3,6脚波形,记录下来,注 意相位关系和幅度大小

三态门的概念

三态门的概念

三态门是电子学中涉及到的非常重要的基础概念,即三种开、关状态的电路形状。

它会产生三种电平输出:1或0,对或错,开或关。

换句话说,三态门能够转

换一组1或0的输入,并产生不同的输出。

三态门的基本原理是将两个开关或多个开关通过电路相互联接,可以实现继电器开关的控制。

与延时开关和脉冲开关相比,三态门具有能够更好地控制输入信号,以及实现更加复杂电子电路和系统的优点。

三态门运算符(TFO)是一种广泛应用的模型,它通过为电路中的每个元素提供激活信号,来模拟这个电路的行为。

最常用的三态门运算符是NAND,NOR和

可控矩阵,它们能够与其他电路元件相结合,提高电路的可靠性和可拓展性。

最著名的三态门应用之一是半导体芯片中的置换门(TTL)和可控置换门(CMOS)。

TTL元件是门与门之间的逻辑连接,它们可以实现数据的循环储存、数据的移位及其他各种操作。

CMOS元件和TTL及延时门元件类似,可用于实现

微处理器、复杂电路和电子设备的编程控制等功能。

三态门可以被用来实现高性能的控制系统和网络安全,它不仅可以为电子系统提供高效信号传输能力,而且可以在各个网络层面提供有效的数据保护。

三态门可以用来实现网络控制和数据传输安全,是多种技术的重要组成部分,并且常常被用来生成高度安全的网络设置。

通俗来讲,三态门具有对电子设备,特别是半导体芯片及微控制器应用中十分重要的作用,尤其它具有更多的控制状态,可以实现更复杂的逻辑功能,更好的控制信号灵活性。

它能够提供一个坚实的基础,实现更先进的电子系统设计,为复杂电子技术的发展提供支持。

TTL逻辑门电路

TTL逻辑门电路TTL逻辑门电路以双极型半导体管为基本元件,集成在⼀块硅⽚上,并具有⼀定的逻辑功能的电路称为双极型逻辑集成电路,简称TTL逻辑门电路。

下⾯⾸先讨论基本的BJT反相器的开关速度不⾼的原因,再讨论改进的TTL反相器和TTL逻辑门电路。

⼀、基本的BJT反相器的动态性能BJT开关速度受到限制的原因主要是由于BJT基区内存储电荷的影响,电荷的存⼊和消散需要⼀定的时间。

考虑到负载电容C L的影响后基本反相器将成为如下图所⽰的电路。

图中C L包含了门电路之间的接线电容以及门电路的输⼊电容。

当反相器输出电压v O由低向⾼过渡时,电路由V CC通过R c对C L充电。

当v O由⾼向低过渡时,C L⼜将通过BJT放电。

这样,C L的充、放电过程均需经历⼀定的时间,这必然会增加输出电压v O波形的上升时间和下降时间。

特别是C L充电回路的时间常数R c C L较⼤时,v O上升较慢,即增加了上升时间。

基于器件内部和负载电容的影响,导致基本BJT反相器的开关速度不⾼。

寻求更为实⽤的TTL电路结构,是下⾯所要讨论的问题。

⼆、TTL反相器的基本电路由前⾯的分析已知,带电阻负载的BJT反相器,其动态性能不理想。

在保持逻辑功能不变的前提下,可以另外增加若⼲元器以改善其动态性能,如减少由于BJT基区电荷存储效应和负载电容所引起的时延。

这需改变反相器输⼊电路和输出电路的结构,以形成TTL 反相器的基本电路。

下图就是⼀个TTL反相器的基本电路。

该电路由三部分组成:由三极管T1组成电路的输⼊级;由T3、T4和⼆极管D组成输出级;由T2组成的中间级作为输出级的驱动电路,将T2的单端输⼊信号v I2转换为互补的双端输出信号v I3和v I4,以驱动T3和T4。

1.TTL反相器的⼯作原理这⾥主要分析TTL反相器的逻辑关系,并估算电路中有关各点的电压,以得到简单的定量概念。

(1)当输⼊为⾼电平,如v I=3.6V时,电源V CC通过R bl和T1的集电结向T2、T3提供基极电流,使T2、T3饱和,输出为低电平,如v O=0.2V。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

R2

T1

c1

T2 R5

T3

T4

R

L

T5

ui

R3

4 .3 R R ui (5 U be1 ) R1 R 3 R

R较小时,ui<UOFF 相当输入低电平,所 以输出为高电平。

20

R增大

RuiuiUON时,输入变高,输出变 低电平。

R1 3k b1

+5V

R4

10

前后级之间电流的联系

&

&

11

前级输出为 高电平时

+5V

R4

+5V 反偏

R1

R2 T3

T4

R5

T1

前级流出电流IOH(拉电 流),后级流入电流 IIH(≤50μA )

前级

后级

12

前级输出为 低电平时

R1

3k b1

+5V

R2

流入前级的电流IOL 约 1.4mA (灌电流),输入 低电平电流IIL。

6

4. TTL与非门的改进 •抗饱和TTL与非门电 路

如右图所示,三极管VT1 、 VT2 和VT5换成了肖特基管(用 肖特基三极管钳位)。

7

4. TTL与非门的改进 •抗饱和TTL与非门电路

抗饱和电路的出发点是为了消除三极管 进入深饱和区时存储电荷的影响,采取必要 的措施,使三极管不工作在深饱和区,减少 由存储电荷的消散所需时间,从而提高与非 门的工作速度。 改进主要围绕提高工作速度、降低功耗、 增强抗干扰能力以及提高集成度方面。

接入高电平,将 不同数据(A、B、 C)分时送至总 线。

C E3

0

40

用途2: 利用三态门实现数据的双向传输

41

习题

P71:

1、题2.2 (中间一小题不做)

2、题2.3

42

R2

IIL1

c1

T1

T2

IOL IIL2

T5

R3

IIL3

前级

17

输出低电平时,后级流入的电流(灌电流): IOL I IL1 I IL 2 输出高电平时,流出前级的电流(拉电流):

IOH I IH1 I IH 2

由于IOL、IOH的限制,每个门电路输出端所 带门电路的个数,称为扇出系数。

R2

A B C

c1

T1 ui

4.3R 1.8(V) 3 R

T2

T3

T4

R5

L

T5

R

R3

21

R临界=2.16K

(6) 开门电平UON :额定负载下,保 证输出为标准低电平时的最小输 入电压值。产品规范值为1.8V (7) 关门电平UOFF :保证输出为标准 高电平时对应的最大输入电压值。 产品规范值为0.8V • 悬空的输入端相当于接高电平。为 了防止干扰,可将悬空的输入端接高 电平。

+5V

R1 3K

c1

T1

T2

T1

T5 R3

13

前级

后级

灌电流的计算

饱和

I OL

5 T5压降 T1的be结压降 R1

5 0 . 3 0 . 7 1.4mA 3

14

关于电流的技术参数

名称及符号 输入低电平电流 IIL 含义 输入为低电平时流入 输 入 端 的 电 流 -1 .4mA。 输入高电平电流 IIH 输入为高电平时流入 输入端的电流 50μ A。 当 IOL> IOL(max)时,输出 不再是低电平。 当 IOH >IOH(max)时, 输出 不再是高电平。

8

5.

TTL与非门的主要参数

(1) 输出高电平UOH 输入一个(或几个)为低时,门电路的 输出电平。典型值为3.6V。 UOH≥ USH =2.4V ( USH标准高电平) (2) 输出低电平UOL 额定负载下,输入全为高时,门电路的 输出电平。典型值为0.3V。

UOL≤ USL =0.4V ( USL标准低电平)

J

33

2 三态门(Tristate Logic , TSL)

三态“与非”门的输出除了具有与 前述“与非”门相同的高低电平外,还 具有高输出电阻的第三种状态,称为高 阻状态。 TTL三态输出“与非”门电路与一 般TTL“与非”门电路相比,只是多出了 一个二极管D,其中A和B是输入端,E是 控制端或称使能端(通常接另一“与非” 门的输出端)。

测试电路

2

输出高电平 u0(V)

UOH (3.6V)

u0(V) “1” 输出低电平

UOL (0.3V) UOH

UOL

(0.3V)

1

2 3 ui(V)

1

2 3 ui(V)

阈值UT=1.4V

传输特性曲线

理想的传输特性

3

UOH

UOL USL

UNL

UNH

UOFF

UON

USH

4

• 标准高电平USH:输出高电平的下限值(2.4V) • 标准低电平USL:输出低电平的上限值(0.4V) • 关门电平UOFF :保证输出为标准高电平USH的 条件下所允许的最大输入低电平(0.8V) • 开门电平UON :保证输出为标准低电平USL的条 件下所允许的最小输入高电平(1.8)

N O N OL I OL (max) / I IL

Байду номын сангаас

一般与非门的扇出系数为8~10。

18

• 输入端通过电阻R接地的情况 输入端 “1”,“0”?

A B C R1 3k b1

+5V

R4

R2

c1

T1 ui

T2

T3

T4

R5

L

T5

R

R3

19

R较小时

A B C

R1 3k b1

+5V

L

&

L2

输出级

T5

L

T5 T5

&

L3

L=L1L2L3

28

L=L1L2L3?

UCC

RL

L1 L2 L3

29

L=0

L

任一导通

L=L1L2L3?

UCC

RL

L1 L2

L=1

F

所以: L=L1L2L3

全部截止

L3

30

VCC (nIOH ' NI IH )R C USH

R C max VCC U SH nIOH ' NI IH

34

R1

+5V

R4

E

A B

E

D

R2

T1

T2

T3

T4

R5

L

T5

E---控制端

R3

35

截止 0 1 E

R1 D

+5V

R4

E

A B

R2

T1

T2

T3

T4

R5

L

T5

L AB

R3

36

导通 1 0 E

截止

R1 D

+5V

R4

E

A B

R2

T1

T2

T3

高阻态

• 高电平噪声容限UNH: UNH = USH - UON (0.6V)

• 低电平噪声容限UNL: UNL = UOFF - USL (0.4V)

• TTL典型值 UOH=3.6V UOL 0.3V

5

4. TTL与非门的改进

•有源泄放TTL与 非门电路 如右图所示, 由三极管VT6及 电阻R3、R6组成。 作用是加快了 VT5的导通和截 止的过程,提高 了与非门的开关 速度。

9

(3) 高电平输入电流IIH 输入漏电流,指某一输入端为高电平, 其它输入端接地时,该高电平输入端的电 流值。一般IIH ≤50μA (拉电流IOH)

(4) 输入低电平电流IIL 指与非门的某一输入端接低电平,其它输 入端接高电平或悬空时,该低电平输入端 的电流值。一般IIL≤1.4mA (灌电流IOL)

22

(8) 平均传输时间 用来表示电路开关速度的参数

平均传输时间

t pd

1 ( t d ( on ) t d ( off ) ) 2

23

2.2.2 其它形式的TTL门电路

1. 集电极开路门(OC门-Open Collector)

它与基本的TTL与非门电 路相比,少了T3和T4两个晶 体管,并将输出管T5的集 电极开路。工作时,T5的 集电极(即输出端)通过外 接电源和电阻RL作为OC门 的有源负载。 解决了一般TTL门电路输 出不能直接相接的问题。

第二章 基本运算电路

§ 2.1 基本逻辑门电路

2.1.1 基本逻辑运算 2.1.2 二极管与门及或门电路 2.1.3 非门电路 2.1.4 DTL与非门

§ 2.2

§ 2.3 § 2.4

TTL逻辑门电路

CMOS逻辑门电路 集成运算运放电路

1

3. TTL与非门的传输特性 • 电压传输特性

+5V

&

ui u0

24

符号

!

&

25