简单的驱动makefile解析

windows下makefile命令详解

windows下makefile命令详解1. 如果已经有vc6的dsp⼯程,可直接导出nmake脚本⽂件(.mak)“Project - Export Makefile...”nmake -f nMakeTest.mak CFG="nMakeTest - Win32 Debug"nmake -f nMakeTest.mak CFG="nMakeTest - Win32 Debug" allnmake -f nMakeTest.mak CFG="nMakeTest - Win32 Release" clean注:如果未指定/F选项,则使⽤当前⽬录下的名为makefile的⽂件【nmake /?】获取更多帮助! vc6:【D:\program files\Microsoft Visual Studio\VC98\Bin】vs2008:【D:\program files\Microsoft Visual Studio 9.0\VC\bin】为了能正确地使⽤命令⾏⼯具及vc6或vs2008下的函数库,需要对⼀些环境变量进⾏设置,最快捷地⽅式是通过如下⽅式打开命令⾏窗⼝(以vs2008为例):2. vs的c++⼯程没有提供导出nmake脚本⽂件的功能,我们只有借助⼯具或⼿动编写nmake脚本⽂件了++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++3. rc.exe 【将.rc资源⽂本转变成.res⼆进制⽂件】/l 0x804 // 默认语⾔ID(⼗六进制数表⽰) 0x804:简体中⽂ 0x409:美国/fo"nMakeTest.res" // 指定rc⽂件输出的res名称例:rc.exe /l 0x804 /fo"nMakeTest.res" /d "_DEBUG" /d "_AFXDLL" “nMakeTest.rc”4. cl.exe 常见选项【将.c,.cpp,.cxx编译成obj⽂件】/nologo // 不打印版权申明信息/I "../include" // 添加头⽂件查找路径(如果路径中带有空格,⼀定要⽤引号括起来)/DWIN32 // 预编译宏定义(win32程序)/D_CONSOLE // 预编译宏定义(控制台程序)/D "_DEBUG" // 预编译宏定义(Debug版本)/D_CRT_SECURE_NO_DEPRECATE // 预编译宏定义(关闭C4996警告。

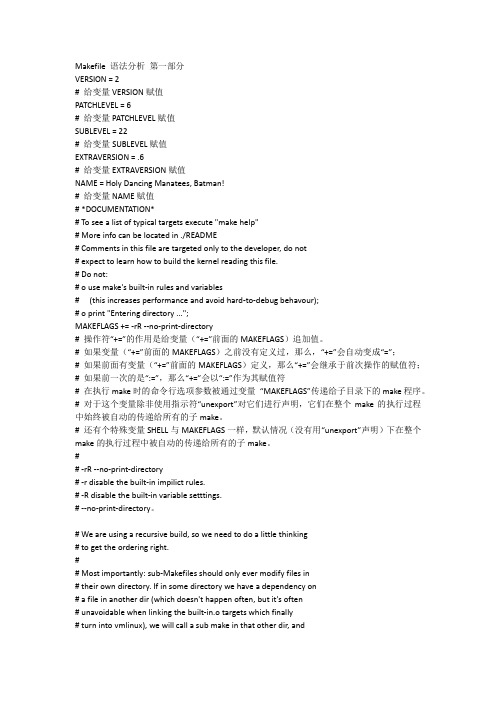

Makefile 语法分析

Makefile 语法分析第一部分VERSION = 2# 给变量VERSION赋值PATCHLEVEL = 6# 给变量PATCHLEVEL赋值SUBLEVEL = 22# 给变量SUBLEVEL赋值EXTRAVERSION = .6# 给变量EXTRAVERSION赋值NAME = Holy Dancing Manatees, Batman!# 给变量NAME赋值# *DOCUMENTATION*# To see a list of typical targets execute "make help"# More info can be located in ./README# Comments in this file are targeted only to the developer, do not# expect to learn how to build the kernel reading this file.# Do not:# o use make's built-in rules and variables# (this increases performance and avoid hard-to-debug behavour);# o print "Entering directory ...";MAKEFLAGS += -rR --no-print-directory# 操作符“+=”的作用是给变量(“+=”前面的MAKEFLAGS)追加值。

# 如果变量(“+=”前面的MAKEFLAGS)之前没有定义过,那么,“+=”会自动变成“=”;# 如果前面有变量(“+=”前面的MAKEFLAGS)定义,那么“+=”会继承于前次操作的赋值符;# 如果前一次的是“:=”,那么“+=”会以“:=”作为其赋值符# 在执行make时的命令行选项参数被通过变量“MAKEFLAGS”传递给子目录下的make程序。

驾驭makefile

This program built for i686-pc-cygwin

图 1.1

1.2 规则

Hello World 几乎是所有编程语言进行语言讲解时采用的一个最为简单的例子,虽然 Makefile 不是一个编程语言,但同样不防碍我们写一个在命令终端上输出“Hello World”的简单 Makefile。 采用一个文本编辑器编写一个如图 1.2 所示的 Makefile 文件,文件的存放目录可以是任意的。 Makefile all:

我们说 Makefile 中第一个很重要的概念就是目标(target), 图 1.2 所示的 Makefile 中的 all 就 是我们的目标,目标放在‘:’的前面,其名字可以是由字母和下划线‘_’组成。echo “Hello World” 就是生成目标的命令,这些命令可以是任何你可以在你的环境中运行的命令以及 make 所定义的函 数等等,后面我们会再细谈,现在只要知识 echo 是 BASH Shell 中的一个命令就行了,其功能是打 印字符串到终端上。all 目标在这里就是代表我们希望在终端上打印出“Hello World”,有时目标会 是一个比较抽象的概念。all 目标的定义,其实是定义了如何生成 all 目标,这我们也称之为规则, 即我们说图 1.2 的 Makefile 中定义了一个生成 all 目标的规则。

图 1.9

这里需要引入 Makefile 中依赖关系的概念,图 1.8 中 all 目标后面的 test 是告诉 make,all 目 标依赖 test 目标,这一依赖目标在 Makefile 中又被称之为先决条件。出现这种目标依赖关系时,make 工具会按从左到右的先后顺序先构建规则中所依赖的每一个目标。如果希望构建 all 目标不,那么 make 会在构建它之前得先构建 test 目标,这就是为什么我们称之为先决条件的原因。图 1.10 采用 UML 的类图表达了 all 目标的依赖关系。

python makefile 用法

python makefile 用法在使用Python编写程序时,我们通常需要编译和运行代码,这就需要用到makefile。

makefile是一种可以自动化地构建程序的工具,它可以根据代码修改的情况自动判断哪些文件需要重新编译,从而提高程序的编译效率。

使用makefile的基本步骤如下:1. 创建一个名为makefile的文件,通常放在程序的根目录下。

2. 在makefile中定义一些变量,如编译器、编译选项等。

3. 定义一些规则,如编译规则、目标规则等。

4. 运行make命令,根据makefile的规则进行编译和链接。

下面是一个简单的makefile示例:```# 定义编译器和编译选项CC=gccCFLAGS=-Wall -g# 定义编译规则%.o: %.c$(CC) $(CFLAGS) -c $< -o $@# 定义目标规则main: main.o sub.o$(CC) $(CFLAGS) main.o sub.o -o main# 清除中间文件clean:rm -f *.o main```在这个示例中,我们定义了两个变量CC和CFLAGS,分别表示编译器和编译选项。

接着定义了一个编译规则,表示将.c文件编译成.o文件的过程。

其中,$<表示依赖文件(即输入文件),$@表示目标文件(即输出文件)。

最后定义了一个目标规则,表示将main.o和sub.o链接成可执行文件main。

最后,我们定义了一个清除中间文件的规则,可以通过运行make clean来清除中间文件。

可以通过运行make命令来编译和链接程序。

例如,如果你有一个名为main.c和sub.c的源文件,并想将它们编译成可执行文件main,可以在终端中输入以下命令:```$ make main```这将根据makefile中定义的规则自动编译和链接程序,并生成可执行文件main。

总之,makefile是一个非常有用的编译工具,可以帮助我们自动化地构建程序,提高编译效率。

makefile -d 用法

makefile -d 用法摘要:1.Makefile 简介2.makefile -d 用法详解a.参数含义b.使用方法c.实例演示3.makefile -d 在实际项目中的应用4.总结正文:Makefile 是一个项目管理工具,主要用于自动化构建和编译软件项目。

在Makefile 中,我们可以定义一系列的规则,用于描述软件项目各文件的依赖关系以及编译命令等。

今天,我们将详细了解一下makefile -d 的用法。

1.Makefile 简介首先,让我们简要了解一下Makefile 的基本概念。

Makefile 是一个包含一系列命令和规则的文本文件,通常位于项目的根目录下。

它告诉make 命令如何自动构建、编译和链接项目。

2.makefile -d 用法详解接下来,我们将详细解释makefile -d 的参数含义、使用方法和实例演示。

a.参数含义-d 选项是makefile 的调试模式,它会在执行规则之前输出规则的详细信息,便于开发者调试和理解Makefile 的执行过程。

b.使用方法要使用makefile -d 选项,只需在调用make 命令时添加-d 参数即可,如下所示:```make -d```c.实例演示下面,我们通过一个简单的实例来演示如何使用makefile -d。

假设我们有一个名为`example.mk`的Makefile,其内容如下:```all: main.occ main.o -o mainmain.o: main.ccc main.c -o main.o```现在,我们使用make -d 命令来执行Makefile:```make -d```执行结果如下:```make: Entering directory `."main.mk:3: recipe for target "all"main.mk:3: cc main.o -o mainmake: Leaving directory `."```从输出结果中,我们可以看到makefile -d 选项输出了规则的详细信息。

Linux 内核配置机制(make menuconfig、Kconfig、makefile)讲解

printk(KERN_WARNING fmt, ##arg) printk(KERN_DEBUG fmt, ##arg)

/* Module Init & Exit function */ static int __init myModule_init(void) {

/* Module init code */ PRINTK("myModule_init\n"); return 0;

图形

工具

前面我们介绍模块编程的时候介绍了驱动进入内核有两种方式:模块和直接编译进内核,并介绍 了模块的一种编译方式——在一个独立的文件夹通过makefile配合内核源码路径完成

那么如何将驱动直接编译进内核呢? 在我们实际内核的移植配置过程中经常听说的内核裁剪又是怎么麽回事呢? 我们在进行linux内核配置的时候经常会执行make menuconfig这个命令,然后屏幕上会出现以下 界面:

首页 业界 移动 云计算 研发 论坛 博客 下载 更多

process的专栏

您还未登录!| 登录 | 注册 | 帮助

个人资料

dianhuiren

访问:71424次 积分:1219分 排名:第8764名 原创:37篇 转载:127篇 译文:0篇 评论:3条

目录视图

摘要视图

订阅

《这些年,我们读过的技术经典图书》主题有奖征文 经理

这些配置工具都是使用脚本语言,如 Tcl/TK、Perl 编写的(也包含一些用 C 编写的代码)。本文

/dianhuiren/article/details/6917132

1/5

2012年04月 (6) 2012年03月 (15) 2012年02月 (16)

并不是对配置系统本身进行分析,而是介绍如何使用配置系统。所以,除非是配置系统的维护者,一般 的内核开发者无须了解它们的原理,只需要知道如何编写 Makefile 和配置文件就可以。

makefile obj用法

文章标题:深入探讨Makefile中的Obj用法在软件开发中,Makefile是一个非常重要的工具,它帮助程序员管理项目的编译和信息过程。

而Makefile中的Obj用法则是Makefile中非常重要的一部分,它用来指定项目中的目标文件。

在本篇文章中,我们将深入探讨Makefile中的Obj用法,从简单到复杂,由浅入深,帮助读者更好地理解和运用Obj用法。

1. 什么是Makefile在开始深入探讨Makefile中的Obj用法之前,我们先来了解一下什么是Makefile。

Makefile是一种文件,其中包含了一系列规则和命令,用于指导编译器如何编译和信息项目中的源文件,最终生成可执行文件。

Makefile通过维护文件之间的依赖关系,可以使得在修改源文件后,只重新编译需要重新编译的文件,而不是整个项目。

这样可以提高编译的效率,特别是在大型项目中非常重要。

2. Obj用法的基础概念Obj用法是Makefile中用来指定目标文件的一个重要部分。

在Makefile中,通常通过指定目标文件来定义一个编译单元,Obj用法就是用来指定这些目标文件的。

在Makefile中,Obj用法通常是在规则中使用的,用来指定编译的目标文件是哪些。

我们可以这样定义一个规则:```main.o : main.cgcc -c main.c -o main.o```在这个例子中,main.o就是通过Obj用法指定的目标文件,它告诉Makefile需要生成名为main.o的目标文件,并且它是由main.c编译而来的。

3. Makefile中的Obj用法进阶除了简单地指定目标文件外,Obj用法还可以进一步扩展。

在实际开发中,一个目标文件可能由多个源文件编译而来,这时候就需要用到Obj用法的进阶用法了。

在Makefile中,我们可以使用通配符来指定一组目标文件,例如:```%.o : %.cgcc -c $< -o $@```这个规则中,%表示任意的文件名,$<表示依赖文件,$@表示目标文件。

MakeFile详解

引用其它的Makefile-实例

有这样几个Makefile:a.mk、b.mk、c.mk,还有 一个文件叫foo.make,以及一个变量$(bar),其 包含了e.mk和f.mk,那么,下面的语句: include foo.make *.mk $(bar) 等价于: include foo.make a.mk b.mk c.mk e.mk f.mk

在大多数时候,由于源文件太多,编译生成的中间目标文 件太多,而在链接时需要明显地指出中间目标文件名,这

对于编译很不方便,所以,通常要给中间目标文件打个包,

在Windows 下这种包叫“库文件”(Library File),也就 是 .lib 文件,在UNIX 下,是Archive File,也就是 .a 文件。

定义变量和引用变量

变量的定义和应用与Linux环境变量一样,变量名 要大写,变量一旦定义后,就可以通过将变量名 用圆括号括起来,并在前面加上“$”符号来进行 引用。 变量的主要作用: 1、保存文件名列表 2、保存可执行命令名,如编译器 3、保存编译器的参数 变量一般都在makefile的头部定义。按照惯例, 所有的makefile变量都应该是大写。

者,通常是你需要告诉编译器头文件的所在位置,只要所有的语法正

确,编译器就可以编译出中间目标文件。一般来说,每个源文件都应 该对应于一个中间目标文件(O 文件或是OBJ 文件)。

孙钦东

程序的编译和链接

链接时,主要是链接函数和全局变量。链接器并不管函数

所在的源文件,只管函数的中间目标文件(Object File)。

clean: -rm -f $(EXEC) *.elf *.gdb *.o

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Linux 2.6 (PC)简单驱动Makefile详解

ifneq ($(KERNELRELEASE),)

module-objs := book.o

obj-m := book.o

else

KERNELDIR ?= /lib/modules/$(shell uname -r)/build

PWD := $(shell pwd)

modules:

$(MAKE) -C $(KERNELDIR) M=$(PWD) modules

endif

clean:

rm -rf *.o *~core.depend.*.cmd *.ko *.mod.c.tmp versions

KERNELRELEASE 内核顶层目录Makefile的一个变量。

KERNELDIR ?= /lib/modules/$(shell uname -r)/build

内核源码树目录。

该Makefile 共读取两次,在输入Makefile时,$(KERNELDIR) 第一次读取KERNELRELEASE并没有被定义,然后就开始读取内核源码的目录,开始定义KERNELRELEASE,然后到当前模块的目录里面,M=$(PWD) 进入该Makefile时KERNELRELEAS已经被定义了,读取要编译的模块,然后再返回到modules

编译完成,产生.KO文件

Linux 2.6 (ARM)简单驱动Makefile详解

ifneq ($(KERNELRELEASE),)

obj-m := fgpio011.o

else

KDIR := /dsw/8126/arm-linux-2.6.28/linux-2.6.28-fa/

all:

make -C $(KDIR) M=$(PWD) modules ARCH=arm

CROSS_COMPILE=arm-none-linux-gnueabi-

clean:

rm -f *.ko *.o *.mod.o *.mod.c *.symvers

endif

注释:

KDIR := /dsw/8126/arm-linux-2.6.28/linux-2.6.28-fa/ KDIR 指定开发板内核所在目录。

CROSS_COMPILE=arm-none-linux-gnueabi- 指定编译器。

其它项目与PC机的一样。

驱动模块编译进内核。