以太网GMII介绍

以太网MII接口类型大全-MII、RMII、SMII、SSMII、SSSMII、GMII、RGMII、SGMII、TBI、RTBI、XGMII、XAUI、XL

MII是英文Medium Independent Interface的缩写,翻译成中文是“介质独立接口”,该接口一般应用于以太网硬件平台的MAC层和PHY层之间,MII接口的类型有很多,常用的有MII、RMII、SMII、SSMII、SSSMII、GMII、RGMII、SGMII、TBI、RTBI、XGMII、XAUI、XLAUI等。

下面对它们进行一一介绍。

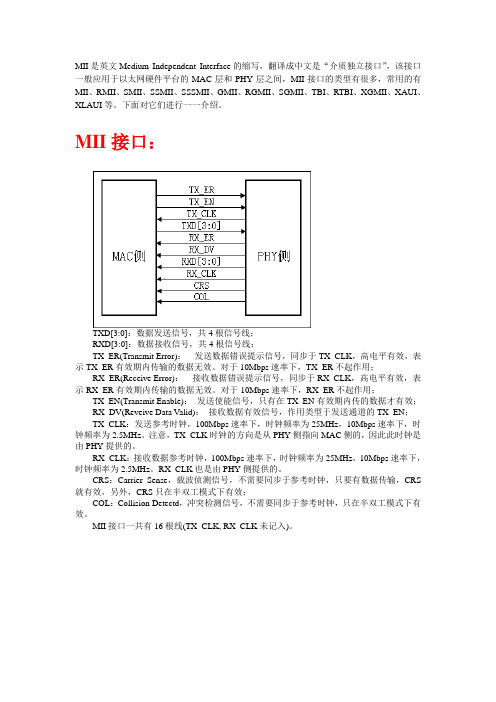

MII接口:TXD[3:0]:数据发送信号,共4根信号线;RXD[3:0]:数据接收信号,共4根信号线;TX_ER(Transmit Error):发送数据错误提示信号,同步于TX_CLK,高电平有效,表示TX_ER有效期内传输的数据无效。

对于10Mbps速率下,TX_ER不起作用;RX_ER(Receive Error):接收数据错误提示信号,同步于RX_CLK,高电平有效,表示RX_ER有效期内传输的数据无效。

对于10Mbps速率下,RX_ER不起作用;TX_EN(Transmit Enable):发送使能信号,只有在TX_EN有效期内传的数据才有效;RX_DV(Reveive Data Valid):接收数据有效信号,作用类型于发送通道的TX_EN;TX_CLK:发送参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。

注意,TX_CLK时钟的方向是从PHY侧指向MAC侧的,因此此时钟是由PHY提供的。

RX_CLK:接收数据参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。

RX_CLK也是由PHY侧提供的。

CRS:Carrier Sense,载波侦测信号,不需要同步于参考时钟,只要有数据传输,CRS 就有效,另外,CRS只在半双工模式下有效;COL:Collision Detectd,冲突检测信号,不需要同步于参考时钟,只在半双工模式下有效。

MII接口一共有16根线(TX_CLK, RX_CLK未记入)。

各种MII详解(MII,GMII,RGMII,RMII,SMII,SSMII,TBI,RTBI)

简介MII是英文Medium Independent Interface的缩写,翻译成中文是“介质独立接口”,该接口一般应用于以太网硬件平台的MAC层和PHY层之间,MII接口的类型有很多,常用的有MII、RMII、SMII、SSMII、SSSMII、GMII、RGMII、SGMII、TBI、RTBI、XGMII、XAUI、XLAUI等。

下面对它们进行一一介绍。

MII接口:T XD(Transmit Data)[3:0]:数据发送信号,共4根信号线;RXD(Receive Data)[3:0]:数据接收信号,共4根信号线;TX_ER(Transmit Error):发送数据错误提示信号,同步于TX_CLK,高电平有效,表示TX_ER有效期内传输的数据无效。

对于10Mbps速率下,TX_ER不起作用;RX_ER(Receive Error):接收数据错误提示信号,同步于RX_CLK,高电平有效,表示RX_ER有效期内传输的数据无效。

对于10Mbps速率下,RX_ER不起作用;TX_EN(Transmit Enable):发送使能信号,只有在TX_EN有效期内传的数据才有效;RX_DV(Reveive Data Valid):接收数据有效信号,作用类型于发送通道的TX_EN;TX_CLK:发送参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。

注意,TX_CLK时钟的方向是从PHY侧指向MAC侧的,因此此时钟是由PHY提供的。

RX_CLK:接收数据参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。

RX_CLK也是由PHY侧提供的。

CRS:Carrier Sense,载波侦测信号,不需要同步于参考时钟,只要有数据传输,CRS就有效,另外,CRS只有PHY在半双工模式下有效;COL:Collision Detectd,冲突检测信号,不需要同步于参考时钟,只有PHY在半双工模式下有效。

GMII_RGMII

以太网知识(3)-GMII / RGMII接口作者:luqiliang 日期:2010-5-11 13:24:45字体大小: 小中大本文主要分析MII/RMII/SMII,以及GMII/RGMII/SGMII接口的信号定义,及相关知识,同时本文也对RJ-45接口进行了总结,分析了在10/100模式下和1000M 模式下的连接方法。

4. GMII 接口分析GMII接口提供了8位数据通道,125MHz的时钟速率,从而1000Mbps的数据传输速率。

下图定义了RS层的输入输出信号以及STA的信号:图18 Reconciliation Sublayer (RS) and STA connections to GMII下面将详细介绍GMII接口的信号定义,时序特性等。

由于GMII接口有MAC和PHY模式,因此,将会根据这两种不同的模式进行分析,同时还会对RGMII/TBI/RTBI接口进行介绍。

4.1 GMII接口信号定义GMII接口可分为MAC模式和PHY模式,一般说来MAC和PHY对接,但是MAC和MAC也是可以对接的。

在GMII接口中,它是用8根数据线来传送数据的,这样在传送1000M数据时,时钟就会125MHz。

GMII接口主要包括四个部分。

一是从MAC层到物理层的发送数据接口,二是从物理层到MAC层的接收数据接口,三是从物理层到MAC层的状态指示信号,四是MAC层和物理层之间传送控制和状态信息的MDIO接口。

GMII接口的MAC模式定义:注意在表7中,信号GTX_CLK对于MAC来说,此时是Output信号,这一点和MII接口中的TX_CLK的Input特性不一致。

GMII接口PHY模式定义:表8注意在表8中,信号GTX_CLK对于PHY来说,此时是Input信号,这一点和MII接口中的TX_CLK的Output特性不一致。

4.2 GMII接口时序特性在GMII接口中,TX通道参考时钟是GTX_CLK,RX通道参考时钟是RX_CLK,802.3-2005定义了它们之间的关系。

usxgmii接口标准

usxgmii接口标准USXGMII(10G SerDes External Interface)是一种用于高速数据通信的接口标准,可以提供最高达10Gbps的数据传输速度。

它是由IEEE 802.3工作组制定的标准,旨在满足现代高带宽需求的应用。

USXGMII接口标准的主要目的是提供一个由物理层和数据链路层共同协作的接口规范,以实现高速数据传输。

它通常被用于千兆以太网或其他高速通信标准中,能够支持多种不同的应用场景。

USXGMII接口通过使用多个数据通道以及相应的控制信号,实现数据的传输和接收。

USXGMII接口标准的特点之一是它的高数据传输速度。

以千兆以太网为例,传统的千兆以太网使用MII(介质选择接口)和GMII(千兆介质选择接口)接口,其传输速度限制在1Gbps。

而USXGMII接口则可以提供高达10Gbps的数据传输速度,为现代高带宽应用提供了更高的性能。

此外,USXGMII接口标准还具有较低的功耗和复杂度。

由于其高速数据传输的特性,USXGMII接口在相对较低的功耗下可以实现更高的数据吞吐量。

同时,USXGMII接口本身的设计也相对简单,降低了实现的复杂性和成本,提高了应用的可扩展性和可组装性。

USXGMII接口标准是一个灵活且可定制的标准。

它提供了多种不同的通道配置选项,以适应不同的应用需求。

用户可以根据具体场景选择合适的通道配置,从而平衡数据传输速度、设计复杂度和成本等因素。

总的来说,USXGMII接口标准是一种用于高速数据通信的接口标准,具有高速数据传输、低功耗、低复杂度和灵活性等特点。

它为现代高带宽应用提供了更高的性能和可靠性。

随着数据传输需求的不断增加,USXGMII接口标准将在各种领域中得到广泛应用。

MII,GMII,RMII介绍

MII (Media Independent Interface(介质无关接口)或称为媒体独立接口,它是IEEE-802.3定义的以太网行业标准。

它包括一个数据接口和一个MAC和PHY之间的管理接口。

数据接口包括分别用于发送器和接收器的两条独立信道,每条信道都有自己的数据、时钟和控制信号。

MII数据接口总共需要16个信号。

管理接口是个双信号接口:一个是时钟信号,另一个是数据信号。

通过管理接口,上层能监视和控制PHY。

MII (Management interface)只有两条信号线。

MII标准接口用于连接Fast Ethernet MAC-block与PHY。

表明在不对MAC硬件重新设计或替换的情况下,任何类型的PHY设备都可以正常工作。

在其他速率下工作的与MII等效的接口有:AUI(10M以太网)、GMII(Gigabit以太网)和XAUI(10-Gigabit以太网)。

MII总线在IEEE802.3中规定的MII总线是一种用于将不同类型的PHY与相同网络控制器(MAC)相连接的通用总线。

网络控制器可以用同样的硬件接口与任何PHY进行连接。

MII相关接口介绍:以太网媒体接口有:MII RMII SMII GMII所有的这些接口都从MII而来,MII是(Medium Independent Interface)的意思,是指不用考虑媒体是铜轴、光纤、电缆等,因为这些媒体处理的相关工作都有PHY或者叫做MAC 的芯片完成。

MII支持10兆和100兆的操作,一个接口由14根线组成,它的支持还是比较灵活的,但是有一个缺点是因为它一个端口用的信号线太多,如果一个8端口的交换机要用到112根线,16端口就要用到224根线,到32端口的话就要用到448根线,一般按照这个接口做交换机,是不太现实的,所以现代的交换机的制作都会用到其它的一些从MII简化出来的标准,比如RMII、SMII、GMII等。

RMII是简化的MII接口,在数据的收发上它比MII接口少了一倍的信号线,所以它一般要求是50兆的总线时钟。

通信协议——MIIGMII

通信协议——MIIGMII协议名称:MIIGMII通信协议一、引言MIIGMII通信协议是一种用于数据通信的标准协议,旨在提供高效、可靠的数据传输。

本协议适用于各种通信设备和网络,包括以太网、无线网络等。

MIIGMII 通信协议的设计目标是保证数据的完整性、可靠性和安全性,同时提供灵活性和可扩展性。

二、术语和定义在本协议中,以下术语和定义适用:1. MIIGMII:Media Independent Interface-Gigabit Media Independent Interface,即媒体独立接口-千兆媒体独立接口。

2. 数据帧:在MIIGMII通信中,数据以帧的形式进行传输,包括数据头、数据体和校验字段。

3. 发送端:指数据传输的发起方。

4. 接收端:指数据传输的接收方。

5. PHY:物理层,负责将数据从逻辑层转换为物理信号进行传输。

6. MAC:介质访问控制层,负责数据的编码、解码和传输控制。

三、协议规范1. 数据帧格式MIIGMII通信协议的数据帧由以下字段组成:- 帧起始标志:用于表示帧的开始,由一个特定的比特序列组成。

- 目的MAC地址:指示帧的接收方MAC地址。

- 源MAC地址:指示帧的发送方MAC地址。

- 类型/长度字段:指示数据帧的类型或长度。

- 数据字段:包含要传输的数据。

- 校验字段:用于校验数据的完整性。

2. 数据传输流程MIIGMII通信协议的数据传输流程如下:- 发送端将数据封装成数据帧,并添加帧起始标志、目的MAC地址、源MAC地址、类型/长度字段、数据字段和校验字段。

- 发送端将数据帧通过PHY层转换为物理信号,并通过传输介质发送到接收端。

- 接收端通过PHY层将物理信号转换为数据帧。

- 接收端根据目的MAC地址判断是否接收该数据帧,如果是则进行数据解析和处理,否则丢弃该数据帧。

3. 数据校验MIIGMII通信协议使用CRC(循环冗余校验)算法对数据进行校验,以确保数据的完整性。

gmii波形

Gigabit Media Independent Interface (GMII)是一种千兆位媒体独立接口,它使用8位接口数据,工作时钟为125MHz,因此传输速率可以达到1000Mbps。

以下是GMI波形的一些基本特性:

1. GMII接口数据结构符合IEEE以太网标准,其信号定义可以在IEEE 80

2.3-2000标准中找到。

2. GMII采用同步模式,发送端在SYNC信号变高后的10个时钟周期内,TXD依次输出一组10bit的数据,包括TX_ER、TX_EN和TXD[0:7]。

这些控制信息与MII接口的含义相同。

3. 在100M速率下,每一组数据的内容都是变化的。

而在10M 速率下,每一组数据需要重复10次,采样任意一组都可以。

希望以上信息对您有帮助。

如果您想了解更多关于GMI波形的信息,建议您查阅相关的专业资料或咨询相关专家。

以太网MII接口类型大全-MII、RMII、SMII、SSMII、SSSMII、GMII、RGMII、SGMII、TBI、RTBI、XGMII、XAUI、XL

以太网MII接口类型大全-MII、RMII、SMII、SSMII、SSSMII、GMII、RGMII、SGMII、TBI、RTBI、XGMII、XAUI、XLMII是英文Medium Independent Interface 的缩写,翻译成中文是“介质独立接口”,该接口一般应用于以太网硬件平台的MAC层和PHY层之间,MII接口的类型有很多,常用的有MII、RMII、SMII、SSMII、SSSMII、GMII、RGMII、SGMII、TBI、RTBI、XGMII、XAUI、XLAUI等。

下面对它们进行一一介绍。

MII接口:TXD[3:0]:数据发送信号,共4根信号线;RXD[3:0]:数据接收信号,共4根信号线;TX_ER(Transmit Error):发送数据错误提示信号,同步于TX_CLK,高电平有效,表示TX_ER有效期内传输的数据无效。

对于10Mbps速率下,TX_ER不起作用;RX_ER(Receive Error):接收数据错误提示信号,同步于RX_CLK,高电平有效,表示RX_ER有效期内传输的数据无效。

对于10Mbps速率下,RX_ER不起作用;TX_EN(Transmit Enable):发送使能信号,只有在TX_EN有效期内传的数据才有效;RX_DV(Reveive Data Valid):接收数据有效信号,作用类型于发送通道的TX_EN;TX_CLK:发送参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。

注意,TX_CLK时钟的方向是从PHY侧指向MAC侧的,因此此时钟是由PHY提供的。

RX_CLK:接收数据参考时钟,100Mbps 速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。

RX_CLK也是由PHY侧提供的。

CRS:Carrier Sense,载波侦测信号,不需要同步于参考时钟,只要有数据传输,CRS就有效,另外,CRS只在半双工模式下有效;COL:Collision Detectd,冲突检测信号,不需要同步于参考时钟,只在半双工模式下有效。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

以太网知识GMII / RGMII接口本文主要分析MII/RMII/SMII,以及GMII/RGMII/SGMII接口的信号定义,及相关知识,同时本文也对RJ-45接口进行了总结,分析了在10/100模式下和1000M模式下的连接方法。

1. GMII 接口分析GMII接口提供了8位数据通道,125MHz的时钟速率,从而1000Mbps的数据传输速率。

下图定义了RS层的输入输出信号以及STA的信号:图18 Reconciliation Sublayer (RS) and STA connections to GMII下面将详细介绍GMII接口的信号定义,时序特性等。

由于GMII接口有MAC和PHY模式,因此,将会根据这两种不同的模式进行分析,同时还会对RGMII/TBI/RTBI接口进行介绍。

4.1 GMII接口信号定义GMII接口可分为MAC模式和PHY模式,一般说来MAC和PHY对接,但是MAC和MAC也是可以对接的。

在GMII接口中,它是用8根数据线来传送数据的,这样在传送1000M数据时,时钟就会125MHz。

GMII接口主要包括四个部分。

一是从MAC层到物理层的发送数据接口,二是从物理层到MAC层的接收数据接口,三是从物理层到MAC层的状态指示信号,四是MAC层和物理层之间传送控制和状态信息的MDIO接口。

GMII接口的MAC模式定义:注意在表7中,信号GTX_CLK对于MAC来说,此时是Output信号,这一点和MII接口中的TX_CLK的Input特性不一致。

GMII接口PHY模式定义:表8注意在表8中,信号GTX_CLK对于PHY来说,此时是Input信号,这一点和MII接口中的TX_CLK的Output特性不一致。

4.2 GMII接口时序特性在GMII接口中,TX通道参考时钟是GTX_CLK,RX通道参考时钟是RX_CLK,802.3-2005定义了它们之间的关系。

图19 GMII signal timing at receiver input由图19可知,Spec只定义了TX通道和RX通道中接收端Setup时间和Hold时间。

很明显,即该Spec只对TX通道上PHY这一侧的接收特性作了定义,而对TX通道MAC 那一侧的发送特性并没有定义。

IC Vendor可在TX通道那一侧的MAC的发送特性作适当调整,只要最终的时序满足TX通道上PHY这一侧的接收特性就可以。

同样的道理,该Spec只对RX通道上MAC这一侧的接收特性作了定义,而对RX通道PHY那一侧的发送特性并没有定义。

IC Vendor可在RX通道那一侧的PHY的发送特性作适当调整,只要最终的时序满足RX通道上MAC这一侧的接收特性就可以。

图20 Setup和Hold Time的值从图20可以看出,这里有两组setup和hold时间。

其中第一组Spec则是根据图21给定的测试电路定义的,即该Spec未考虑PCB上传输线的不匹配等影响。

而第二组Spec则是定义了receiver at its input pins的时间要求,它考虑了PCB上传输线的长度不匹配等影响。

一般IC Vendor需要按照第二组Spec来设计它们的IC。

(Two sets of setup and hold time parameters are specified in Fig. 20. The first set, tSETUP and tHOLD, applies to the source of a synchronous GMII signal and its clock and is measured using the “GMII Setup and Hold Time Test Circuit,” which has transmission lines with matched propagation delays in the “clock” and“signal” paths. The second set, tSETUP(RCVR) and tHOLD(RCVR), applies to the GMII receiver and specifies the minimum setup and hold times available to the GMII receiver at its input pins. The difference between the two sets of setup and hold time parameters provides margin for asmall amount of mismatch in the propagation delays of the “clock” path and the “signal” paths in GMII applications)。

图21 GMII接口Setup和Hold Time测试电路4.3 GMII信号功能特性:<1>:GTX_CLK (transmit clock),GTX_CLK (Transmit Clock)是一个连续的时钟信号(即系统启动,该信号就一直存在),它是TX_EN, TXD, and TX_ER(信号方向为从RS到PHY)的参考时钟,PHY端在信号的上升沿采样,GTX_CLK由MAC驱动。

GTX_CLK的时钟频率是数据传输速率的12.5,即125MHz。

<2>:对于同样的RX_CLK,它与TX_CLK具有相同的要求,所不同的是它是RX_DV, RXD, and RX_ER(信号方向是从PHY到RS)的参考时钟,MAC端在时钟的上升沿采样。

RX_CLK是由PHY驱动,PHY可能从接收到的数据中提取时钟RX_CLK,也有可能从一个名义上的参考时钟(e.g., the TX_CLK reference)来驱动RX_CLK<3>:GMII接口的发送时序如图22所示,接收时序如图23所示,至于其它信号的功能特性以及在数据传输过程中,不同信号的逻辑变化所代表的意义,这里不再描述,大体上和“MII信号功能特性”一节中描述类似,读者可以参阅802.3-3005的Spec。

图22 GMII信号发送时序图23 GMII信号接收时序4.4 GMII的管理MDIO接口:关于GMII的管理MDIO接口,这里也不再描述,它在硬件设计上同MII的管理MDIO 接口一节的描述。

4.5 Electrical CharacterG MII接口的电气特性可以分为DC characteristics和AC characteristics。

针对于DC电气特性而言,All GMII drivers and receivers shall comply with the dc parametric attributes specified in Table 35–7. The potential applied to the input of a GMII receiver may exceed the potential of the receiver’s power supply (i.e., a GMII driver powered from a 3.6 V supply driving VOH into a GMII receiver powered from a 2.5 V supply). Tolerance for dissimilar GMII driver and receiver supply potentials is implicit in these specifications.针对于AC电气特性而言,The GMII ac electrical characteristics are specified in a manner that allows the implementor flexibility in selecting the GMII topologies its devices support and the techniques used to achieve the specified characteristics.All GMII devices are required to support point-to-point links. The electrical length of the circuit board traces used to implement these links can be long enough to exhibit transmission line effects and require some form of termination. The implementor is allowed the flexibility to select the driver output characteristics and the terminationtechnique and components to be used with its drivers for point-to-point links. Implementors may elect to support other GMII topologies in addition to the point-to-point topology and may specify different termination techniques and components for each supported topology.Since the output characteristics and output voltage waveforms of GMII drivers depend on the termination technique and the location of the termination components, the ac output characteristics of GMII drivers are not explicitly specified. Rather, the ac characteristics of the signal delivered to a GMII receiver are specified. These characteristics are independent of the topology and termination technique and apply uniformly to all GMII applications.5. RGMII接口分析5.1 RGMII接口信号定义:RGMII接口(Reduced GMII接口)是简化的GMII接口。