4级m序列发生器设计参考

m序列发生器设计实现

河南师范大学设计性实验报告学期:2014-2015学年第 1 学期m序列发生器设计实现_实验实验小组成员:班级:2013级网络工程班学院:计算机与信息工程学院填表日期: 2014年 11月 29 日实验项目简介:1 问题描述通常产生伪随机序列的数字电路为一反馈移位寄存器。

根据其构成结构,它又分为线性反馈移位寄存器和非线性反馈移位寄存器两类,由线性反馈移位寄存器产生的周期最长的二进制数字序列称为最大长度线性反馈移位寄存器序列,简称m序列。

2.实验原理:此实验是用4位移位寄存器实现可控乘/除法2到8步长为2n电路通过分析不难看出本次实验的乘除法运算中一个只出现三个数字2、4、8写成二进制为0010、0100、1000可以发现每一次乘法都只是将1向左移一个位每一次除法则是向右移一位,那么就可以使用74194双向移位寄存器。

首先要了解4位移位寄存器。

工作原理:74194是一个4位双向移位寄存器。

它具有左移、右移、并行输入数据、保持以及清除等五种功能:当~R=1MA MB=00MA MB=01MA MB=10MA MB=113.一个完整的系统应具有以下功能:1)控制信号的移动方向,通过改变S1S0的编码状态,使移位器左移、右移、保持等。

2)可以得到m序列的周期,通过观察示波器中CLK与Sl或者Sr的波形,可以得出m序列的周期。

4.实验目的:1、掌握M序列信号产生的基本方法2、利用EWB产生M序列信号,设计电路做成M序列信号发5.实验条件:学院提供公共机房,1台/学生微型计算机。

实验总结:1.在实验的过程中,小组成员积极准备。

通过实验加深了对74194芯片性能的了解,提高了各个成员的动手能力。

2.但是由于知识掌握不够全面准确的原因,实验过程中多次出现问题,小组成员积极思考,最终解决了问题。

3.在观察m序列周期的过程中,出现了周期同预期不符合的情况,最终发现是输入脉冲时出现了问题。

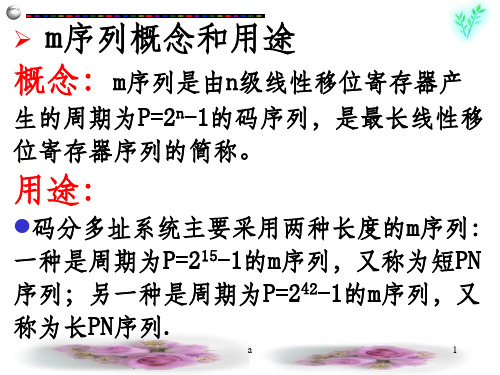

m序列

a

12

游程数目

游程长 “1”

“0”

度/比特

xij

R(j)

1P Pi1

xi

xij

1, j 0 1, j 0

a

P

15

R()

R(j) 1 1

P

P

12 3

P

0

T0

j

当P足够大,收发同步时,接收端输出就是峰值.

a

16

➢ m序列的构造——反馈线性反馈移存器

an

c0 1 an1

c1

c2

an2

a1

.cn1 a0

.cn 1

输

特征多项式:Ci代表反馈连接的值,c0,cna19x4 来自1x. a 3

x2

a2

x3

a1

1 0 0 0

1

1

0

0

1 1 1 0

1

1

1

1

0 1 1 1

1

0

1

1

0 1

1 0

0 1

1 0

24 1 15

1

1

0

1

0 1 1 0

0

0

1

1

1

0

0

1

0

1

0

0

0

0

1

0

0

0

0

1

1

0

0

0

基于FPGA的M序列的设计与实现_冀勇钢

参考文献

ቤተ መጻሕፍቲ ባይዱ

[1] Application Using the TMS320C6000 Enhanced DMA . TI,2001.

66

2007.9 www.ecda.cn

!!!!!!!!!!!!!"

!!!!!!!!!!!!!!!!!!!!"

[2] TMS320C6000 Optimizing Compiler User’s Guide .TI , 2001.

0 引言

扩频通信系统与传统通信系统的区别在于其 利用伪随机序列来实现扩频与解扩步骤。而伪随 机序列作为扩频通信系统的关键, 将直接影响到 系统的性能。

信息论的奠基人香农提出的编码定理指出: 只要信息速率Rb小于信道容量C, 那么, 就总 可 以找到某种编码方法, 在码周期相当长的条件 下, 几乎无差错的从受到高斯噪声干扰的信号中 复制出原来发送的信息。这里有两个条件: 一是 Rb小 于C, 二 是 编 码 的 码 长 周 期 足 够 长 。 同 时 , 香农在证明编码定理的时候, 也提出了使用具有 白噪声统计特性的信号来编码。

[3] 江 思 敏 、刘 畅.TMS320C6000DSP应 用 开 发 教 程[M].北 京: 机械工业出版社, 2005.

!!!!!!!!!!!!!!!!!!!!"

本刊启事

为适应我国信息化建设, 扩大本刊及作 者知识信息交流渠道, 本刊已被CNKI中国期 刊全文数据库网络出版, 其作者著作权使用 费与本刊发表费用一次性处理。如作者不同 意文章被收录, 请在来稿时向本刊声明, 本 刊将做适当处理。

行仿真, 本例程在QuartusII下得到的寄存器传输 级电路图和仿真波形如图5所示。

3 结束语

m序列发生器的设计与实现

2 0 年 6月 07

J n 20 u .0 7

m序列发生器的设计与实现

王会华 , 李宝平

( 南京邮电大学 无线通信与电磁兼容实验 室, 江苏 , , 1 0 3) 南京 2 0 0

摘 要: 随机码越 来越受到人们 的重视 , 广泛应 用于导弹、 伪 被 卫星、 飞船轨道 测量和跟踪 、 雷达、 导航 、 移

计 想法 。

关键词 : 随机码 ; 序列 ; 伪 m 移位寄存器 ; ; 仿真 移动通信

中图分类号 : N 1 . T 9 7 1 文献标识码 : A 文章编号 :6 2 4 4 (0 7 2 0 5 — 4 17 — 6 X2 0 ) —0 80 0

De in a d Re l eo lS q e c n r t r sg n ai fn e u n e Ge e a o z

WAN H il , B n G u-ma ∞ g

( b rtr o rl sC mm n ai n MC N nn n esyo ot a d L oaoy f e s o u i t na dE a jgU i rt f s n a Wi e c o i v i P s TI o e c mmu i f n a jg 20 0 ) e n ai sN nn , 10 3 c o i

0引 言

伪 随机码【 又称伪 随机序 列 , 1 】 , 是一种可 以预先确定并 可以重复地产生和复制 ,又具有 随机统计特性 的二进制码

s q e c . a e a r u e h r wae d s i u t 1 一 e e s q e c . u h r o e t i p p r e u n e L tr we c ry o t h a d r e i cr i 3 lv l t n g c s m e u ne F r e t m r s a e h

序列信号发生器的设计方法及应用实例

序列信号发生器的设计方法及应用实例在现代通信系统中,序列信号发生器是一个非常重要的设备,它能够产生各种类型的信号序列,如随机序列、伪随机序列、码片序列等。

这些信号序列在数字通信系统、脉冲调制系统以及其他通信系统中起着至关重要的作用。

在本文中,我将深入探讨序列信号发生器的设计方法及其应用实例,并共享一些个人观点和理解。

1. 序列信号发生器的基本原理序列信号发生器是一种能够产生特定类型的信号序列的设备。

其基本原理是利用特定的算法和逻辑电路来产生所需的信号序列。

在设计序列信号发生器时,首先需要确定所需的信号类型,如随机序列、伪随机序列或者其他类型的序列。

然后根据所选的信号类型,选择合适的算法和电路来实现信号的生成。

最常见的序列信号发生器包括线性反馈移位寄存器(LFSR)、差分方程序列发生器等。

2. 序列信号发生器的设计方法在设计序列信号发生器时,需要考虑信号的周期、自相关性、互相关性等性能指标。

一般来说,设计序列信号发生器的方法可以分为以下几个步骤:(1)确定信号类型:首先需要确定所需的信号类型,如随机序列、伪随机序列或者其他类型的序列。

(2)选择算法和电路:根据所选的信号类型,选择合适的算法和电路来实现信号的生成。

常用的算法包括线性反馈移位寄存器、差分方程序列发生器等。

(3)优化性能指标:优化信号的周期、自相关性、互相关性等性能指标,以确保生成的序列满足系统的要求。

(4)验证和测试:设计完成后,需要对信号发生器进行验证和测试,确保其生成的信号符合设计要求。

3. 序列信号发生器的应用实例序列信号发生器在数字通信系统、脉冲调制系统以及其他通信系统中有着广泛的应用。

以下是一些典型的应用实例:(1)伪随机噪声序列发生器:在数字通信系统中,伪随机噪声序列被广泛用于信道编码、扩频通信以及通信安全等领域。

(2)码片序列发生器:在脉冲调制系统中,码片序列被用于直序扩频通信系统中的扩频码生成。

(3)随机序列发生器:在通信加密领域,随机序列被用于数据加密和解密。

4阶m序列密码

4阶M序列(Maximum-length sequence)是一种由4级线性反馈移位寄存器(LFSR)生成的伪随机序列。

这种序列具有良好的周期性和伪随机特性,因此在密码学中常被用作流密码或者序列密码的密钥流生成器。

一个4阶M序列的生成通常涉及以下步骤:

1. 定义LFSR:

- 选择一个4位的线性反馈移位寄存器,每个寄存器位可以是0或1。

- 确定反馈连接,即哪些寄存器位的输出将反馈到输入以更新寄存器状态。

2. 设定初始状态:

- 为寄存器设定一个初始状态,通常是4位的二进制数。

3. 执行移位和反馈操作:

- 每个时钟周期,最右边的寄存器位(通常称为“输出位”)被移出并作为M序列的一个元素。

- 同时,根据反馈连接规则,一些寄存器位的异或结果(XOR)被反馈到寄存器的左侧,更新寄存器状态。

4. 生成M序列:

- 重复移位和反馈操作,生成无限长的二进制序列。

对于4阶M序列,其周期最长为2^4-1 = 15。

在密码学应用中,4阶M序列可能会与其他技术结合使用以增强安全性,例如通过异或操作将明文与M序列的元素进行组合来加密数据。

然而,直接使用M序列作为密钥流可能存在安全风险,因为较长的连续密文段可能暴露LFSR 的状态和反馈连接,使得攻击者能够恢复密钥或预测未来的密钥流。

因此,在实际应用中,通常会采用更复杂的流密码设计,如使用非线性组合

函数、多个LFSR的级联或者密钥流的扰动等技术来提高密码系统的安全性。

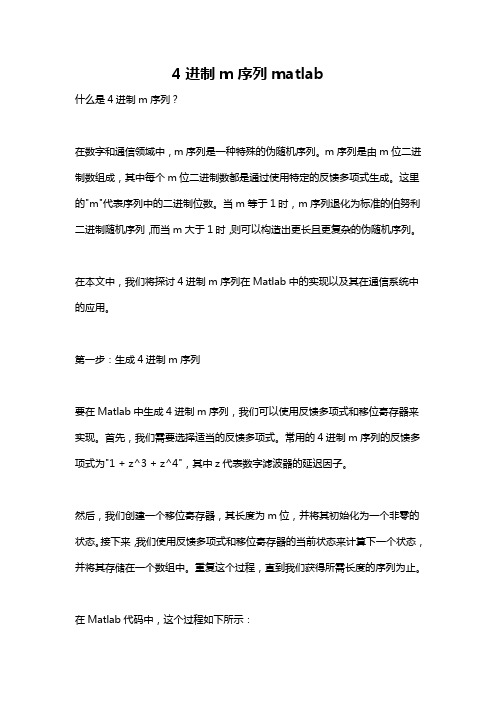

4进制m序列matlab

4进制m序列matlab什么是4进制m序列?在数字和通信领域中,m序列是一种特殊的伪随机序列。

m序列是由m位二进制数组成,其中每个m位二进制数都是通过使用特定的反馈多项式生成。

这里的"m"代表序列中的二进制位数。

当m等于1时,m序列退化为标准的伯努利二进制随机序列,而当m大于1时,则可以构造出更长且更复杂的伪随机序列。

在本文中,我们将探讨4进制m序列在Matlab中的实现以及其在通信系统中的应用。

第一步:生成4进制m序列要在Matlab中生成4进制m序列,我们可以使用反馈多项式和移位寄存器来实现。

首先,我们需要选择适当的反馈多项式。

常用的4进制m序列的反馈多项式为"1 + z^3 + z^4",其中z代表数字滤波器的延迟因子。

然后,我们创建一个移位寄存器,其长度为m位,并将其初始化为一个非零的状态。

接下来,我们使用反馈多项式和移位寄存器的当前状态来计算下一个状态,并将其存储在一个数组中。

重复这个过程,直到我们获得所需长度的序列为止。

在Matlab代码中,这个过程如下所示:matlabfunction sequence = generate_m_sequence(m, length)feedback_polynomial = [1, 0, 0, 0, 1]; % Feedback polynomial: 1 +z^3 + z^4shift_register = [1, 1, 1, 1]; % Initial state of shift registersequence = zeros(1, length); % Initialize sequence arrayfor i = 1:lengthsequence(i) = shift_register(1); % Store current state in sequence arrayfeedback_bit = mod(sum(shift_register .* feedback_polynomial), 2); % Calculate feedback bitshift_register = circshift(shift_register.', -1).'; % Shift register to the leftshift_register(end) = feedback_bit; % Update last bit with feedback bitendend通过调用上述函数,我们可以生成4进制m序列。

M序列发生器设计实验指导书

M序列发生器设计实验一、实验原理:M序列码也称伪随机序列码,其主要特点是:(1)每个周期中,“1”码出现2n-1次,“0”码出现2n-1次,即0、1出现概率几乎相等。

(2)序列中连1的数目是n,连0的数目是n-1。

(3)分布无规律,具有与白噪声相似的伪随机特性。

由于具有这些特点,m序列码在通信、雷达、系统可靠性测试等方面获得了广泛地应用。

m序列码发生器是一种反馈移位型结构的电路,它由n位移位寄存器加异或反馈网络组成,其序列长度M=2n-1,只有一个多余状态即全0状态,所以称为最大线性序列码发生器。

由于其结构已定型,且反馈函数和连接形式都有一定的规律,因此利用查表的方式就设计出m 序列码。

列出部分m序列码的反馈函数F和移存器位数n的对应关系。

如果给定一个序列信号长度M,则根据M=2n-1求出n,由n查表便可以得到相应的反馈函数F。

二、基于DSP Builder 的设计M 序列发生器可由线性反馈寄存器(Linear Feedback Shift Registers,LFSR )来产生,如图1所示。

图1 线性反馈移位寄存器的构成其特征多项式可表示为:∑==ni i i x C x F 1)(在图1中涉及的乘法和加法都是指模二运算的乘法和加法,即逻辑与和逻辑或。

要产生最长的线性反馈移位寄存器序列的n 级移位寄存器,其特征多项式必须是n 次本原多项式。

例如n=5,可以生成M 序列的5级LFSR 的特征多项式,即:125++x x ,此式可生成的M 序列的周期为:125-。

下面以M 序列发生器模型125++x x 为例,利用DSP Builder 构建一个伪随机序列发生器。

图2显示了上式的DSP Builder 模型表述,这里采用相连的延时单元级作为移位寄存器,用异或(XOR )完成模二加运算,输出为Output 。

图2 M 序列发生器模型但应注意,图2所示的电路一般无法正常工作。

这是由于在DSP Builder 默认的延时单元在开始工作时,存储内容为0,而对于M 序列来说,起始序列为全0,那么根据多项式,输出序列也将为0.全0序列不是正常的M 序列。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3级m序列发生器设计方案

图2.2 七位反馈移位移存器

方案一:

根据图2.2的结构模型,对于级数为n=3的m序列,可设置四个寄存器,将寄存器0和寄存器1进行异或运算,把结果赋给寄存器3。

然后将寄存器2,1,0右移一位。

再将寄存器3赋给寄存器2。

这样就不会产生数据覆盖。

最后把寄存器0输出。

同理可得15位m序列,级数n=4的verilog建模思路。

方案二:

由于7位m序列1110010可用三位二进制7种状态表示,因此可用Moore有限状态机的行为进行建模方法。

Moore有限状态机,其输出值只取决于当前状态,与输入值无关。

可以通过在always语句块内使用case语句来实现,在每个case分支都应当有输出值及状态转换。

设状态A=3'b111,B=3'b011,C=3'b001,D=3'b100,E=3'b010,F=3'b101,G=3'b110;它们的转换关系图如图2.3:

图 2.3 m序列发生器的状态转移图

方案一的程序比方案二简洁,方案二的思路比方案一更明白。

二者的各有千秋。

4级m序列及其Manchester编码

module manchester_encodingnew(enc_data,m_test,clk);

parameter BYTE_WIDTH=8;

input clk;

output enc_data;

output m_test;

reg phase;

reg busy;

wire clkr;

wire enc_data;

reg [2:0] bit_count;

reg reg_data;

reg Data_CLKT,Buff;

reg [3:0]m_Buff;

assign clkr=clk;

initial

begin

Data_CLKT=0;

busy=0;

phase=0;

bit_count=0;

end

always@(posedge clkr)

begin

Data_CLKT=~Data_CLKT;

end

always@ (posedge clkr)

begin

phase=~phase;

end

always@ (posedge clkr)

begin

if((bit_count==BYTE_WIDTH-1)&&phase)

busy=0;

else

busy=1;

end

always@(posedge clkr)

begin

if(phase&&busy)

bit_count=bit_count+1;

end

always@ (posedge clkr)

begin

if(phase&&busy)

begin

Buff=m_Buff[1]^m_Buff[0]^(m_Buff==0);

m_Buff[0]=m_Buff[1];

m_Buff[1]=m_Buff[2];

m_Buff[2]=m_Buff[3];

m_Buff[3]=Buff;

end

end

always@ (posedge clkr)

begin

reg_data=m_Buff[0];

end

assign m_test=reg_data;

assign enc_data=reg_data^~phase;

endmodule。