数字版图流程与工具1

20120523-数模混合电路设计流程

数模混合电路设计流程马昭鑫 2012/5/23本文主要面向模拟电路设计者,讲解了从行为级代码形式的数字电路到数模混合版图之间的流程,默认模拟版图和数字电路的行为级代码、testbench已经完成。

阅读者需确定自己会编写Verilog或Spice格式的网表,熟悉Linux的文件操作,了解Spectre、Virtuoso、Calibre、Modelsim、Design Compiler(dc)、Astro等EDA工具的使用方法。

由于本人才疏学浅,经验不足,难免会在文中出现一些错误,恳请高手给予指正。

数模混合电路的仿真方法一般的设计流程中数字电路和模拟电路是分开进行设计的,但有些时候希望能将数字电路和模拟电路放在一起仿真来验证设计,这就需要用到混合电路的仿真方法。

在Cadence 工具中有专门用作混合电路仿真的仿真器spectreVerilog,其实现方法是首先将模拟模块与数字模块区分开并设置接口电平,然后在ADE中设置数字电路的测试代码,调用不同的仿真器分别对数字模块和模拟模块进行仿真,最后将结果汇总显示或输出。

下面将以一个简单实例的形式讲解混合电路的仿真方法。

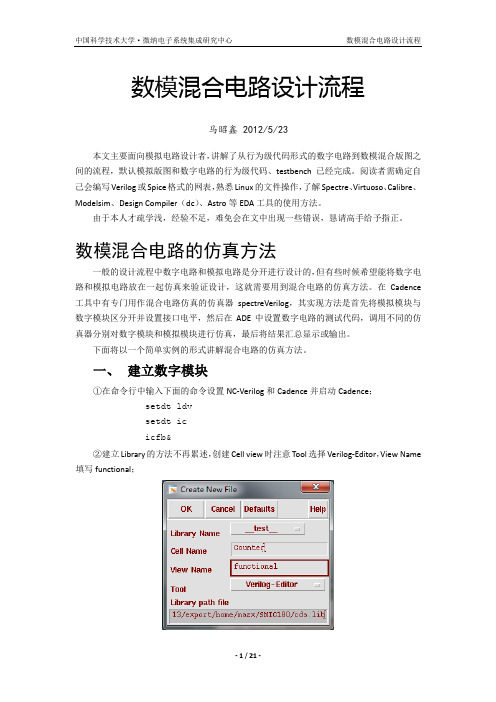

一、建立数字模块①在命令行中输入下面的命令设置NC-Verilog和Cadence并启动Cadence;setdt ldvsetdt icicfb&②建立Library的方法不再累述,创建Cell view时注意Tool选择Verilog-Editor,View Name 填写functional;③点击OK后会弹出有模块代码框架的vi窗口,将设计需要的代码输入或粘贴进去;④保存并关闭后如果没有错误会弹出创建Symbol View的询问对话框,确定后会进入Symbol编辑器,并自动生成了Symbol(注意在Cadence中总线用尖括号<>表示);⑤保存并关闭Symbol编辑器。

至此已经完成了数字模块的创建。

二、建立模拟模块模拟电路的创建方法无需赘述,这里搭建了一个输出频率为10MHz的环形振荡器。

Cadence工具版图设计

输出域

菜单栏

Log文件

窗口号

输入域 命令提示行

鼠标按纽提示

Cadence文件目录

• 在CIW中,打开Tools中的Library Manager。

三个层次: Library:库,可理解为Project,

每项工程有独立的Lib。 Cell:单元,库的基本组成元素,

单元之间可以相互使用。 View:视图,单元的各种表达形式

• 系统环境

• 工作站 • unix-based 工作环境 • VM-Ware虚拟机工作环境

工作站/Unix/Linux使用入门

• 基本指令简介: • ls:查看目录下所有文件。 • clear:清除屏幕。 • pwd:显示当前工作目录 。 • cd:改变目录 。 • rm:删除文件 。 • cp:复制文件 。 • mv:移动文件 。 • mkdir:建立目录 。 • rmdir:删除目录 。 • find:寻找文件 。 • passwd:改变密码 。 • chfn:改变全名 。 • finger:显示用户信息 。 • rusers:显示所有用户 。

激光划片机

引线键合机

测试环境

测试平台

SRAM 静态随机存储器

RF DTV Tuner

待划片的圆片

二、 Cadence简介

• Cadence(Nasdaq股票代码:CDNS),全球最大的 EDA软件开发商,在当今集成电路和电子产品中发挥核心 作用。

• Cadence公司的客户采用Cadence的软件、硬件、设计方 法和服务,来设计和验证用于消费电子产品、网络和通讯 设备以及计算机系统中的尖端半导体器件、印刷电路板和 电子系统。

Cell Design Tutorial

图层定义及操作

数字版图设计流程

Step 1 导入LEF工艺文件 ............................................................................................................. 15 Step 2 导入时序文件................................................................................................................... 16 Step 3 导入Verilog......................................................................................................................... 17 Step 4 导入DEF文件..................................................................................................................... 18 Step 5 FloorPlan............................................................................................................................. 19 Step 6 手工添加Corner PAD......................................................................................................... 21 Step 7 Place IO PAD ...................................................................................................................... 23 Step 8 插入IO Bridge .................................................................................................................... 24 Step 9 放置宏单元 ........................................................................................................................ 24 Step 10 Add Power Ring................................................................................................................ 25

cadence仿真工具介绍1

( TB ( TO ( GT ( W1 ( A1 ( W2 ( A2 ( W3 ( A3

"nwell" ) "diff" ) "poly" ) "cut" ) "metal" ) "cut" ) "metal" ) "cut" ) "metal" )

COPYRIGHT FOR ZHOUQN

COPYRIGHT FOR ZHOUQN

原理图编辑窗口结构分类编辑命令菜单常用快捷命令菜单1instance调用库单元cellview浏览器librarycellviewnameoption阵列行数列数旋转x镜像y镜像variable如果有2addpin调用端口pinpinnames总线命名方式总线名放置方式pin的旋转和镜像3addwire连线narroworwide4wirename连线命名连线规则连线粗细连线名称连线名称的相关属性10属性参数修改9undo11chechandsave12save5放大缩小8删除6stretch拉动保持连接7copy从分类菜单中可以看到命令的快捷键和许多其它命令仿真环境设置版图设计基本过程和要求在一定工艺下根据电路的要求依据版图设计规则设计每个器件的图形并完成排版布线形成一套完整的电路光刻掩膜版图形

COPYRIGHT FOR ZHOUQN

版图主要编辑命令 (2)修改类命令 ) Undo, Redo , Move, Copy, 拉动,改变形状, 拉动,改变形状, 删除,查找, 删除,查找, 合并图形, 合并图形, 制作单元, 制作单元, 打散单元, 打散单元, 劈切图形, 劈切图形, 胀缩图形, 胀缩图形, 旋转图形等等。 旋转图形等等。

数字IC设计工具介绍

COMPOSER - CADENCE 逻辑图输入这个工具主要针对中小规模的ASIC以及MCU电路的逻辑设计,大的东西可能需要综合了。

虽然现在电路越设计越大,有人言必称SYNOPSYS,但只要仔细到市场上端详一下,其实相当大部分真正火暴卖钱的东西还是用CADENCE的COMPOSER加VIRTUOSO加VERILOG—XL加DRACULA流程做的。

原因很简单,客户可不买你什么流程的帐,什么便宜性能又好就买什么。

备用PC上的工具:WORKVIEW OFFICEDC - SYNOPSYS 逻辑综合这个不用说了,最经典的。

但老实说在我们现在的设计流程里用得还不多,最关键问题还是一个市场切入问题。

备用工作站上的工具:AMBIT,这个工具其实很不错,它和SE都是CADENCE出的,联合起来用的优势就很明显了。

PC上用的备用工具可以选NT版的SYNOPSYS,SYNPILIFY也不错,但主要是用做FPGA综合的。

其实最终你拿到的库有时最能说明问题,它不支持某工具,转换?急吧。

VIRTUOSO - CADENCE 版图设计这个大家比较熟了,但个人还是喜欢用PC上的TANNER。

原因是层与层之间的覆盖关系用调色的模式显示出来比直接覆盖显示就是舒服。

可惜人家老大,国产的《熊猫》也学了这个模式。

倒是以前有个COMPASS,比较好用,可惜现在不知哪去了。

SE - CADENCE 自动布局布线有了它,很多手工版图的活儿就可以不用做的,实在是一大进步。

可惜残酷市场上如果规模不大的东西人家手画的东西比你自动布的小40%,麻烦就大了。

APOLLO用的人还不是很多吧。

PC上的TANNER 据说也能做,针对线宽比较粗,规模不太大的设计。

VERILOG—XL - CADENCE 逻辑仿真VERILOG就是CADENCE的发明,我们的版本比较老,现在该工具是不是停止开发了?CADENCE 新推都叫NC-VERILOG。

SYNOPSYS的VCS是不是比NC强,反正两公司喊的挺凶,哪位对这个两个东西都比较了解,不妨对比一下。

集成电路(IC)设计完整流程详解及各个阶段工具简介

集成电路(IC)设计完整流程详解及各个阶段工具简介集成电路(ic)设计完整流程及工具集成电路的设计过程可以分为两部分:前端设计(也称为逻辑设计)和后端设计(也称为物理设计)。

这两部分之间没有统一而严格的界限。

任何与流程相关的设计都可以称为后端设计。

前端设计的主要流程:1、规格制定芯片规格与功能清单一样,是客户向芯片设计公司(称为fabless,fabless design company)提出的设计要求,包括芯片需要满足的具体功能和性能要求。

2.详细设计fabless根据客户提出的规格要求,拿出设计解决方案和具体实现架构,划分模块功能。

3、hdl编码使用硬件描述语言(VHDL、Verilog HDL,工业公司普遍使用)以代码形式描述和实现模块功能,即用HDL语言描述实际硬件电路功能,形成RTL(寄存器传输级)代码。

4.模拟验证仿真验证通过,进行逻辑综合。

逻辑综合的结果就是把设计实现的hdl代码翻译成门级网表netlist。

综合需要设定约束条件,就是你希望综合出来的电路在面积,时序等目标参数上达到的标准。

逻辑综合需要基于特定的综合库,不同的库中,门电路基本标准单元(standardcell)的面积,时序参数是不一样的。

所静态时序分析(STA)也属于验证范畴,主要从时序方面验证电路,并检查电路是否违反设置时间和保持时间。

这是数字电路的基础知识。

当寄存器中出现这两种时序冲突时,无法正确采样和输出数据,因此基于寄存器的数字芯片的功能肯定会出现问题。

sta工具是Synopsys的黄金时间。

7.正式核查这也是验证范畴,它是从功能上(sta是时序上)对综合后的网表进行验证。

常用的就是等价性检查方法,以功能验证后的hdl设计为参考,对比综合后的网表功能,他们是否在功能上存在等价性。

这样做是为了保证在逻辑综合过程中没有改变原先hdl描述的电路功能。

形式验证工具有synopsys的formality。

前端设计的流程暂时写到这里。

版图模拟集成电路版图设计工作流程

版图模拟集成电路版图设计工作流程

一、设计准备阶段

1.收集设计需求和规格

2.确定版图设计工具

(1)选择合适的版图设计软件

(2)熟悉工具操作方法

二、布局设计

1.绘制整体版图布局

(1)放置主要功能模块

(2)确定连线路径和间距

2.设计外围器件布局

(1)放置电容、电阻等器件

(2)保证布局紧凑和良好连接

三、器件布线

1.连接器件引脚

(1)确定引脚连接顺序

(2)绘制连线路径

2.优化布线

(1)考虑信号传输和功耗(2)调整布线路径提高性能

四、特殊器件设计

1.设计特殊功能模块

(1)绘制模拟电路部分(2)完成数字逻辑设计

2.验证特殊器件功能

(1)模拟仿真验证

(2)数字仿真测试

五、验证与调试

1.进行版图验证

(1)检查器件连接和间距(2)确保布局符合设计规范2.仿真验证

(1)电气仿真测试

(2)时序分析和功耗测试

六、提交版图

1.准备版图文件

(1)导出版图文件格式

(2)打包必要设计文件2.提交给布局工程师(1)交流设计细节和要求(2)确认后提交版图。

版图设计培训资料

5) virtuoso编辑器 --版图层次显示(LSW)

技术中心内部资料

26

第二部分:版图设计基础

3. 版图编辑器

6) virtuoso编辑器 --版图编辑菜单

技术中心内部资料

27

第二部分:版图设计基础

3. 版图编辑器

7) virtuoso编辑器 --显示窗口

技术中心内部资料

28

7) virtuoso编辑器--CDL输出

技术中心内部资料

37

第二部分:版图设计基础

5. 了解工艺厂商

GLOBALFOUNDRIES

HHG —华虹宏力

--中芯国际 CSMC – 华润上华 FMIC—深圳方正 TSMC -- 台积电 UMC -- 台联电 Winbond -- 华邦 先锋 比亚迪 新进 厦门集顺 无锡和舰

3. 版图编础

3. 版图编辑器

cell

3) virtuoso编辑器-- 建立

CIW窗口

技术中心内部资料

24

第二部分:版图设计基础

3. 版图编辑器

4) virtuoso编辑器--工作区和层次显示器

LSW

技术中心内部资料

工作区域

25

第二部分:版图设计基础

2.2互连

1) 典型工艺

CMOS N阱 1P4M工艺剖面图

连线与孔之间的连接

技术中心内部资料 21

第二部分:版图设计基础

3. 版图编辑器

建立LIBRARY

1) virtuoso编辑器

CIW窗口

技术中心内部资料

22

第二部分:版图设计基础

2) virtuoso编辑器--Library manager

SoC设计与EDA工具第3章-SoC设计与EDA工具(1)

版图电路图同一性比较(LVS,Layout Versus Schematic)

用于比较版图和原理图在晶体管级的连接是否正确。

ECO步骤之后需要进行 逻辑等效性检查

P&R

Phy. V.

ECO

Equivalence Checking

静态时序分析(Static Timing Analysis)

静态时序分析工具通过计算路径上延迟的总和,并比较相对于预定义时钟的延迟, 来检查是否满足时序要求。它仅关注时序间的相对关系而不是评估逻辑功能。 不需要测试激励,检查所有路径的时序。 常用工具,如Synopsys公司的Primetime。

快速搭建虚拟原型机

电子系统级(ESL)设计

Electronic System Level(ESL)设计指系统级的设计方法,是从算 法建模演变而来,已经演变为嵌入式系统软硬件设计、验证、调试的 一种补充方法学。

ESL设计以抽象方式来描述SoC硬件系统,给软硬件工程师提供一 个虚拟的硬件原型平台,用以进行硬件系统结构的探测和软件程序的 开发。

设计约束

综合工具按照什么样的原则来综合电路,该电路所要达到的指标是什么。

主要包括时序、面积、功耗、可测性等。

逻辑综合的流程

工艺无关

工艺相关

逻辑综合的举例

RTL描述:

module magnitude_comparator(A, B, clk, rst_b, A_gt_B, A_lt_B, A_eq_B);

BIST的基本结构

边界扫描测试

边界扫描的原理是在核心逻辑电路的I/O都增加一个寄存器,通 过将这些I/O上的寄存器连接起来,可以将数据串行输入被测单 元,并且从相应端口串行读出。也可以并行输入,并行输出。

集成电路版图基础.pdf

由一个NMOS,一个PMOS组成, 先画出两个正确尺寸的mos版图, 然后对mos的四端进行连线。

第二部分:版图设计基础

2.1.2 电阻

根据电路选择的电阻类型(ppolyf_s)、电阻的W/L值来画版图,相对应的电 阻类型应当由哪些层的图形组成,这个参照厂家提供的design rule。

1)集成电路掩膜版图设计是实现集成电路制造所必不 可少的设计环节,它不仅关系到集成电路的功能是 否正确,而且也会极大程度地影响集成电路的性能、 成本与功耗。

2)它需要设计者具有电路系统原理与工艺制造方面的 基本知识,设计出一套符合设计规则的“正确”版 图也许并不困难,但是设计出最大程度体现高性能、 低功耗、低成本、能实际可靠工作的芯片版图缺不 是一朝一夕能学会的本事。

第二部分:版图设计基础

4) 打开cell a--工作区和层次显示器

电路转换为选定工艺的版图,版图设计完成后,将版图的数据发 给foundry,foundry收到数据后按照数据制作掩膜版(mask), mask上的图形就代表了最终在芯片加工上需要保留或者需要刻蚀 掉的位置。

VDD

3u/0.18u

IN

OUT

1u/0.18u

GND

电路图

版图

第一部分:了解版图

3. 版图的意义:

第四部分:版图的艺术(这个作为后期目标,暂作了解)

1. 模拟版图和数字版图的首要目标 2. 匹配 3. 寄生效应 4. 噪声 5. 布局规划 6. ESD 7. 封装

IC模拟版图设计

第一部分:了解版图

1. 芯片是怎么来的 2. 版图的定义 3. 版图的意义 4. 版图的工具 5. 版图的设计流程

1) 启动软件

使用Xmanager登陆linux服务器

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

布局布线工具根据基本单元库的时序-几何模型, 将电路单元布局布线成为实际电路版图

Contents

1 2 3 基于标准单元的ASIC设计流程

数字前端设计(front-end)

数字后端设计(back-end)

数字前端设计流程-1

RTL file

综合

布局布线前静态时序分析

形式验证

整个ASIC设计流程都是一 个迭代的流程,在任何一步 不能满足要求,都需要重复 之前步骤,甚至重新设计 RTL代码。 模拟电路设计的迭代次数甚 至更多。。。

.synopsys_dc.setup启动文件 company =“ ”; designer =“Your name”; technology =“0.6 micro csmc”;

search_path =search_path+{“.” ~/csmc06/lib” };

target_library ={csmc06core.db};

link_library ={*, csmc06core.db, csmc06pad.db};

symbol_library ={csmc06core.sdb, csmc06pad.sdb};ALeabharlann IC design flow

Initial Setup :建立设计环境,技术库文件及其它设计环境设置。 DC .synopsys_dc.setup 文件

综合的定义

逻辑综合:决定设计电路逻辑门的相互连接。

逻辑综合的目的:决定电路门级结构、寻求时序和与 面积的平衡、寻求功耗与时序的平衡、增强电路的测 试性。 逻辑综合的过程:首先,综合工具分析HDL代码,用一 种模型(GTECH) ,对HDL进行映射,这个模型是与技术 库无关的;然后,在设计者的控制下,对这个模型进 行逻辑优化;最后一步,进行逻辑映射和门级优化, 将逻辑根据约束,映射为专门的技术目标单元库 (target cell library)中的cell,形成了综合后的 网表。

数字前端设计。以生成 可以布局布线的网表为 终点。

数字后端设计。以生成 可以可以送交foundry 进行流片的GDS2文件 为终点。 术语: tape-out—提交最终 GDS2文件做加工;

Foundry—芯片代工厂, 如中芯国际。。。

Floorplanning & Placement, CT Insertion Formal Verification (Scan Inserted Netlist Vs CT Inserted Netlist) Auto Routing DRC,LVS,ECO No Formal Verification (ECO Netlist vs CT Inserted Netlist) Post-layout STA Power check Timing OK? Yes Tape Out Astro AstroRail FORMALITY PT Hercules Caliber Virtuoso

基于standcell的ASIC设计流程

算法模型 c/matlab code

RTL HDL vhdl/verilog

综合工具根据基本单元库的功能-时序模型,将行 为级代码翻译成具体的电路实现结构

NETLIST verilog Standcell library LAYOUT gds2

对功能,时序,制造参数进行检查

ASIC design flow

Pre_layout 的 STA :用DC的静态时序分析引擎做block的STA,用PrimeTime 做full_chip的STA。 Setup_time分析 Hold_time分析 其时序约束和提供给DC做逻辑综合的约束相同。静态时序分析同综合一样 ,是一个迭代的过程,和cell的位置及布线关系密切,通常都执行多次 ,直到满足需要。

ASIC design flow

Compile and scan insert的scripts,采用bottom_up的编译方法

set_fix_multiple_port_net –buffer_constants –all compile –scan check_test create_test_pattern –sample 10 preview_scan insert_scan check_test 如果模块内的子模块具有dont_touch 属性需添加如下命令,因要插入扫描 remove_attribute find(-hierarchy design,”*”)dont_touch

ASIC design flow

设计举例,IIC控制器,已完成代码编写及功能仿真:

Tap_controller.v Tap_bypass.v Tap_instruction.v Tap_state.v 完成全部设计还需经过如下几个步骤:

Pre_layout Synthesis STA using PrimeTime SDF generation Verification Floorolanning and Routing Post_layout 反标来自layout tool的信息, STA using PrimeTime Post-layout Optimization Fix Hold-Time Violation

Write netlist

remove_unconnected_ports find(-hierarchy cell,”*”) change_names –hierarchy –rules BORG set_dont_touch current_design write –herarchy –output active_design+”.db” write –format verilog –hierarchy –output active_design+”.sv”

SYNOPSYS – Design Compiler

数字前端设计流程-3 使用DC综合

数字前端设计流程-4 使用DC综合

步骤可以归纳为: 1.指定综合使用的库 2.根据符号库将行为级模型 转换为逻辑网表(由逻辑单 元GTECH构成) 3.指定综合环境以及约束 4.进行综合,根据约束将逻 辑网标映射为实际网表(由 标准单元构成) 5.优化网表 6.输出综合结果

Synthesis:利用约束完成设计的门及实现及扫描插入

Constrain scripts

/* Create real clock if clock port is found */ if (find(port, clk) == {"clk"}) { clk_name = clk create_clock -period clk_period clk } /* Create virtual clock if clock port is not found */ if (find(port, clk) == {}) { clk_name = vclk create_clock -period clk_period -name vclk

数字流程与工具

Contents

1 2 3 基于标准单元的ASIC设计流程

数字前端设计(front-end)

数字后端设计(back-end)

基于standcell的ASIC设计流程

Concept + Market Research Architechtural specs & RTL coding RTL simulation Logic Synthesis,Optimization & Scan Insertion Formal Verification (RTL vs Gates) No Pre-layout STA Timing OK? Yes DC MODELSIM MBISTARCHITEC T FORMALITY PT

ASIC design flow

SDF generation,pre_layout的SDF文件,用于pre_layout timing仿真,同时还需提供时序约 束文件(SDF格式)给layout tool做布局布线。script文件如下:

active_design=tap_controller read active_design current_design active_design link Create_clock –period 33 –waveform {0 16.5} tck Set_dont_touch_network {tck trst} set_clock_skew –delay 2.0 –minus_uncertainty 3.0 tck set_driving_cell –cell BUFF1X –pin Z all_inputs() set_drive 0 {tck trst} set_input_delay 20.0 –clock tck –max all_inputs() set_output_delay 10.0 –clock tck –max all_outputs() write_timing –format sdf-v2.1 \ -output active_design+”.sdf” write_constraints –format sdf –cover_design\ -output constraints.sdf

}

Constrain scripts(续) /* Apply default drive strengths and typical loads for I/O ports */ set_load 1.5 all_outputs() set_driving_cell -cell IV all_inputs() /* If real clock, set infinite drive strength */ if (find(port, clk) == {"clk"}) { set_drive 0 clk } /* Apply default timing constraints for modules */ set_input_delay 1.2 all_inputs() -clock clk_name set_output_delay 1.5 all_outputs() -clock clk_name set_clock_skew -minus_uncertainty 0.45 clk_name /* Set operating conditions */ set_operating_conditions WCCOM /* Turn on Auto Wireload selection Library must support this feature */ auto_wire_load_selection = true