数字逻辑3-2

数字逻辑与数字系统设计第2-3章客观题

()1、数字电路又称为开关电路、逻辑电路。

答案:正确()2、二极管、三极管、场效应管是常用的开关元件。

答案:正确()3、最基本的逻辑关系是:与、或、非。

答案:正确()4、高电平用0表示,低电平用1表示,称为正逻辑。

答案:错误()5、TTL型门电路比CMS型门电路开关速度快。

答案:正确()6、逻辑表达式是逻辑函数常用的表示方法。

答案:正确()7、用真值表表示逻辑函数,缺乏直观性。

答案:错误()8、逻辑图是最接近实际的电路图。

答案:正确()9、由真值表得到的逻辑函数一般都要经过化简。

答案:正确()10、组合电路的特点是:任意时刻的输出与电路的原状态有关。

答案:错误()11、1+A=1答案:正确()12、AB+A=A()13、将实际问题转换成逻辑问题第一步是要先写出逻辑函数表达式。

答案:错误14、异或函数与同或函数在逻辑上互为反函数。

(对)每个最小项都是各变量相“与”构成的,即n个变量的最小项含有n个因子。

(对)15、因为逻辑表达式A+B+AB=A+B成立,所以AB=0成立。

(错)16、逻辑函数F=A B+A B+B C+B C已是最简与或表达式。

(错)17、利用约束项化简时,将全部约束项都画入卡诺图,可得到函数的最简形式。

(错)18、卡诺图中为1的方格均表示逻辑函数的一个最小项。

(对)19、在逻辑运算中,“与”逻辑的符号级别最高。

(错)20、标准与或式和最简与或式的概念相同。

(对)21、数字电路中用“1”和“0”分别表示两种状态,二者无大小之分。

(对)22、格雷码具有任何相邻码只有一位码元不同的特性。

(对)23、所有的集成逻辑门,其输入端子均为两个或两个以上。

(错)24、根据逻辑功能可知,异或门的反是同或门。

(对)25、逻辑门电路是数字逻辑电路中的最基本单元。

(对)26、TTL和CMOS两种集成电路与非门,其闲置输入端都可以悬空处理。

(错)27、74LS系列产品是TTL集成电路的主流,应用最为广泛。

PLC的位逻辑指令详细说明综述

LD =

C40 Q0.0

//装入计数器触点 //输出触点

• CTUD,增减计数器指令。有两个脉冲输入端:CU输 入端用于递增计数,CD输入端用于递减计数。 • 指令格式:CTUD Cxxx,PV • 例: CTUD C30,5

举例

指令表格式

LD I0.1 LD I0.2 LD I0.3 CTUD C50,+4 LD C50 = Q0.0

3.2.1 基本逻辑指令及应用

基本逻辑指令见P36 表3-2。 PLC规定:如果触点是常开触点,则常开触 点“动作”认为是“1”,常开触点“不动作” 认为是“0”; 如果触点是常闭触点,则常闭触点“动作” 认为是“0”,常闭触点“不动作”认为是 “1”;

位操作类指令

一、位操作指令介绍

1. 逻辑取(装载)及线圈驱动指令 LD(load):常开触点逻辑运算的开始。 LDN(load not):常闭触点逻辑运算的开始 =(OUT):线圈驱动指令。

Q0.0

//输出触点

C30, VW30 //比较计数器 //当前值是否大于 //VW30 中的值

= Q0.1 程序举例

//输出触点

5000

5000

C3 0 当前值

1000

1000

Q 0.0

Q 0.1

时序图

3.7 运算指令

一、算术运算指令 二、逻辑运算指令

算术运算指令在累加器1和2中进行, 在累加器2中的值作为被减数或被除数。算 术运算的结果保存在累加器1中,累加器1 原有的值被运算结果覆盖,累加器2中的值 保持不变

在 EU 指令前有一个上升沿时(由 OFF→ON )产生一个宽 度为一个扫描周期的脉冲,驱动后面的输出线圈。

下降沿触发指令:ED

《数字逻辑》第3章习题答案

题

【3-1】填空: (1) 逻辑代数中有三种最基本运算: 与 、 或 和 非 ,在此基础上又派生出五种基本运算, 分别为 与非 、 或非 、 异或 、 同或 、和 与或非 。 (2) 与运算的法则可概述为:有 0 出 0 ,全 1 出 1 ;类似地,或运算的法则为 有”1”出”1”, 全”0”出”0” 。 (3) 摩根定理表示为: A B = A B ; A B = A B 。 (4) 函数表达式 Y= AB C D ,则其对偶式为 Y ' = ( A B)C D 。 积的形式结果应为 M ( 0,1,2,4,5,8,9,10)。 (5) 函数式 F=AB+BC+CD 写成最小项之和的形式结果应为 m ((3,6,7,11,12,13,14,15)), 写成最大项之

0 0 1 1 1 1

1 1 0 0 1 1

0 1 0 1 0 1

1 1 0 0 1 0

【3-8】写出下列函数的反函数 F ,并将其化成最简与或式。 (1) F1 ( A D )( B C D)( AB C ) (2) F2 ( A B )( BCD E )( B C E )(C A) (3) F3 A B C A D (4) F4 ( A B)C ( B C ) D 解: (1) F1 AD C (2) F2 AB A C E (3) F3 AB AC A D (4) F4 BC C D ABD A B C 【3-9】用对偶规则,写出下列函数的对偶式 F ,再将 F 化为最简与或式。 (1) F1 AB B C A C (2) F2 A B C D (3) F3 ( A C )( B C D)( A B D) ABC (4) F4 ( A B )( A C )( B C )(C D) (5) F5 AB C CD BD C 解:题中各函数对偶函数的最简与或式如下: (1) F1 A BC AB C (2) F2 A B D A C D (3) F3 AC A BD (4) F4 A BC B C CD (5) F5 ABC D (6) F6 AB C D 【3-10】已知逻辑函数 F A B C , G=A⊙B⊙C,试用代数法证明: F G 。 解:

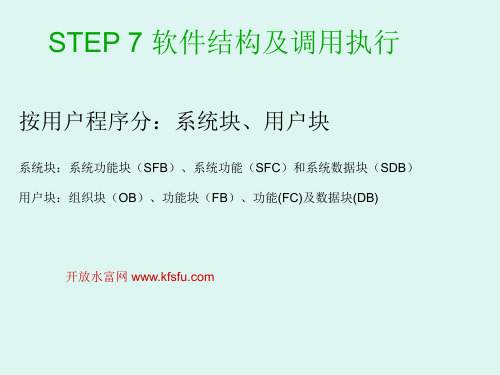

数字逻辑第3章 门电路

逻辑式:Y=A + B

逻辑符号: A 1

B

Y

电压关系表

uA uB uY

0V 0V 0V 0V 3V 2.3V 3V 0V 2.3V 3V 3V 2.3V

真值表

ABY

0

0

0

0

1

1

1

0

1

1

1

1

三、三极管非门

5V

利用二极管的压降为0.7V, 保证输入电压在1V以下时,

电路可靠地截止。

A(V) Y(V) <0.8 5 >2 0.2

II H &

II L &

… …

NOH

I OH (max) I IH

N MIN ( NOH , NOL )

NOL

IOL(max) I IL

六、CMOS漏极开路门(OD)门电路(Open Drain)

1 . 问题的提出

普通门电路

在工程实践中,往往需要将两个门的输出端 能否“线与”?

并联以实现“与”逻辑功能,称为“ 线与 。

输入 0 10% tr tf

tPHL

输出

tPLH

tr:上升时间

tf:下降时间 tw:脉冲宽度 tPHL:导通传输时间

tPLH:截止传输时间

平均传输延迟时间 (Propagation delay)

tpd= tpHL+ tpLH 2

5、功耗: 静态功耗:电路的输出没有状态转换时的功耗。 动态功耗:电路在输出发生状态转换时的功耗。

PMOS

NMOS

3、增强型MOSFET的开关特性

iD管可变子类型恒

VGS1 击开/关的条(件1)N沟道增强开型/M关O的S等FE效T电:路

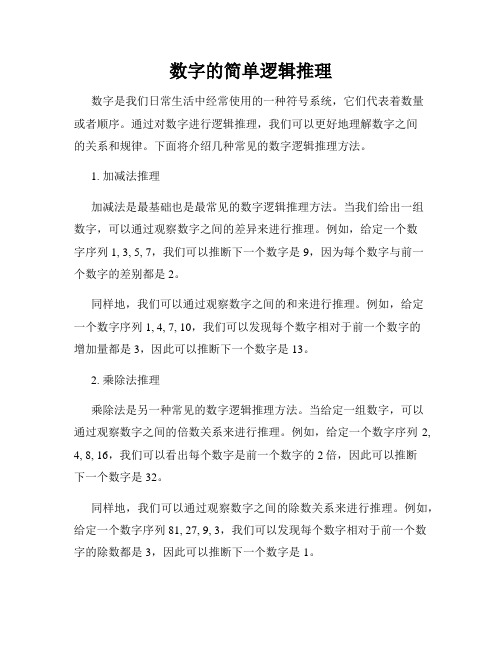

数字的简单逻辑推理

数字的简单逻辑推理数字是我们日常生活中经常使用的一种符号系统,它们代表着数量或者顺序。

通过对数字进行逻辑推理,我们可以更好地理解数字之间的关系和规律。

下面将介绍几种常见的数字逻辑推理方法。

1. 加减法推理加减法是最基础也是最常见的数字逻辑推理方法。

当我们给出一组数字,可以通过观察数字之间的差异来进行推理。

例如,给定一个数字序列1, 3, 5, 7,我们可以推断下一个数字是9,因为每个数字与前一个数字的差别都是2。

同样地,我们可以通过观察数字之间的和来进行推理。

例如,给定一个数字序列1, 4, 7, 10,我们可以发现每个数字相对于前一个数字的增加量都是3,因此可以推断下一个数字是13。

2. 乘除法推理乘除法是另一种常见的数字逻辑推理方法。

当给定一组数字,可以通过观察数字之间的倍数关系来进行推理。

例如,给定一个数字序列2, 4, 8, 16,我们可以看出每个数字是前一个数字的2倍,因此可以推断下一个数字是32。

同样地,我们可以通过观察数字之间的除数关系来进行推理。

例如,给定一个数字序列81, 27, 9, 3,我们可以发现每个数字相对于前一个数字的除数都是3,因此可以推断下一个数字是1。

3. 序列推理序列推理是另一种常见的数字逻辑推理方法,它涉及到数字之间的顺序和模式。

当给定一组数字,可以通过观察数字的排列规律来进行推理。

例如,给定一个数字序列2, 4, 8, 16,我们可以看出每个数字是前一个数字的2倍,因此可以推断下一个数字是32。

同样地,我们可以通过观察数字的顺序来进行推理。

例如,给定一个数字序列3, 8, 15, 24,我们可以发现每个数字的差异依次是5, 7, 9,因此可以推断下一个数字的差异应该是11。

根据这个规律,我们可以推断下一个数字是35。

4. 质数推理质数是指只能被1和自身整除的数字。

质数推理涉及到质数之间的关系和规律。

当给定一组数字,可以通过观察数字是否为质数来进行推理。

例如,给定一个数字序列2, 3, 5, 7,我们可以发现每个数字都是质数,因此可以推断下一个数字应该是11。

数字逻辑4-3-2组合电路中的险象判断

组合逻辑电路险象判断

卡诺图法

当描述电路的输出函数是“与-或”表达式时, 采用卡诺图判断比较方便。具体方法是先将函 数读入卡诺图中,并画出对应各个与项的卡诺 图圈。接着检查是否存在两个相邻的最小项没 有被任一个卡诺图圈圈在一起。若存在,则当 输入变量在这两个最小项对应的值之间变化时, 存在险象。若没有这种情况,则不存在险象。

数字逻辑

章晓卿

上海交通大学继续教育学院

第3章 集成门电路

4.1 组合电路的分析方法 4.2 组合电路的设计方法 4.3 组合电路中的险象问题

险象产生 险象判断 险象消除

数字逻辑 第4章 组合逻辑电路

组合逻辑电路险象判断

当某一个输入变量X同时以原变量X和反变 量X形式出现在函数表达式中,且在一定条件 下函数表达式可以转换为X+X或者XX的形式 时,则当输入X 变化时,由于竞争可能产生险 象。

数字逻辑

第4章 组合逻辑电路

组合逻辑电路险象判断

有两种方法判断组合电路是否存在险象: 代数法 根据描述电路的函数表达式来判断相应电 路是否具有产生险象的条件。具体步骤: 首先检查找出具备竞争条件的输入变量,该 变量X同时以原变量和反变量的形式出现在 表达式中。

数字逻辑 第4章 组合逻辑电路

组合逻辑电路险象判断

可见,输入C变化时不可能产生险象。

数字逻辑 第4章 组合逻辑电路

组合逻辑电路险象判断

例2 例如设描述电路的逻辑函数为:

F ( A B)( A C )( B C )

找出具有竞争条件的输入变量:A和B。分别对A、 B进行检查。

数字逻辑

第4章 组合逻辑电路

组合逻辑电路险象判断

(1)表达式中只保留A,BC分别以00、01、 10、11的逻辑值代入表达式,得到如下结果:

数电逻辑16个公式

数电逻辑16个公式1.与门公式(AND gate):输出为1当且仅当所有输入都为1,否则输出为0。

公式为:Y = A * B。

2.或门公式(OR gate):输出为0当且仅当所有输入都为0,否则输出为1。

公式为:Y = A + B。

3.非门公式(NOT gate):输出与输入相反。

公式为:Y = ̅A。

4.异或门公式(XOR gate):输出为1当且仅当输入中只有一个是1,否则输出为0。

公式为:Y = A ⊕ B。

5.与非门公式(NAND gate):输出为0当且仅当所有输入都为1,否则输出为1。

公式为:Y = ̅(A * B)。

6.或非门公式(NOR gate):输出为1当且仅当所有输入都为0,否则输出为0。

公式为:Y = ̅(A + B)。

7.同或门公式(XNOR gate):输出为1当且仅当输入中所有位都相同,否则输出为0。

公式为:Y = A ⊙ B。

8.三输入与门公式(3-input AND gate):输出为1当且仅当所有输入都为1,否则输出为0。

公式为:Y = A * B * C。

9.三输入或门公式(3-input OR gate):输出为0当且仅当所有输入都为0,否则输出为1。

公式为:Y = A + B + C。

10.三输入异或门公式(3-input XOR gate):输出为1当且仅当输入中有奇数个1,否则输出为0。

公式为:Y = A ⊕ B ⊕ C。

11.三输入与非门公式(3-input NAND gate):输出为0当且仅当所有输入都为1,否则输出为1。

公式为:Y = ̅(A * B * C)。

12.三输入或非门公式(3-input NOR gate):输出为1当且仅当所有输入都为0,否则输出为0。

公式为:Y = ̅(A + B + C)。

13.与-或非门公式(AND-OR-NOT gate):输出为1当且仅当输入经过与门并通过或门后为1,否则输出为0。

公式为:Y = ̅(A * B) + C。

第2章 数字逻辑基础(3)

R F C D

将影响输出逻辑的低电平值。

2.5.2 CMOS门电路

(Complementary Symmetry MOS)

1. CMOS反相器

和NMOS反相器一样,CMOS反相器是CMOS逻辑电 路中最基本的单元电路。 图中驱动管T1为NMOS管,负载管T2 为PMOS管,为保证电路正常工作,电 源电压VDD大于两管的开启电压的绝 对值之和。

2.5 MOS门电路 MOS门电路具有制造工艺简单、集成度高、功耗低、

体积小、成品率高等优点。

特别适用于中、大规模集成电路的制造,是目前集成

电路中的主打产品。

VDD

2.5.1 NMOS门电路 1. NMOS反相器

T2

F=A

1)T2管为负载管,始终导通,导通阻

抗为T1管导通阻抗的10~100倍。 2)T1管为驱动管,A为1时导通,输出 低电平, A为0时截止,输出高电平。

Vo

C

工作原理:设两管开启电压的绝对值为2V,VDD=5V.输入

信号在0~5V内连续变化。 (1) C=0V,C=5V时,传输门截止.(T1和T2均截止)

(2) C=5V,C=0V时,传输门导通.(T1和T2总有一只导通)

关于CMOS传输门: (1)由于MOS为对称的,源极和漏极可以互换,输入和输出 端也可互换,即CMOS传输门为双向的。

(2) 传输门和非门结合,可组成模拟开关。

Vi C

TG

Vo 1

Vi

SW C

Vo

3. CMOS集成电路的主要特点和注意事项 特点: 1) 功耗低 2) 工作电源电压范围宽 3) 抗干扰能力强 4) 带负载能力强 5) 输出幅度大 使用注意事项: 1) 多余的输入端不能悬空 2) 注意输入电路的过流保护 3) 电源电压极性不能反接,防止输出短路。

《数字逻辑》第3章作业与习题_单选题第六小题已更正版本

。

20.如果某 TTL 与非门的输入低电平噪声容限 VNL=0.7V,输入低电平

ViL=0.2V,那么它的关门电平 Voff 为

。

21.对于或非门,只要有一个输入为高电平,则输出就为 电平,所以

对或非门多余输入端的处理不能接 电平。

22.对于 TTL 与非门,只要有一个输入为低电平,则输出就为 电平,

为

,按抗干扰能力强弱的顺序依次为

,按静态功耗低和高的顺序依次为

。

6. 假设 VGS(TH)为开启电压,一般在 1~3V 范围内,则 NMOS 管当

时

截止,当

时导通;PMOS 管当

时截止,当

时

导通。

7. CMOS 反相器是由

作为驱动管,

作为负载管形成了 电

路结构。

2)单选题

1.硅二极管导通和截止的条件是( )。

不形成

;在外电场作用下,

和

均能参与导电。

7. 半导体中载流子的两种运动方式指

运动和

运动。

8. 硅二极管的截止条件是

,导通条件是

。

9. 数字电路中的晶体三极管作为开关元件,主要工作在

和

。

10. 三种基本逻辑门是

、

、

。

11. 与门是可以实现

的电路。

12. 在 TTL 电路中,输入端悬空等效于逻辑 电平,但为了避免引入干

② 输出端能带同类门的输入端个数

③ 输出端能带同类门的个数

④ 输入端数

7.输出端可直接连在一起实现“线与”逻辑功能的门电路是( )。

① 与非门

② 或非门 ③ OC 门

④ 异或门

8.两输入变量 A、B 的逻辑门的输出、输入如图所示,根据输出波形 Y,该

数字逻辑(科学出版社 第五版)课后习题答案

1 1 0 0 0 0 0 0

2 D0 1 0 0 0 0 0 0

3 D1 D0 1 0 0 0 0 0

4 D2 D1 D0 1 0 0 0 0

5 D3 D2 D1 D0 1 0 0 0

6 D4 D3 D2 D1 D0 1 0 0

7 D5 D4 D3 D2 D1 D0 10

二进制十进制八进制

1010 10 12

111101 61 75

1011100 92134

0.10011 0.59375 0.46

101111 47 57

01101 13 15

3.将下列十进制数转换成8421BCD码

1997=0001 1001 1001 0111

65.312=0110 0101.0011 0001 0010

证明:左边= ABC+A C+AB

= ABC+A C+AB +ABC

=AC(B+ )+AB(C+ )

=AB+AC

=右边

(3) =A+CD+E

证明:左边=

=A+CD+A + E

=A+CD+ E

=A+CD+E

=右边

(4) =

证明:左边=

=

= =右边

8.用布尔代数化简下列各逻辑函数表达式

(1)F=A+ABC+A +CB+ = A+BC+

19.设计保密锁。

解:设A,B,C按键按下为1,F为开锁信号(F=1为打开),G为报警信号(G=1为报警)。

(1)真值表

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Never

Yes , but only Yes , but need one is not Z ! pull up resistor !

Schmitt – Trigger input

Use feedback circuit to shift the switching threshold depending on the input changing ways.

Hysteresis: the difference between the threshold

Schmitt – Trigger input

It can be used to eliminate noise !

Real behavior

The input between VIL and VIH : amplified area !

Logic level and noise margin

The input limit : to avoid the noise be amplified!

Device informations from the data sheet

Limitation for output current and resistive load.

Use NAND2 to drive LED

Fig 3-54 74AC Device : VOLmax = 0.37 V

R (5 0.37 1.6) /10 0.303k 303

If an input is not used ?

If an input keep floating, the output will be undecided, or the gate may be damaged ! Must connected it to some where !

Can we connect more than one output to a single line?

0.35 Rp

0.பைடு நூலகம்2

4.4 Rn

0.91 Rp

4

3.84 Rn

Rp 0.151k 151

Output driven ability

For NAND2 in Table 3-3: If VOHmin= 3.84 V Then IOHmax=4 mA R > 3.84/4 = 0.96 kΩ

Static model of CMOS when output is hold on 1 or 0

R will be changed with VG

The electric model for basic CMOS circuit

When Vx is increased, Rp will be increased and Rn be decreased !

Use Table 3-3 : 74HC00 (NAND2x4) Commercial: Vcc> 4.75 Military:Vcc>4.5

Get resistor value from the data sheet

For commercial device High level output (use minimal value)

The resistors are changed with input

Figure 3-8 3-9 The output voltage is changed When input voltage changed.

Steady-state behavior for inverter

Ideal behavior