专题4 精简8位CPU电路设计

8位移位寄存器的电路设计与版图实现要点

8位移位寄存器的电路设计与版图实现要点8位移位寄存器的电路设计与版图实现摘要电⼦设计⾃动化,缩写为EDA,主要是以计算机为主要⼯具,⽽Tanner EDA则是⼀种在计算机windows平台上完成集成电路设计的⼀种软件,基本包括S-Edit,T-Spice,W-Edit,L-Edit与LVS等⼦软件,其S-Edit以及L-Edit为常⽤软件,前者主要实现电路设计,后者主要针对的是已知电路的版图绘制,⽽T-Spice主要可实现电路图及版图的仿真,可以⽤Tanner EDA实现电路的设计布局以及版图实现等⼀系列完整过程。

本⽂⽤Tanner EDA⼯具主要设计的是8位移位寄存器,移位寄存器主要是⽤来实现数据的并⾏和串⾏之间的转换以及对数据进⾏运算或专业处理的⼯具,主要结构构成是触发器,触发器是具有储存功能的,可以⽤来储存多进制代码,⼀般N 位寄存器就是由N个触发器构成,移位寄存器⼯作原理主要是数据在其脉冲的作⽤下实现左移或者右移的效果,输⼊输出的⽅式表现为串⾏及并⾏⾃由组合,本设计就是在Tanner EDA的软件平台上进⾏对8位移位寄存器的电路设计仿真,再根据电路图在专门的L-Edit 平台上完成此电路的版图实现,直⾄完成的结果和预期结果保持⼀致。

关键词:Tanner EDA;L-Edit;移位寄存器,S-Edit8 bits shift register circuit design and layoutAbstractElectronic design automation,referred to as EDA,it is based on computers as the main tool,and Tanner EDA is a kind of software that complete the integrated circuit design on Windows platforms.Its Sub-Softwares include S-Edit,T-Spice,W-Edit,L-Edit and LVS and so on.S-Edit and L-Edit are commonly used software,S-Edit is primarily designed to achieve circuit,the latter is aimed primarily known circuit layout drawing,T-Spice can achieve schematic and layout simulation.We can achieve layout of the circuit design and a series of complete process layout used Tanner EDA tools.In this paper, Tanner EDA tools are mainly designed an 8-bit shift register.The shift register is mainly used for data conversion between parallel and serial, and the data processing tool operation or professional,its main structure is the trigger composition,flip-flop is a storage function,it can be used to store more hexadecimal code,In general N-bits register is composed of N trigger.Working principle of the shift register data under the action of the pulse, mainly the effect of the shift to the left or right,input and output of the way of serial and parallel free combination.This design is in Tanner on the EDA software platform to 8 bits shift register circuit design and simulation,then according to the circuit diagram on special L - Edit platform to complete the circuit layout implementation,until the finish is consistent with the results and expected results.Keywords:Tanner EDA;L-Edit;Shift register,S-Edit⽬录1 前⾔ (1)1.1 课题的背景和⽬的 (1)1.2课题的设计内容 (1)2 设计软件简介 (2)2.1EDA技术的介绍 (2)2.2T ANNER EDA T OOLS的简述 (2)2.3T ANNER软件的组成及发展 (3)2.3.1 Tanner的设计流程 (4)2.3.2 Tanner软件的发展 (5)2.3.3 L-Edit软件的介绍 (6)2.48位移位寄存器的⼯作原理和设计要求 (9)2.4.1 ⼯作原理 (9)2.4.2 电路结构与设计 (11)3 8位移位寄存器的电路设计与版图实现过程 (13)3.1各个模块的设计与仿真 (13)3.1.1 带复位端D触发器的设计与版图实现 (13)3.1.2 与或⾮门的设计与版图实现 (16)3.28位移位寄存器的电路设计与版图实现 (18)3.2.1 8位移位寄存器的电路结构 (18)3.2.2 8位移位寄存器的版图实现 (19)3.2.3 LVS对⽐ (21)4 结束语 (21)参考⽂献 (22)巢湖学院2013届本科毕业论⽂(设计)1 前⾔1.1 课题的背景和⽬的随着科技的进步,近⼏个世纪寄存器技术不断成熟,在数字电路中,寄存器已经是⼀个经常被提出的概念,它主要指的是⽤来存放⼆进制数据或者代码的电路。

8bitCPU

正弦信号发生器实验报告88132639殷达1.实验内容(1)设计要求:设计一正弦信号发生器,采用ROM 宏功能模块进行一个周期数据存储,并通过地址发生器产生正弦信号。

(2)设计内容:地址6位;ROM :6位地址8位数据;原理图完成顶层设计;2.实验原理(1)正弦波信号发生器是由地址发生器和正弦波数据存储器ROM 两块构成,输入为时钟脉冲,输出为8位二进制。

(2)地址发生器的原理: 地址发生器实质上就是计数器,ROM 的地址是6位数据,相当于64位循环计数器。

(3)只读存储器ROM 的设计 、VHDL 编程的实现①基本原理:为每一个存储单元编写一个地址,只有地址指定的存储单元才能与公共的I/O 相连,然后进行存储数据的读写操作。

②逻辑功能:地址信号的选择下,从指定存储单元中读取相应数据。

(4)基于LPM 宏功能模块的存储器的设计①LPM :Library of Parameterized Modules ,可参数化的宏功能模块库。

②Quartus II 提供了丰富的LPM 库,这些LPM 函数均基于Altera 器件的结构做了优化处理。

③在实际的工程中,设计者可以根据实际电路的设计需要,选择LPM 库中适当的模块,并为其设置参数,以满足设计的要求,从而在设计中十分方便的调用优秀的电子工程技术人员的硬件设计成果。

3.原理图,VHDL 设计(1)ROM 的单元数据(2)地址发生器的VHDL 语言的实现library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity addr_count isport(clk1kHz: in std_logic;qout: out integer range 0 to 63);end addr_count;architecture behave of addr_count issignal temp:integer range 0 to 63;beginprocess(clk1kHz)beginif(clk1kHz'event and clk1kHz='1') thenif(temp=63) thentemp<=0;elsetemp<=temp+1;end if;end if;qout<=temp;end process;end behave;(3)为了在示波器上得到更好的现象需要对FPGA模块进行分频处理分频的VHDL语言如下library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity fenpin isgeneric(N: integer:=800);port(clkin: in std_logic;clkout: out std_logic);end fenpin;architecture behave of fenpin issignal cnt:integer range 0 to N-1;begin--fenpinprocess(clkin)beginif(clkin'event and clkin='1')thenif(cnt<N-1)thencnt<=cnt+1;elsecnt<=0;end if;end if;end process;process(cnt)beginif(cnt<n/2)thenclkout<='1';elseclkout<='0';end if;end process;end behave;(4)顶层设计原理图(5)仿真报告。

8位骨灰级CPU电路图

9 10

12 13

2 1

1 2 13

U 29A 12 74F 10

Y1

1 3 74F 02 U 24B 5 4 6 74F 02 U 24C 8 10 9 74F 02

R1 锁存

3 1 74F 86

DB 7 DB 6 DB 5 DB 4

DB 3 DB 2 DB 1 DB 0

DB 7 DB 6 DB 5 DB 4 DB 3 DB 2 DB 1 DB 0

19 16 15 12 9 6 5 2

U 10E 74F 04 10 12

U 10F 74F 04 8

2Y 4 2Y 3 2Y 2 2Y 1

6

8

6

B4 B3 B2 B1 2G

17 15 13 11 19

A LU _A7 A LU _A6 A LU _A5 A LU _A4 A LU _A3 A LU _A2 A LU _A1 A LU _A0

3 5 7 9

12 14 16 18

2

U 11B 74F 20

U 26A 74F 20

U 27 74F 30

U 26B 74F 20

U 28A 74F 20

U 23B 74F 00

B

11

3

3 5 7 9

1 2

4 5

1 2 3 4

1 2

4 5

4

累加器到 RA M 传送指令 累加器到寄存器传送指令 加法指令

8 13 12

8 10 74F 32

A4 A3 A2 A1 1G

执行1电平 2

执行 1脉冲3

U 4C 9

1 11

3 4 7 8 13 14 17 18

3 5 7 9

8位CPU的设计与实现

计算机组成原理实验题目8位CPU得系统设计学号1115106046姓名魏忠淋班级 11电子B 班指导老师凌朝东华侨大学电子工程系8位CPU得系统设计一、实验要求与任务完成从指令系统到CPU得设计,编写测试程序,通过运行测试程序对CPU设计进行正确性评定。

具体内容包括:典型指令系统(包括运算类、转移类、访存类)设计;CPU结构设计;规则文件与调试程序设计;CPU调试及测试程序运行。

1。

1设计指标能实现加减法、左右移位、逻辑运算、数据存取、有无条件跳转、内存访问等指令;1、2设计要求画出电路原理图、仿真波形图;二、CPU得组成结构三、元器件得选择1.运算部件(ALU)ALU181得程序代码:LIBRARY IEEE;USEIEEE、STD_LOGIC_1164。

ALL;USEIEEE、STD_LOGIC_UNSIGNED.ALL;ENTITY ALU181 ISPORT(S: IN STD_LOGIC_VECTOR(3 DOWNTO0 );A:IN STD_LOGIC_VECTOR(7 DOWNTO0);B: INSTD_LOGIC_VECTOR(7DOWNTO 0);F : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);ﻩCOUT:OUTSTD_LOGIC_VECTOR(3 DOWNTO0);M :INSTD_LOGIC;CN : IN STD_LOGIC;CO,FZ:OUT STD_LOGIC );END ALU181;ARCHITECTURE behav OF ALU181 ISSIGNALA9 :STD_LOGIC_VECTOR(8DOWNTO 0);SIGNAL B9 : STD_LOGIC_VECTOR(8 DOWNTO0);SIGNALF9: STD_LOGIC_VECTOR(8 DOWNTO0);BEGINA9<= '0'& A; B9 <= ’0’&B;PROCESS(M,CN,A9,B9)BEGINCASE S ISWHEN "0000" =〉IF M='0’THEN F9<=A9 + CN ; ELSE F9<=NOT A9; E NDIF;WHEN "0001" =>IF M='0’THEN F9<=(A9 orB9)+ CN ;ELSE F9〈=NOT(A9OR B9);END IF;WHEN ”0010"=> IF M=’0’THEN F9〈=(A9 or(NOT B9))+C N; ELSE F9<=(NOT A9) ANDB9; ENDIF;WHEN "0011"=> IF M='0’THEN F9<= ”000000000"—CN ;ELSEF9<="000000000”;END IF;WHEN"0100”=> IFM='0'THENF9<=A9+(A9 ANDNOT B9)+ CN; ELSE F9〈=NOT(A9 ANDB9);END IF;WHEN ”0101”=>IFM='0' THENF9<=(A9orB9)+(A9 AND NOTB9)+CN ;ELSEF9<=NOT B9; END IF;WHEN"0110" =>IFM=’0’THEN F9〈=(A9- B9) -CN ;ELSE F9〈=A9XOR B9; ENDIF;WHEN”0111"=>IF M='0' THEN F9〈=(A9 or(NOT B9)) -CN ;ELSE F9<=A9 and (NOT B9); END IF;WHEN"1000" =>IFM='0'THEN F9<=A9+ (A9AND B9)+CN ; ELSE F9〈=(NOTA9)and B9; END IF;WHEN "1001”=> IF M=’0’THEN F9〈=A9+ B9 + CN ; ELSE F9<=NOT(A9 XOR B9); ENDIF;WHEN ”1010"=>IF M=’0'THEN F9〈=(A9or(NOTB9))+(A 9AND B9)+CN ; ELSEF9<=B9;END IF;WHEN "1011”=〉IF M='0'THENF9<=(A9 AND B9)- C N; ELSE F9<=A9 ANDB9; ENDIF;WHEN ”1100”=〉IF M='0'THENF9<=(A9 +A9) + CN; ELSEF9〈="000000001"; END IF;WHEN "1101”=〉IF M='0' THEN F9〈=(A9or B9)+ A9 + CN;ELSEF9〈=A9 OR (NOTB9); END IF;WHEN "1110"=>IF M='0'THENF9<=((A9 or (NOTB9)) +A9) + CN; ELSE F9〈=A9OR B9;END IF;WHEN”1111”=〉IFM=’0'THENF9<=A9 —CN ;ELSE F9<=A9 ; END IF;WHEN OTHERS=> F9<= ”000000000" ;ENDCASE;IF(A9=B9) THENFZ<=’0';END IF;ﻩEND PROCESS;F<=F9(7DOWNTO0) ;CO<= F9(8) ;COUT<="0000"WHEN F9(8)=’0'ELSE"0001";END behav;ALU得原理图:2、微控制器实现信息传送要靠微命令得控制,因此在CPU 中设置微命令产生部件,根据控制信息产生微命令序列,对指令功能所要求得数据传送进行控制,同时在数据传送至运算部件时控制完成运算处理。

8位CPU的设计与实现

计算机组成原理CPU 实验题目 8位的系统设计1115106046 号学魏忠淋姓名B 11电子班班级凌朝东指导老师华侨大学电子工程系8位CPU的系统设计一、实验要求与任务完成从指令系统到CPU的设计,编写测试程序,通过运行测试程序对CPU设计进行正确性评定。

具体内容包括:典型指令系统(包括运算类、转移类、访存类)设计;CPU结构设计;规则文件与调试程序设计;CPU调试及测试程序运行。

1.1设计指标能实现加减法、左右移位、逻辑运算、数据存取、有无条件跳转、内存访问等指令;1.2设计要求画出电路原理图、仿真波形图;二、CPU的组成结构三、元器件的选择1.运算部件(ALU)ALU181的程序代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ALU181 ISPORT (S : IN STD_LOGIC_VECTOR(3 DOWNTO 0 );A : IN STD_LOGIC_VECTOR(7 DOWNTO 0);B : IN STD_LOGIC_VECTOR(7 DOWNTO 0);F : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);COUT : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);M : IN STD_LOGIC;CN : IN STD_LOGIC;CO,FZ: OUT STD_LOGIC );END ALU181;ARCHITECTURE behav OF ALU181 ISSIGNAL A9 : STD_LOGIC_VECTOR(8 DOWNTO 0);SIGNAL B9 : STD_LOGIC_VECTOR(8 DOWNTO 0);SIGNAL F9 : STD_LOGIC_VECTOR(8 DOWNTO 0);BEGINB9 <= '0' & B ; A9 <= '0' & A ;PROCESS(M,CN,A9,B9)BEGINCASE S ISWHEN ぜ?尰=> IF M='0' THEN F9<=A9 + CN ; ELSE F9<=NOT A9; END IF;WHEN IF M='0' THEN F9<=(A9 or B9) + CN ; ELSEF9<=NOT(A9 OR B9); END IF;WHEN 0 => IF M='0' THEN F9<=(A9 or (NOT B9))+ CN ; ELSEF9<=(NOT A9) AND B9; END IF;WHEN 1 => IF M='0' THEN F9<= ; ELSEF9<= END IF;WHEN 0 => IF M='0' THEN F9<=A9+(A9 AND NOT B9)+ CN ; ELSE F9<=NOT (A9 AND B9); END IF;WHEN 1 => IF M='0' THEN F9<=(A9 or B9)+(A9 AND NOT B9)+CN ; ELSE F9<=NOT B9; END IF;WHEN 0 => IF M='0' THEN F9<=(A9 - B9) - CN ; ELSE F9<=A9 XOR B9; END IF;WHEN 1 => IF M='0' THEN F9<=(A9 or (NOT B9)) - CN ; ELSE F9<=A9 and (NOT B9); END IF;WHEN @0 => IF M='0' THEN F9<=A9 + (A9 AND B9)+CN ; ELSE F9<=(NOT A9)and B9; END IF;WHEN @1 => IF M='0' THEN F9<=A9 + B9 + CN ; ELSE F9<=NOT(A9 XOR B9); END IF;WHEN A0 => IF M='0' THEN F9<=(A9 or(NOT B9))+(A9 AND B9)+CN ;ELSE F9<=B9; END IF;WHEN A1 => IF M='0' THEN F9<=(A9 AND B9)- CN ;ELSE F9<=A9 AND B9; END IF;WHEN H0 => IF M='0' THEN F9<=(A9 + A9) + CN ; ELSEF9<= END IF;WHEN H1 => IF M='0' THEN F9<=(A9 or B9) + A9 + CN ; ELSEF9<=A9 OR (NOT B9); END IF;WHEN I0 => IF M='0' THEN F9<=((A9 or (NOT B9)) +A9) + CN ; ELSEF9<=A9 OR B9; END IF;WHEN I1 => IF M='0' THEN F9<=A9 - CN ; ELSEF9<=A9 ; END IF;WHEN OTHERS => F9<=END CASE;IF(A9=B9) THEN FZ<='0';END IF;END PROCESS;F<= F9(7 DOWNTO 0) ; CO <= F9(8) ;COUT<=END behav;ALU的原理图:2.微控制器实现信息传送要靠微命令的控制,因此在CPU 中设置微命令产生部件,根据控制信息产生微命令序列,对指令功能所要求的数据传送进行控制,同时在数据传送至运算部件时控制完成运算处理。

专题4-精简8位CPU电路设计

将9H内存的内容值加载累加器

将BH的内存内容值和累加器内容 值相加,再存放运算结果回累加器 将EH的内存内容值和累加器内容 值相减,再存放运算结果回累加器

17

零位寻址法(Zero Addressing)

指令 OUT HLT

运算码 1110 1111

范例 OUT HLT

说明

将累加器内容输出至“输出寄存 器” 结果CPU执行

CLR

display

CLR

12

CP EP LM CE LI EI LA EA SU EU LB LO

图1: SAP-1结构

2.输入与MAR(Memory Access Register)

这个方块应分成两个部分,一个是接受由“输入”部分输入到RAM内存的外部

程序和数据,另一部分“MAR”是用来在CPU执行上述所加载的程序时,暂存下一

图1: SAP-1结构

Output register

8

Binary display

LO

CLK

4

CP

CLK CLR

EP

LM

CLK

CE

Wbus

LA

Program counter

4

88 8

Accumulator A

CLK

EA

8

Input

and MAR

4

Adder/ 8 subtractor

SU EU

44

CLK

Instruction 8

LO

Output

CLR

E1

register

4

8

register

CLK

4

8

CLK

Controller/

8位CPU的设计-VHDL语言-综合性实验实验报告

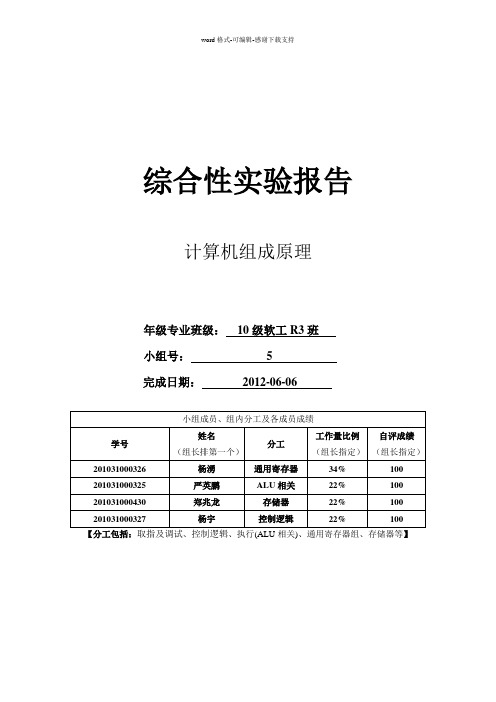

综合性实验报告计算机组成原理年级专业班级:10级软工R3班小组号: 5完成日期:2012-06-06【分工包括:、、执行(ALU相关)、通用寄存器组、存储器等】(一)实验类型:验证性+设计性(二)实验类别:综合性专业基础实验(三)实验学时数:8学时(四)实验目的理解和验证参考代码,并在其基础上,通过适当改造,尝试设计一个简单的CPU,并测试其结果。

(五)实验内容设计一个能验证计算机CPU工作原理的实验系统,包括取指部分、指令译码部分、执行部分、通用寄存器组以及存储器,并测试其结果。

(六)实验要求根本目标:缩小到8位的数据通路,也即是4位OP和4位的地址码。

(参考代码是16位数据通路,也即8位OP和8位的地址码)(参见实践报告.doc中的9-11页的指令系统总体说明)学生按照实验要求,在实验平台上实现具有存储与运算功能的计算机系统,并能通过测试,以验证其正确性。

具体要求如下:(1)取指及调试(组长兼任)。

熟悉指令取指过程,并把16位的部分改为8位。

使用DebugController和系统中的调试模块(reg_testa.vhd,reg_test.vhd)。

(2)熟悉电原理图的连接,以通用寄存器组部分为例。

实现上,用实验4所用的简单通用寄存器组(4个寄存器+1个2-4译码器+2个4选1多路开关)设计方法,替代参考代码中的通用寄存器组部分。

(3)学习和掌握控制逻辑。

设计一套指令集(可在原参考代码指令集的基础上做删减,从中选取16条基本的指令),并修改控制器中指令集的译码部分。

(4)执行部件,ALU的改造。

可在原参考代码的基础上,改变某些运算功能的实现方式,比如加、减、增1、减1等算术运算。

实现上,原参考代码采用了最少编码量的“+”、“-”号实现。

可以改用通过port map语句调用系统自带的加法器,也可以进一步自己编写加法器,然后用port map语句调用。

(5)存储器部分的加入。

原参考代码采用的带外部存储器的模式。

CPU设计实践教程8-8位7段数码管控制的设计

使用Verilog HDL实现一个1位7段数码管的编码控 制器hexseg,可以在Minisys实验板的数码管上显 示1位16进制数。

2021/9/5 P.4

实验1. 1位7段数码管控制器的设计

实验预习

请根据2.4.4节自行列出各个数字的7段数码管真值 表,并按照真值表设计7段数码管编码器。

计算机系统能力培养系列

CPU设计实践教程 ——从数电到计算机组成

数字逻辑电路实验

2021/9/5 P.1

计算机系统能力培养系列

8. 8位7段数码管控制的设计

2021/9/5 P.2

实验1. 1位7段数码管控制器的设计

实验目的

学会控制1位7段数码管的显示。

2021/9/5 P.3

实验1. 1位7段数码管控制器的设计

实验3.六十进制数字时钟的设计

实验内容

使用Verilog HDL结合实验1和实验2设计的hexseg 与hexseg8实现一个数字时钟clock60

要求能有秒、分和小时的计数与输出

用数码管A1,A0显示秒值 数码管A2,A3显示分值 数码管A4,A5显示小时 数码管A6,A7不显示。

实验目的

学会控制8位7段数码管的显示 巩固计数器的设计。

2021/9/5 P.8

实验2. 8位7段数码管控制器的设个实验设计的hexseg的改 造版本,实现一个8位十六进制数显示的数码管显 示控制模块hexseg8。

要求能同时稳定地显示各个位的数字,并能定义8 位数码管哪些位需要显示,哪些位不需要显示。( 比如要显示十六进制数0x387A6D,就只需要图2-7 中A4~A0这5位数码管显示,而A7~A5这3位不显示 )

思考与拓展

4.4.1节设计了一个8位的加法器,考虑将该加法器 的运算结果输出到数码管上。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ADD

SUB

0001

0010

ADD BH

SUB EH

零位寻址法(Zero Addressing)

指令 OUT HLT

运算码 1110 1111

范例 OUT HLT

说明

将累加器内容输出至“输出寄存 器” 结果CPU执行

范例:

• 试使用SAP-1指令,执行下列运算结果。

CP

CLK CLR

Wbus

LA

EP

Program counter

4

8 8 8

Accumulator A 8

CLK

EA

LM

CLK

Input and MAR 4 4 16*8 RAM

4

8

Adder/ subtractor 8

SU EU

CE

8

8

B register

LB

CLK

L1

CLK CLR

E1

Instruction register 4

E1

Instruction register 4

8 8 4

CLK

Output register 8

LO

CLK

Controller/ sequencer 12

CLK CLR CLR

Binary display

CP EP LM CE LI EI LA EA SU EU LB LO

图1:

SAP-1结构

1.程序计数器 它是一个4Bits的计数器,计数范围由0~15。主要功用是记录下 每个执行的指令地址,并把这个地址传送至MAR寄存器存放。

• 解答: • 首先将运算数据10,20,30,15依序放在9H-CH地址里 • 第一个指令写在0H地址,功能是先将10加载累加器,所

以指令写成: 10+20+30-15=4B(十六进制)

LDA 9H

这是因为9H存放着数值10的内容

• 第二个指令写在1H地址,功能是将20加载B寄存

器,然后与累加器里的10作相加后,再将结果 30存回累加器,所以指令写成(地址AH内存数 值20): ADD AH 第三个指令写成在2H地址,功能是将30加载B寄 存器,然后与累加器里的30作相加后,再将结 果60存回累加器,所以指令写成(地址BH内存 放数值30数据): ADD BH

8 8 4

CLK

Output register 8

LO

CLK

Controller/ sequencer 12

CLK CLR CLR

Binary display

CP EP LM CE LI EI LA EA SU EU LB LO

图1:

SAP-1结构

2.输入与MAR(Memory Access Register) 这个方块应分成两个部分,一个是接受由“输入”部分输入到RAM内存的外部 程序和数据,另一部分“MAR”是用来在CPU执行上述所加载的程序时,暂存下一 个要执行的指令地址。

8 8 4

CLK

Output register 8

LO

CLK

Controller/ sequencer 12

CLK CLR CLR

Binary display

CP EP LM CE LI EI LA EA SU EU LB LO

图1:

SAP-1结构

• 5.控制器/序列发生器

这个项目也是属于CPU内控制单元的一部分,这个控制器在程序执行时,负责送出 整个计算机的时序信号CLK,而且会把指令寄存器送来的4位指令,解译成12位的控 制信号,由这组控制信号指挥其它的功能方块,完成该指令的运作。由于使用VHDL语 言设计整个SAR-1,依照语法的使用,这部分会被省略,而且不会影响整个CPU运作。

CP

CLK CLR

Wbus

LA

EP

Program counter

4

8 8 8

Accumulator A 8

CLK

EA

LM

CLK

Input and MAR 4 4 16*8 RAM

4

8

Adder/ subtractor 8

SU EU

CE

8

8

B register

LB

CLK

L1

CLK CLR

E1

Instruction register 4

CP

CLK CLR

Wbus

LA

EP

Program counter

4

8 8 8

Accumulator A 8

CLK

EA

LM

CLK

Input and MAR 4 4 16*8 RAM

4

8

Adder/ subtractor 8

SU EU

CE

8

8

B register

LB

CLK

L1

CLK CLR

E1

Instruction register 4

8 8 4

CLK

Output register 8

LO

CLK

Controller/ sequencer 12

CLK CLR CLR

Binary display

CP EP LM CE LI EI LA EA SU EU LB LO

图1:

SAP-1结构

3.16×8 RAM 这个RAM和其它的部分构成SAP-1计算机,而且它的内存大小共有16地址×8 位。所以这个RAM的地址总线是4bit,地址编码是由0000,0001,0010…1111,这 个地址内容是由上述MAR传送过来,然后通过译码将地址存放的8位数据或指令 输出至Wbus。

CP

CLK CLR

Wbus

LA

EP

Program counter

4

8 8 8

Accumulator A 8

CLK

EA

LM

CLK

Input and MAR 4 4 16*8 RAM

4

8

Adder/ subtractor 8

SU EU

CE

8

8

B register

LB

CLK

L1

CLK CLR

E1

Instruction register 4

CP

CLK CLR

Wbus

LA

EP

Program counter

4

8 8 8

Accumulator A 8

CLK

EA

LM

CLK

Input and MAR 4 4 16*8 RAM

4

8

Adder/ subtractor 8

SU EU

CE

8

8

B register

LB

CLK

L1

CLK CLR

E1

Instruction register 4

CP

CLK CLR

Wbus

LA

EP

Program counter

4

8 8 8

Accumulator A 8

CLK

EA

LM

CLK

Input and MAR 4 4 16*8 RAM

4

8

Adder/ subtractor 8

SU EU

CE

8

8

B register

LB

CLK

L1

CLK CLR

E1

Instruction register 4

8 8 4

CLK

Output register 8

LO

CLK

Controller/ sequencer 12

CLK CLR CLR

Binary display

CP EP LM CE LI EI LA EA SU EU LB LO

图1:

SAP-1结构

7.加减法器 这个加减法器负责执行数学的加法和减法运算,而且运算的结果 会放回“累加器”暂存。

8 8 4

CLK

Output register 8

LO

CLK

Controller/ sequencer 12

CLK CLR CLR

Binary display

CP EP LM CE LI EI LA EA SU EU LB LO

图1:

SAP-1结构

8.B寄存器 这个寄存器用来配合“累加器”、“加减法器”,执行“加法” 或“减法”

8 8 4

CLK

Output register 8

LO

CLK

Controller/ sequencer 12

CLK CLR CLR

Binary display

CP EP LM CE LI EI LA EA SU EU LB LO

图1:

SAP-1结构

• 4.指令寄存器

属于CPU内的控制单元,主要是将在RAM的8位数据,通过Wbus后读入指令寄存器,然 后再把数据一分为二,较高的4位属于指令部分,送至下一级的“控制器”,而较低的4位 属于数据部分,将会被送至Wbus。

CP

CLK CLR

Wbus

LA

EP

Program counter

4

8 8 8

Accumulator A 8

CLK

EA

LM

CLK

Input and MAR 4 4 16*8 RAM

4

8

Adder/ subtractor 8

SU EU

CE

8

8

B register