正交信号发生器的设计与实现

基于MATLAB的可控DDS正交信号发生器的设计与实现

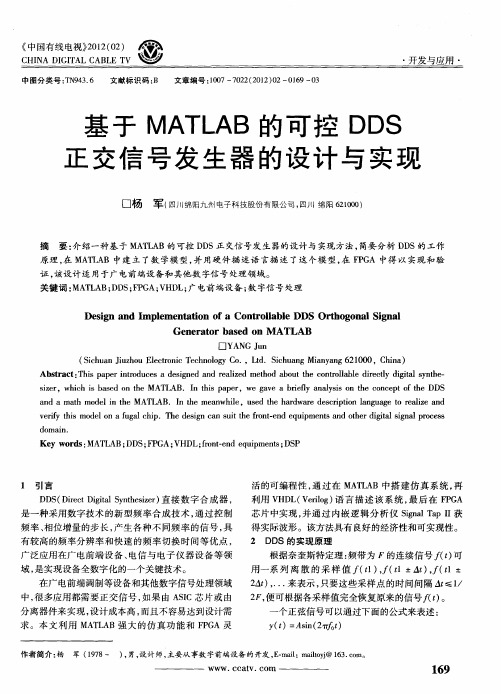

得到如图 ! 的系

统实 现 图& 其 中

主要用到加法

器* 延 时 单 元*

,i+查 找 表* 乘

法器和总线

单元)

图 !5))L 正交信号发生器 K(+,(-系统模型

=JB

中国有线电视!"#! 年第 "! 期

杨5军基于 (+,(-的可控 ))L 正交信号发生器的设计与实现

C>$"4<实现

根据 ))L 原理和 K(+,(-系统模型可以很方便

( ) <051 Y2NC< !!*"#05 7#1 Z$

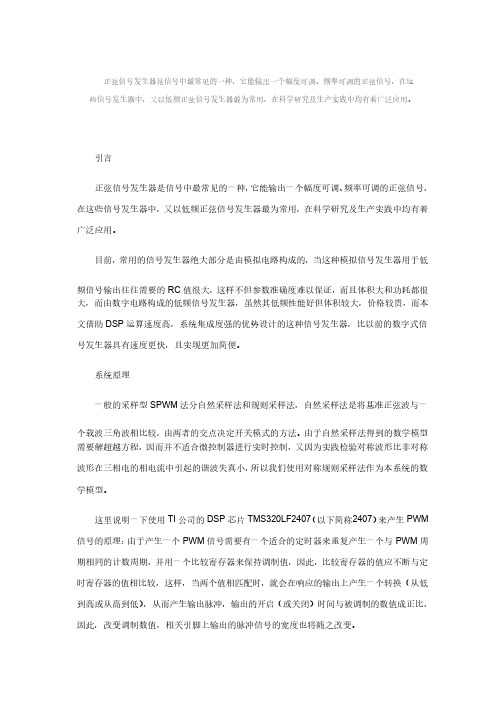

得仿真波形如图 2 所示)

由此可见&实际上需要一个 相位的累加&完全

可以由 ^X*(的 ,i+来实现这个过程)

A>;<9=<8建模

K(+,(-是一个强大的数学工具) )NOVSCPE;I是

K(+,(-中 NCTSPC<J 的一个工具箱&可以帮助设计者

地用硬件描述语言把这个系统描述出来 从图 ! 中可

图 25K(+,(-仿真图

由 ! 块 ,i+表

组成& 分 别 存 放

着正弦和余弦函

数的 采 样 值& 采

样值可以由

K(+,(- 工 具

函数 得 到& 其 查

找表的地址就是

相位累加的结

果&原 理 框 图 如

图 # 所示)

在 K(+,(-

中& 调 用 )NO?

VSCPE;I工 具 栏

中相 应 的 模 块&

! 中国有线电视"!"#!#"!$ $%&'()&*&+(,$(-,.+/

基于MATLAB的可控DDS正交信号发生器的设计与实现

D S Drc ii y tei r 直 接数 字 合 成 器 , D ( i t gt S nh s e ) e D a l z

是 一种 采用 数 字技 术 的新 型频 率 合 成 技 术 , 过 控 制 通 频 率 、 位 增量 的步 长 , 生 各 种 不 同频 率 的信 号 , 相 产 具

2 t… . A) 来表 示 , 只要 这 些采 样 点 的 时 间 间隔 ≤l /

在广 电前端调制等设备和其他数字信号处理领域

中 , 多应 用 都需 要 正 交信 号 , 果 由 A I 片或 由 很 如 SC芯 分离 器件 来 实现 , 设计 成本 高 , 而且 不容 易达 到设 计需 求 。本 文 利 用 MA L B强 大 的仿 真 功 能 和 F G 灵 TA PA

sz r ie ,wh c s b s d o h ih i a e n t e MAT LAB.I h s p p r n t i a e ,we g v re y a ay i n t o c p f t a e a b i f n l ss o he c n e to he DDS l a d a ma h mo li h n t de n te MATL AB.I he me n ie,us d t e ha d r s rp in l n u g o r aie a d n t a wh l e h r wa e de c i to a g a e t e z n l v rf h s mo e n a f g lc i e y t i d lo u a hp. i d man. o i e d sg a u tt e fo te d e u p n sa t e i i in lp o e s e in c n s i h r n — n q i me t nd o h rd gt sg a r c s l a

双路正交IQ信号发生器

课程设计报告课程设计题目:双路正交IQ信号发生器学院:专业:通信工程班级:姓名:学号:指导老师:2011年07月08日摘要电子线路中,在无需外加激励信号的情况下,能将直流电能转换成具有一定波形、一定频率和一定幅度的交变能量的电子电路称为信号发生器。

本课程设计中要求实现一频率为10Mhz的信号源,故为高频信号发生器。

高频信号发生器主要是产生高频正弦震荡波,电路主要由高频振荡电路构成。

振荡器是一种能自动地将直流电源能量转换为一定波形的交变振荡信号能量的转换电路。

它无需外加激励信号。

常用正弦波振荡器主要由决定振荡频率的选频网络和维持振荡的正反馈放大器组成,这就是反馈振荡器。

按照选频网络所采用元件的不同,正弦波振荡器可分为LC振荡器、RC振荡器和晶体振荡器等类型。

其中LC振荡器和晶体振荡器用于产生高频正弦波。

正反馈放大器既可以由晶体管、场效应管等分立器件组成,也可以由集成电路组成。

根据所产生的波形不同,可将振荡器分成正弦波振荡器和非正弦波振荡器两大类。

前者能产生正弦波,后者能产生矩形波、三角波、锯齿波等。

使用运算放大器组成的微分电路可实现正弦波相移90度,产生余弦波,两路信号形成双路正交信号。

在本课程设计中,着眼于无线电通信的基础电路——LC正弦振荡器的分析和研究。

通过对电容反馈式三端振荡器以及改进型电容反馈式振荡器(西勒电路)的分析、对比和讨论。

以求得到一些对实际应用电路有帮助的结论。

在课程设计中,使用的仿真软件为protel99se。

该软件提供了功能强大的电子仿真设计界面和方便的电路图和文件管理功能。

能够让使用者全面的收集电路的相关数据,进而有助于对电路进行改进。

总体来说,课程设计中所涉及的仿真电路是比较简单的。

但通过仿真得到的结论在实际的类似电路中有很普遍的意义。

本设计最终选用西勒振荡器。

目录第一章设计要求与总体框图1.1 设计目的 (3)1.2 题目要求 (3)1.3 设计总体框图 (3)第二章各部分设计方案及工作原理2.1 LC正弦波振荡部分 (4)2.1.1 LC三点式振荡器相位平衡条件的判断准则 (4)2.1.2 电容三点式振荡器 (4)2.1.3西勒振荡器 (5)2.2 相位调整网路部分 (8)2.3总体设计及仿真 (10)第三章结论 (11)第四章展望 (12)第五章致谢 (12)第六章参考文献 (12)第一章设计要求与总体框图1.1 设计目的(1)了解通信系统功能模块电路的工作原理(2)熟悉通信系统功能电路的设计方法(3)掌握利用仿真软件对电路功能进行分析(4)学会通信电路的器件选型,参数调节,功能测试1.2 题目要求1 基于LC振荡器设计一频率为10Mhz的信号源,并利用相位调整网络获得双路正交信号。

基于延时移相正交信号发生器的锁相环建模方法及系统

基于延时移相正交信号发生器的锁相环建模方法及系统锁相环(PLL)是一种常见的电路,用于将输入信号与本地参考信号同步。

其中,延时移相正交信号发生器(DDS)是一种常用的数字信号发生器,可以产生高精度的正弦波信号。

本文将介绍一种基于DDS的PLL建模方法及系统。

一、建模方法1. PLL的基本原理PLL的基本原理是将输入信号与本地参考信号进行比较,然后根据比较结果调整本地参考信号的相位和频率,使其与输入信号同步。

PLL通常由相位检测器(PD)、环路滤波器(LPF)、控制电压发生器(VCO)和反馈电路组成。

2. DDS的基本原理DDS是一种数字信号发生器,可以通过数字控制产生高精度的正弦波信号。

DDS的基本原理是将一个参考时钟信号与一个数字控制字相乘,得到一个数字信号,再通过数字滤波器和DAC转换成模拟信号输出。

DDS的优点是精度高、频率稳定,可以实现高速、高精度的信号产生。

3. 基于DDS的PLL建模方法基于DDS的PLL建模方法是将DDS作为VCO的替代品,将输入信号与DDS产生的正弦波信号进行比较,然后通过相位检测器和环路滤波器控制DDS的数字控制字,使其产生与输入信号同步的正弦波信号。

二、系统实现基于DDS的PLL系统实现主要包括DDS模块、相位检测器模块、环路滤波器模块和反馈电路模块。

1. DDS模块DDS模块主要包括数字控制字生成器、数字滤波器和DAC模块。

数字控制字生成器根据输入的频率和相位信息产生相应的数字控制字,数字滤波器对数字控制字进行滤波,DAC模块将滤波后的数字信号转换成模拟信号输出。

2. 相位检测器模块相位检测器模块将输入信号和DDS产生的正弦波信号进行比较,得到相位误差信号。

常用的相位检测器有边沿触发型、环路型和乘法型等。

3. 环路滤波器模块环路滤波器模块对相位误差信号进行滤波,得到控制电压信号。

常用的环路滤波器有积分型、比例积分型和低通滤波器等。

4. 反馈电路模块反馈电路模块将控制电压信号送回DDS模块,控制DDS的数字控制字,实现DDS的频率和相位的调整,使其与输入信号同步。

正交信号发生器

case 3:Tx = 2;

break;

}

gotob;

a:switch(Tx)

{

case 0:Tx = 2;

break;

case 1:Tx = 0;

break;

case 2:Tx = 3;

break;

case 3:Tx = 1;

break;

}ቤተ መጻሕፍቲ ባይዱ

b:P1 = Tx;

//Count++;

TH1 = 0x3c;

3、改变Count(根据KEY的状况加或减)。

4、Count%=4(求余数);

C语言程序:#include<reg51.h>

#define uchar unsigned char

void main()

{

TH1 = 0x3c;

TL1 = 0xb0;

TMOD = 0x10;

//TCON = 0x40;

EA = 1;

超前90°:

P1.0超前:P1口依次循环输出00H→01H→03H→02H→…

P1.1超前:P1口依次循环输出00H→02H→03H→01H→…

定时中断服务程序处理:

1、重置定时时间常数。

2、根据当前Count(Count为一个波形周期内的等分时段计数,值为0~3。既上图中的Tx)查表(表中的值见 )获取当前时段P1的输出值。

正交信号发生器

一、任务

在P1.0和P1.1输出如下图的正交信号(P1.0超前90°),硬件电路参见Orthogonal.DSN)。当KEY按下时,波形改变成P1.1超前90°。

二、设计参考:

三、 正交波形产生:

在一个波形周期内可分成四个等分时段,每个时段用相同时间的定时来实现,定时时间可设为50ms。

基于DSP Builder租DDS的正交信号发生器的设计

基于D P udr D 的 S ie租D S 正交信号发生 设计 Bl 器的

李攀峰 , 紫婷 王

( 兰州交通 大学 电子与信 息工程 学院 ,甘 肃 兰州 7 07 ) 300

摘 要: 简要 分 析 了直接 数 字频 率 合 成 技 术 的概 念 、优 点 和 应 用 , 阐述 了 D S工 作 的 基 本 原 理 和 利 用 D

直 接 数 字 频 率合 成 ( i c Dg a Feuny Dr t i t r ec e il q Sn ei yt s )技术是一种新型的频率合成技术和信号 h s 产生方法 _ 1 1 电路系统具有频率分辨率高 、频率 。其 转换时间短 、控制灵活和全数字化 的优点 。由于其

系统 时钟

图 1 DD S基 本 结构

Байду номын сангаас

D S D 的核心 是相 位 累加器 , 由一个 Ⅳ位 字长 的

基 本 D S结 构 中增 加 一 块 R M 查 找 表 .在 两 块 D O

二进制加法器和一个 由时钟 c 采样 的 Ⅳ位寄存器 l k 组成 ,作用是对频率控制字进行线性累加 ;波形存

= / 秒的间隔对它进行采样 ,则此信号f()可 1c f £ 以由其采样值完全恢复过来网 D 正是基于这一 。D S 理 论 ,将 一 个 经 过 对 原 始 信 号 进 行 采 样 的 阶 梯 信

号 ,通 过低 通滤 波器完 全恢 复 。一个 典型 的 D S D 组 成如 图 1 示 ( 所 以正 弦波 为例 )[ 1 1 。

的相位码值 输 出不 同的 幅度编码 。该 幅度编 码经

DA转化 后 得 到对应 的阶梯 波 ,最 后 经低 通 滤波 器 /

平滑后 可得 到所 需 的模 拟 波形 2 利 用 DS ule 设计 正 交信号 发生 器 PB i r d

正交信号发生器的FPGA设计与仿真

正交信号发生器的FPGA设计与仿真雷能芳【期刊名称】《价值工程》【年(卷),期】2011(030)024【摘要】The common approach to implement orthogonal signal generator on FPGA is based on look-up tables, which require a huge volume of ROM to achieve high resolution. This paper proposes a pipelined architecture for implementation of orthogonal signal generator on FPGA, which, based on CORDIC algorithm, can save considerable hardware resources and improve the speed performance as well. According to advantages of DSP Builder, the system is designed by utilizing VHDL and Simulink module. The correctness and feasibility of this design is verified by simulation result.%正交信号发生器的FPGA实现通常都是基于查找表的方法,为了达到高精度要求,需要耗费大量的ROM资源去建立庞大的查找表.文中提出了一种基于流水线CORDIC 算法的实现方案,可有效地节省FPGA的硬件资源.并根据DSP开发工具DSP Builder的优点,采用VHDL文本与Simulink模型图相结合的方法进行了FPGA设计,仿真结果验证了设计的正确性及可行性.【总页数】2页(P140-141)【作者】雷能芳【作者单位】渭南师范学院,渭南714000【正文语种】中文【中图分类】TP391.9【相关文献】1.基于FPGA的正交信号发生器设计 [J], 杨峰;文枰2.正交幅度调制解调器的FPGA设计与仿真 [J], 雷能芳3.基于FPGA的正交信号发生器 [J], 郝小江4.多模态信号发生器设计与仿真 [J], 雷红;黄懿赟;潘圣民;陆伟5.一种频率占空比独立可调的PWM信号发生器的设计与仿真 [J], 盛奋华因版权原因,仅展示原文概要,查看原文内容请购买。

基于DSP的正弦信号发生器设计(参考)

正弦信号发生器是信号中最常见的一种,它能输出一个幅度可调、频率可调的正弦信号,在这些信号发生器中,又以低频正弦信号发生器最为常用,在科学研究及生产实践中均有着广泛应用。

引言引言正弦信号发生器是信号中最常见的一种,它能输出一个幅度可调、频率可调的正弦信号,在这些信号发生器中,又以低频正弦信号发生器最为常用,在科学研究及生产实践中均有着广泛应用。

广泛应用。

目前,常用的信号发生器绝大部分是由模拟电路构成的,当这种模拟信号发生器用于低频信号输出往往需要的RC 值很大,这样不但参数准确度难以保证,而且体积大和功耗都很大,而由数字电路构成的低频信号发生器,虽然其低频性能好但体积较大,大,而由数字电路构成的低频信号发生器,虽然其低频性能好但体积较大,价格较贵,价格较贵,价格较贵,而本而本文借助DSP 运算速度高,系统集成度强的优势设计的这种信号发生器,比以前的数字式信号发生器具有速度更快,且实现更加简便。

号发生器具有速度更快,且实现更加简便。

系统原理系统原理一般的采样型SPWM 法分自然采样法和规则采样法,自然采样法是将基准正弦波与一个载波三角波相比较,由两者的交点决定开关模式的方法。

由于自然采样法得到的数学模型需要解超越方程,因而并不适合微控制器进行实时控制,又因为实践检验对称波形比非对称波形在三相电的相电流中引起的谐波失真小,所以我们使用对称规则采样法作为本系统的数学模型。

学模型。

这里说明一下使用TI 公司的DSP 芯片TMS320LF2407(以下简称2407)来产生PWM 信号的原理:由于产生一个PWM 信号需要有一个适合的定时器来重复产生一个与PWM 周期相同的计数周期,并用一个比较寄存器来保持调制值,并用一个比较寄存器来保持调制值,因此,因此,比较寄存器的值应不断与定时寄存器的值相比较,这样,当两个值相匹配时,时寄存器的值相比较,这样,当两个值相匹配时,就会在响应的输出上产生一个转换(从低就会在响应的输出上产生一个转换(从低到高或从高到低),从而产生输出脉冲,输出的开启,从而产生输出脉冲,输出的开启(或关闭)(或关闭)(或关闭)时间与被调制的数值成正比,时间与被调制的数值成正比,因此,改变调制数值,相关引脚上输出的脉冲信号的宽度也将随之改变。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

正交信号发生器的设计与实现

马胜前

【期刊名称】《西北师范大学学报(自然科学版)》

【年(卷),期】2006(042)006

【摘要】描述了基于AT89C52单片机、锁相环和开关电容滤波器的正交信号发生器的设计和实现方法.单片机产生方波,通过数字接口实现相位差为90°的方波,再通过两个8阶BUTTERWORTH低通开关电容滤波器MAX295对双路方波进行滤波,从而产生正交的正弦波.MAX295的时钟由锁相环倍频产生.采用连续时间滤波器抑制采样时钟的影响.频率覆盖范围0.1~20 kHz.频率和相位误差小于1%.【总页数】3页(P31-33)

【作者】马胜前

【作者单位】西北师范大学,物理与电子工程学院,甘肃,兰州,730070

【正文语种】中文

【中图分类】TN713;TP368.1

【相关文献】

1.基于正交信号发生器的单相锁相环的研究 [J], 陈红兵;闵晶妍

2.单相αβPLL方案中正交信号发生器的性能比较 [J], 贝太周;王萍;张博文

3.基于FPGA的正交信号发生器设计 [J], 杨峰;文枰

4.基于MATLAB的可控DDS正交信号发生器的设计与实现 [J], 杨军

5.具有精确幅值积分特性的正交信号发生器 [J], 孙于;李雪;耿嘉一;吴尚

因版权原因,仅展示原文概要,查看原文内容请购买。