习题1-门电路和组合逻辑电路

数字电子技术基础课-阎石-第五版第四章期末复习题

组合逻辑电路习题一、填空、选择1、8 线—3线优先编码器74LS148 的优先编码顺序是I7 、I6 、I5 、…、I0 ,输出A2 A1 A0 。

输入输出均为低电平有效。

当输入I7 I6 I5 …I0 为11010101时,输出A2 A1 A0为 。

2、3 线—8 线译码器74LS138 处于译码状态时,当输入A 2A 1A 0=001 时,输出Y 7~Y 0 = 。

3、组合逻辑电路任何时刻的输出信号,与该时刻的输入信号 ,与电路以前的状态 。

4、在组合逻辑电路中,由于门电路的延时,当输入信号状态改变时,输出端可能出现虚假过渡干扰脉冲的现象称为 。

5、一位数值比较器,输入信号为两个要比较的一位二进制数A 、B ,输出信号为比较结果:Y(A >B)、Y(A =B)和Y(A <B),则Y(A >B)的逻辑表达式为 。

6、下列电路中,不属于组合逻辑电路的是。

(A )译码器 (B )全加器 (C )寄存器 (D )编码器 7、在二进制译码器中,若输入有4位代码,则输出有 个信号。

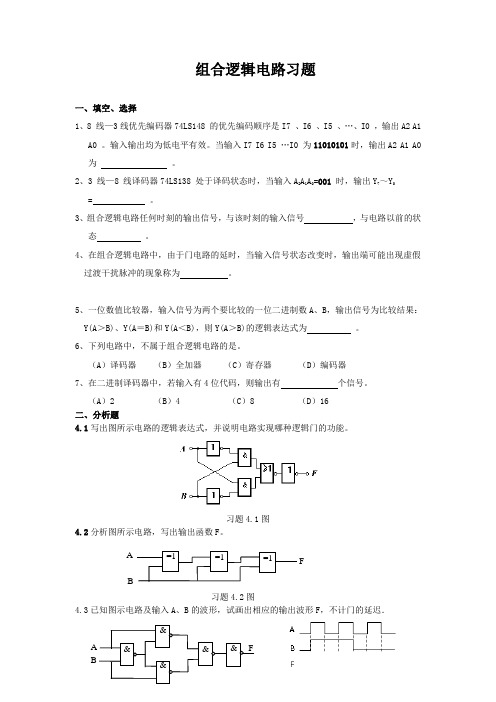

(A )2 (B )4 (C )8 (D )16 二、分析题4.1写出图所示电路的逻辑表达式,并说明电路实现哪种逻辑门的功能。

习题4.1图4.2分析图所示电路,写出输出函数F 。

习题4.2图4.3已知图示电路及输入A 、B 的波形,试画出相应的输出波形F ,不计门的延迟.B A =1 =1 =1F习题4.3图4.4由与非门构成的某表决电路如图所示。

其中A 、B 、C 、D 表示4个人,L=1时表示决议通过。

(1) 试分析电路,说明决议通过的情况有几种。

(2) 分析A 、B 、C 、D 四个人中,谁的权利最大。

4.5分析图所示逻辑电路,已知S 1﹑S 0为功能控制输入,A ﹑B 为输入信号,L 为输出,求电路所具有的功能。

习题4.5图4.6试分析图所示电路的逻辑功能。

习题4.6图4.7已知某组合电路的输入A 、B 、C 和输出F 的波形如下图所示,试写出F 的最简与或表达式。

门电路功能测试及组合逻辑电路设计

实验报告门电路功能测试及组合逻辑电路设计实验题目:门电路功能测试及组合逻辑电路设计实验目的:(1)掌握常用门电路的逻辑功能及测试方法;(2)掌握用小规模集成电路设计组合逻辑电路的方法。

实验仪器及器材:数字电路实验箱一个;双踪示波器一台;稳压电源一台;数字万用表一个。

74LS00一片;74LS10一片;74LS20一片。

实验内容:实验一:对74LS00进行功能测试○1.静态测试A B F0 0 10 1 11 0 11 1 0(1)A、B都为低电平,输出结果为高电平(2)A为低电平,B为高电平或A为高电平,B为低电平时,输出结果为高电平(3)A、B均为高电平,输出结果为低电平实验结论:测试结果与74LS00逻辑功能功能表相同。

○2动态测试电路的逻辑表达式:F=ˉVK分析:当K为0时,示波器的A通道是V的波形,为方波信号,B通道是F的波形,为高电平(一条直线);当开关闭合后,K=1,B通道应该是与V波形刚好相反的波形;小灯泡也是一闪一闪的状态。

实验的电路图实验现象:开关断开:示波器的显示:开关闭合后,小灯泡开始一闪一闪,示波器波形如下图:现象分析:实验所得现象与预先分析的实验结果一样。

比较输入与输出的波形,发现输出F的波形与V的波形刚好相反,但是F波形的最大值较V的最大值偏小,究其原因,这属于正常现象,因为输出会有损失。

实验结论:所得到的波形符合功能要求。

实验2实验目的:分析一个电路的逻辑功能实验器材:74LS00、74LS10各一片实验原理分析:F=AB*BC*AC,所以F的结果应为以下表格:A B C F0 0 0 00 0 1 00 1 0 00 1 1 11 0 0 01 0 1 11 1 0 11 1 1 1实验结论:实验结果与预期的一样,符合该电路的逻辑功能表达式实验三实验目的:设计一个控制楼梯电灯的开关控制器,逻辑功能为课本表2-1-5的真值表。

实验原理分析:根据电路所实现的真值表,可以得出输出Y的逻辑表达式:Y=AB*AB实验电路及现象:1.A=1,B=0;A=0,B=1,时灯泡发光;2.A=B=0或1时,灯泡不发光实验结论:该电路可以实现题目要求的功能,即课本表2-1-5的真值表。

门电路和组合逻辑电路

-U

(2) 工作原理 12V

“或” 门逻辑状态表

A B CY

00 00 01 01 10 10 11 11

00 11 01 11 01 11 01 11

输入A、B、C有一个为“1”,输出 Y 为“1”。

输入A、B、C全为低电平“0”,输出 Y 为“0”。

2021/7/17

6

2. 或门电路

逻辑表达式: Y=A+B+C

2021/7/17

2

电平的高低

UCC

一般用“1”和

“0”两种状态

区别,若规定

高电平为“1”,

低电平为“0”

则称为正逻辑。

反之则称为负 逻辑。若无特 0V

殊说明,均采

用正逻辑。

2021/7/17

高电平 1

低电平 0

3

1. 与 门电路

(1) 电路

03V A

DA

DB

03V B

03V C

DC

+U 12V R

在数字电路中,常用的组合电路有加法器、 编码器、译码器、数据分配器和多路选择器 等。下面几节分别介绍这几种典型组合逻辑 电路的使用方法。

2021/7/17

38

加法器

二进制

十进制:0~9十个数码,“逢十进一”。 在数字电路中,为了把电路的两个状态 (“1”

态和“0”态)与数码对应起来,采用二进制。 二进制:0,1两个数码,“逢二进一”。

26

12. 2. 2 组合逻辑电路的设计

根据逻辑功能要求 设计 逻辑电路

设计步骤如下: (1) 由逻辑要求,列出逻辑状态表 (2) 由逻辑状态表写出逻辑表达式 (3) 简化和变换逻辑表达式 (4) 画出逻辑图

(完整版)第20章习题1-门电路与组合逻辑电路

第20章习题 门电路和组合逻辑电路S10101B为实现图逻辑表达式的功能,请将TTL 电路多余输入端C 进行处理(只需一种处理方法),Y 1的C 端应接 ,Y 2的C 端应接 ,解:接地、悬空S10203G在F = AB +CD 的真值表中,F =1的状态有( )。

A. 2个 B. 4个 C. 3个 D. 7个 解:DS10203N某与非门有A 、B 、C 三个输入变量,当B =1时,其输出为( )。

A. 0 B. 1 C. AC D. AC 解:CS10204B在数字电路中,晶体管的工作状态为( )。

A. 饱和 B. 放大 C. 饱和或放大 D. 饱和或截止 解:DS10204I逻辑电路如图所示,其逻辑函数式为( )。

A. B A B A +B. AB B A +C. B A B A +D. A AB + 解:CS10204N已知F =AB +CD ,选出下列可以肯定使F = 0的情况( )。

A. A = 0,BC = 1 B. B = C = 1 C. C = 1,D = 0 D. AB = 0,CD = 0 解:DS10110B三态门电路的三种可能的输出状态是 , , 。

解:逻辑1、逻辑0、高阻态1&B1&≥1逻辑图和输入A ,B 的波形如图所示,分析当输出F 为“1”的时刻应是( )。

A. t 1B. t 2C. t 3解:AS10211I图示逻辑电路的逻辑式为( )。

A. F =A B AB +B. B A AB F =C. F =()A B AB + 解:BS10212I逻辑电路如图所示,其功能相当于一个( )。

A. 门B. 与非门C. 异或门 解:CS10216B图示逻辑电路的逻辑式为( )。

A. F =A B +A BB. F =AB AB +C. F =AB +A B 解:CS10217B逻辑图如图(a )所示,输入A 、B 的波形如图(b ),试分析在t 1瞬间输出F 为( )。

基础知识一基本逻辑门电路习题精选全文完整版

可编辑修改精选全文完整版基础知识一 基本逻辑门电路习题一、填空题1、模拟信号的特点是在 和 上都是 变化的。

(幅度、时间、连续)2、数字信号的特点是在 和 上都是 变化的。

(幅度、时间、不连续)3、数字电路主要研究 与 信号之间的对应 关系。

(输出、输入、逻辑)4、用二进制数表示文字、符号等信息的过程称为_____________。

(编码)5、()11011(2= 10),()1110110(2= 8),()21(10= 2)。

(27、166、10101) 6、()101010(2= 10),()74(8= 2),()7(16=D 2)。

(42、111100、)7、最基本的三种逻辑运算是 、 、 。

(与、或、非)8、逻辑等式三个规则分别是 、 、 。

(代入、对偶、反演)9、逻辑函数化简的方法主要有 化简法和 化简法。

(公式、卡诺图)10、逻辑函数常用的表示方法有 、 和 。

(真值表、表达式、卡诺图、逻辑图、波形图五种方法任选三种即可)11、任何一个逻辑函数的 是唯一的,但是它的 可有不同的形式,逻辑函数的各种表示方法在本质上是 的,可以互换。

(真值表、表达式、一致或相同) 12、写出下面逻辑图所表示的逻辑函数Y= 。

(C B A Y )(+=)13、写出下面逻辑图所表示的逻辑函数Y= 。

())((C A B A Y ++=)14、半导体二极管具有 性,可作为开关元件。

(单向导电)15、半导体二极管 时,相当于短路; 时,相当于开路。

(导通、截止) 16、半导体三极管作为开关元件时工作在 状态和 状态。

(饱和、截止)二、判断题1、十进制数74转换为8421BCD 码应当是BCD 8421)01110100(。

(√)2、二进制只可以用来表示数字,不可以用来表示文字和符号等。

(╳)3、十进制转换为二进制的时候,整数部分和小数部分都要采用除2取余法。

(╳)4、若两个函数相等,则它们的真值表一定相同;反之,若两个函数的真值表完全相同,则这两个函数未必相等。

门电路和组合逻辑电路 练习题

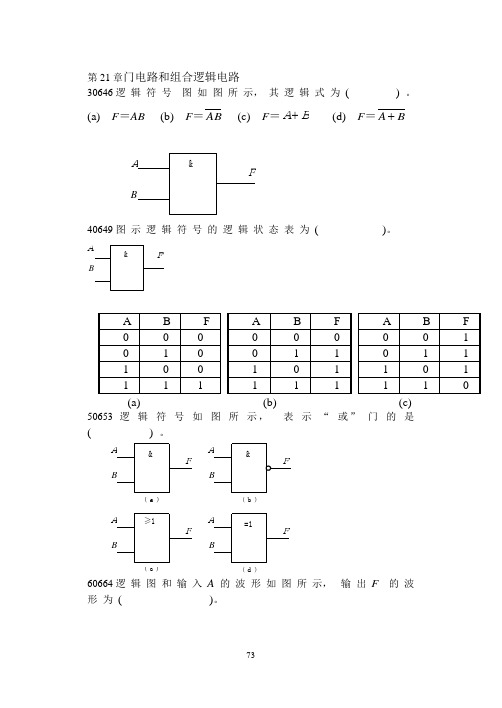

第21章门电路和组合逻辑电路30646逻 辑 符 号 图 如 图 所 示, 其 逻 辑 式 为 ( ) 。

(a) F =AB (b) F =AB (c) F =A B +(d) F =A B +40649图 示 逻 辑 符 号 的 逻 辑 状 态 表 为 ( )。

&A FB50653逻 辑 符 号 如 图 所 示, 表 示 “ 或” 门 的 是( ) 。

&AFB≥1AFB&A FB=1A FB()a ()b ()c ()d60664逻 辑 图 和 输 入 A 的 波 形 如 图 所 示, 输 出 F 的 波 形 为 ( )。

"0"1AF()a ()b (c)AFF90707在 正 逻 辑 条 件 下, 如图 所 示 逻 辑 电 路 为( ) 。

(a)“ 与 非” 门 (b) “ 与” 门(c) “ 或” 门(d) “ 或 非” 门AB CF100735下 列 逻 辑 式 中,正 确 的逻 辑 公 式 是( )。

(a) A =1(b)A =0(c)A =A110754逻 辑 式F =A B +B D+A B C +AB C D ,化 简 后 为( )。

(a) F =AB BC +(b)F =A B +C D (c) F =A B + B D120758逻 辑 式F =A BC +ABC +A B C ,化 简 后 为( )。

(a) F =A B +B C(b) F =A C +AB (c) F =A C +BC130766图 示 逻 辑 电 路 的 逻 辑 式 为( )。

(a) F =AB C +(b)F =()A B C +(c)F =AB +C&≥1FAB C140772图 示 逻 辑 电 路的 逻 辑 式 为( )。

(a) F = AB A B ()+ (b) F =AB ()AB(c) F =()A B AB +150791逻 辑 图 和 输 入A ,B 的 波 形 如 图 所 示, 分 析 当 输 出 F 为“1”的 时 刻 应 是( )。

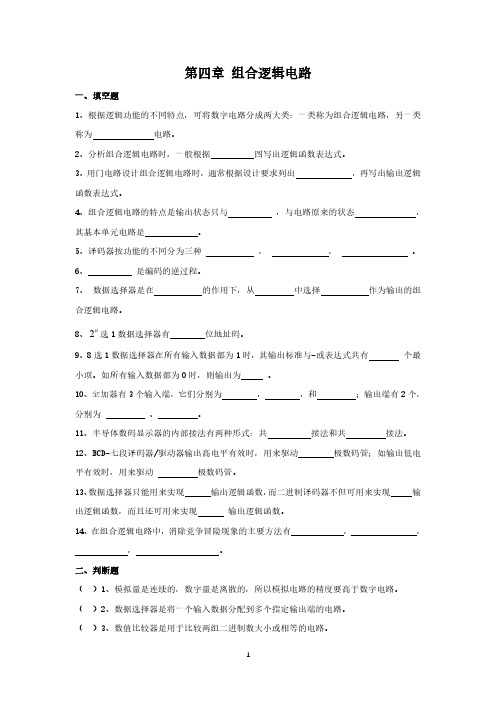

第四章组合逻辑电路习题

第四章组合逻辑电路一、填空题1、根据逻辑功能的不同特点,可将数字电路分成两大类:一类称为组合逻辑电路,另一类称为电路。

2、分析组合逻辑电路时,一般根据图写出逻辑函数表达式。

3、用门电路设计组合逻辑电路时,通常根据设计要求列出,再写出输出逻辑函数表达式。

4、组合逻辑电路的特点是输出状态只与,与电路原来的状态,其基本单元电路是。

5、译码器按功能的不同分为三种,,。

6、是编码的逆过程。

7、数据选择器是在的作用下,从中选择作为输出的组合逻辑电路。

8、2n选1数据选择器有位地址码。

9、8选1数据选择器在所有输入数据都为1时,其输出标准与-或表达式共有个最小项。

如所有输入数据都为0时,则输出为。

10、全加器有3个输入端,它们分别为,,和;输出端有2个,分别为、。

11、半导体数码显示器的内部接法有两种形式:共接法和共接法。

12、BCD-七段译码器/驱动器输出高电平有效时,用来驱动极数码管;如输出低电平有效时,用来驱动极数码管。

13、数据选择器只能用来实现输出逻辑函数,而二进制译码器不但可用来实现输出逻辑函数,而且还可用来实现输出逻辑函数。

14、在组合逻辑电路中,消除竞争冒险现象的主要方法有,,,。

二、判断题()1、模拟量是连续的,数字量是离散的,所以模拟电路的精度要高于数字电路。

()2、数据选择器是将一个输入数据分配到多个指定输出端的电路。

()3、数值比较器是用于比较两组二进制数大小或相等的电路。

()4、优先编码器只对多个输入编码信号中优先权最高的信号进行编码。

()5、加法器是用于对两组二进制数进行比较的电路。

()6、具有记忆功能的电路不是组合逻辑电路。

()7、译码器的作用就是将输入的二进制代码译成特定的信号输出。

()8、全加器只用于对两个一位二进制数相加。

()9、数据选择器根据地址码的不同从多路输入数据中选择其中一路输出。

()10、在任何时刻,电路的输出状态只取决于该时刻的输入,而与该时刻之前的电路状态无关的逻辑电路,称为组合逻辑电路。

电工学第14章 门电路和组合逻辑电路

14.1 逻辑代数

逻辑代数运算规则

逻辑代数又称布尔代数,是分析与设计 逻辑电路的工具。逻辑代数表示的是逻辑关 系,它的变量取值只有1和0,表示两个相反 的逻辑关系。

2 逻辑函数的表示方法

逻辑状态表:列出输入、输出变量的所有逻辑状态

逻辑式:用基本运算符号列出输入、输出变量间 的逻辑代数式

逻辑图: 用逻辑符号表示输入、输出变量间的逻 辑关系

卡诺图:与变量的最小项对应的按一定规则排列 的方格图

最小项是指所有输入变量各种组合的乘积项,输入变量

包括原变量和反变量。例如,二变量A,B的最小项有四项:

选取原则是:● 这些乘积项应包含函数式中所有的最小项

● 所用的乘积项数目最少 ● 每个乘积项包含的因子最少

[例题1.3.4] 用卡诺图化简法将下式化简为最简与—

或函数式 Y = AC + AC + BC + BC

解:● 画出函数Y的卡诺图

对应 AC 项:

BC A

00

AC

01 11

10

00 1 1 1

基本运算有: 乘(与)运算、加(或) 运算、求反(非)运算。

1.基本运算规则

A+0=A , A+1=1 , A • 0=0 A • 1=A , A+A=1 , A+A=A A • A=0 , A • A=A , A=A

2.逻辑代数的基本定律

交换律:A+B=B+A , A • B=B • A 结合律:A+(B+C)=(A+B)+C

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第20章习题 门电路和组合逻辑电路S10101B为实现图逻辑表达式的功能,请将TTL 电路多余输入端C 进行处理(只需一种处理方法),Y 1的C 端应接 ,Y 2的C 端应接 ,解:接地、悬空S10203G在F = AB +CD 的真值表中,F =1的状态有( )。

A. 2个 B. 4个 C. 3个 D. 7个 解:DS10203N某与非门有A 、B 、C 三个输入变量,当B =1时,其输出为( )。

A. 0 B. 1 C. D. AC 解:CS10204B在数字电路中,晶体管的工作状态为( )。

A. 饱和 B. 放大 C. 饱和或放大 D. 饱和或截止 解:DS10204I逻辑电路如图所示,其逻辑函数式为( )。

A. B.C. D.解:CS10204N已知F =AB +CD ,选出下列可以肯定使F = 0的情况( )。

A. A = 0,BC = 1 B. B = C = 1 C. C = 1,D = 0 D. AB = 0,CD = 0 解:DS10110B三态门电路的三种可能的输出状态是 , , 。

解:逻辑1、逻辑0、高阻态S10214B逻辑图和输入A ,B 的波形如图所示,分析当输出F 为“1”的时刻应是( )。

A. t 1B. t 2C. t 3解:AYS10211I图示逻辑电路的逻辑式为( )。

A. B. C. 解:BS10212I逻辑电路如图所示,其功能相当于一个( )。

A. 门B. 与非门C. 异或门 解:CS10216B图示逻辑电路的逻辑式为( )。

A. A +BB.C. AB + 解:CS10217B逻辑图如图(a )所示,输入A 、B 的波形如图(b ),试分析在t 1瞬间输出F 为( )。

A. “1”B. “0”C. 不定 解:BS10218B图示逻辑符号的逻辑状态表为( )。

A. B. C.解:BS10219B逻辑图和输入A的波形如图所示,输出F的波形为( )。

解:(b)S10220B图示逻辑符号的状态表为( )。

解:CS10221B逻辑图和输入A,B的波形如图所示,分析当输出F为“1”的时刻,应是( )。

A.t1B.t2C.t3解:AS10225B逻辑门电路的逻辑符号如图所示,能实现F=AB逻辑功能的是( )。

解:(a)S10214I逻辑图和输入A,B的波形如图所示,分析当输出F为的时刻应是( )。

A.t1B.t2C.t3解:CS10217I图示逻辑电路的逻辑式为( )。

A.B.C.解:AS10221I逻辑图和输入A,B的波形如图所示,分析当输出F为“0”的时刻应是( )。

A. t1B. t2C. t3解:CS10222I逻辑图和输入A,B的波形如图所示,分析当输出F为“0”的时刻应是( )。

A. t1B. t2C. t3解:BS10226B三态输出“与非”门电路的输出比正常的“与非”门电路多一个状态是( )。

A. 高电平B. 低电平C. 高阻解:CS10229B逻辑图和输入A,B的波形如图所示,分析当输出F为“1”的时刻应是( )。

A.t1B.t2C.t3解:CS10209B逻辑符号如图所示,其中表示“与非”门的是( )。

解:(d)S10210B“异或”门的逻辑式为( )。

A. F=AB+ABB. F=+ABC. F=解:CS10223I图示逻辑电路的逻辑式为( )。

A.B.C.解:A已知各逻辑门输入A、B和输出F的波形如下图所示,要求写出F的逻辑表达式,并画出逻辑电路。

解S10503B写出如图所示电路的输出函数Y的表达式,并分析逻辑功能。

解:逻辑函数Y的表达式Y= 1,否则Y= 0。

即该电路具有“判一致”的逻辑功能。

S10504B证明图(a)、(b)两电路具有相同的逻辑功能。

解:图(a)逻辑函数Y的表达式图(b)逻辑函数Y的表达式可见,两电路具有“异或”的逻辑功能。

为提高报警信号的可靠性,在有关部位安置了3个同类型的危险报警器,只有当3个危险报警器中至少有两个指示危险时,才实现关机操作。

试画出具有该功能的逻辑电路。

解:在危急情况下,报警信号A 、B 、C 为高电平1,且当输出状态F 为高电平1时,设备应关机。

其真值表如下:由真值表可写出“与或”表达式:化简为: 逻辑图,如下图所示。

或者:用与非门 ==其逻辑电路略。

S10504N某设备有开关A 、B 、C ,要求:只有开关A 接通的条件下,开关B 才能接通;开关C 只有在开关B 接通的条件下才能接通。

违反这一规程,则发出报警信号。

设计一个由“与非门”组成的能实现这一功能的报警控制电路。

解:由题意可知,该报警电路的输入变量是三个开关A 、B 、C 的状态,设开关接通用1表示,开关断开用0表示;设该电路的输出报警信号为F ,F 为1表示报警,F 为0表示不报警。

可列出真值表:根据真值表做出卡诺图如下图(a )所示。

利用卡诺图对逻辑函数进行化简,得到最简逻辑表达式:根据逻辑表达式画出逻辑图,就得到题目所要求的控制电路如图(b )所示。

S10405G可否将“与非门”、“或非门”、“异或门”当做“反相器”使用如果可以,其输入端应如何处理并画出电路图。

解:如右图所示。

组合逻辑电路的设计步骤为:(1);(2);(3)简化和变换逻辑表达式,从而画出逻辑图。

解:⑴由电路的功能要求,列出真值表;(2)由真值表写出逻辑表达式;S11102B分析组合逻辑电路的步骤为:(1);(2);(3);(4)根据真值表和逻辑表达对逻辑电路进行分析,最后确定其功能。

解:由逻辑图写出个输出端逻辑表达式、化简和变换各逻辑表达式、列出真值表S11102I如图所示逻辑图,逻辑表达式= ;=。

解:;S11201I如图所示逻辑电路其逻辑表达式为( )。

A.B.C.D.解:DS11202B组合逻辑电路任何时刻的输出信号与该时刻的输入信号( ),与电路原来所处的状态( )。

A. 无关,无关B. 无关,有关C. 有关,无关D. 有关,有关解:CS11202I半加器的本位和输出端的逻辑关系是( )。

A. 与非B. 或非C. 与或非D. 异或解:D已知选出下列可以肯定使的情况是( )。

A. B.C. D.E.解:DS11203N图示为一简单的编码器,其中E、F、G是一般信号,A、B是输出量,为二进制代码变量。

今令AB= 10 ,则输入的信号为1的是( )。

A. EB. FC. G解:BS11301B编码器,译码器,数据选择器都属于组合逻辑电路。

( )解:√S11301N全加器的输出不仅取决于输入,同时还取决于相邻低位的进位,因此说全加器属于时序逻辑电路。

( )解:×S11302B用二进制代码表示某一信息称为编码。

反之把二进制代码所表示的信息翻译出来称为译码。

( )解:√S11302G在下列电路中,试问哪些电路能实现的逻辑关系解:A.√、B.×、C.×S11102G一个三变量排队电路,在同一时刻只有一个变量输出,若同时有两个或两个以上变量为1时,则按A、B、C的优先顺序通过,若F A=1表示A通过,F B、F C为1表示B、C通过,F A、F B、F C为0时表示其不通过,则表示变量A、B、C通过的表达式:F A=,F B = ,F C=。

解:A、、半加器逻辑符号如图所示,当A“0”,B“0”时,C和S分别为( )。

A.、B.、C.、解:CS11218B半加器的逻辑图如下,指出它的逻辑式为( )。

A. 、B. 、C. 、解:AS11219B全加器逻辑符号如图所示,当A i=“1”,B i=“1”,C i-1=“1”时,C i和S i分别为( )。

A. C i = 1 、S i = 0B. C i = 0 、S i = 1C. C i = 1 、S i = 1解:CS11207B全加器逻辑符号如图所示,当A i=“1”,B i=“1”,C i-1=“0”时,C i和S i分别为( )。

A. C i = 0、0B. 1、1C. 1、0解:CS11206B半加器逻辑符号如图所示,当A“1”,B“1”时,C和S分别为( )。

A. C = 0、S = 0B. C = 0、S = 1C. C = 1、S = 0解:CS11403B设计一个半加器电路(要求:列出真值表,写出逻辑式,画出逻辑电路)。

解:由半加器概念即只考虑两个一位二进制数A和B相加,不考虑低位来的进位数称半加:列出半加器真值表(a),其中,S为本位和数,C为向高位送出进位数由真值表可直接得出逻辑式:、由逻辑式可画出逻辑电路(b)。

图示逻辑电路的逻辑式为( )。

A.B.C.解:CS11213I逻辑电路如图所示,其逻辑功能相当于一个( )。

A. “与”非门B. “异或”门C. “与或非”门解:CS11404I写出图中所示电路的最简“与或”表达式。

解:F ==S11501B写出如图所示电路的逻辑表达式,并将其化简再用最简单的组合电路实现之。

解:最简电路如下图所示。

组合逻辑电路设计:某产品有A、B、C、D四项质量指标,A为主要指标。

检验合格品时,每件产品如果有包含主要指标A 在内的三项或三项以上质量指标合格则为正品,否则即为次品。

试设计一个全部用“与非门”组成的结构最简的正品检验机。

解:(1)对于A、B、C、D中任何指标,合格时用1表示,不合格时用0表示,检验结果正品用1表示,次品用0表示,列真值表如(a)。

(2)化简作卡诺图(b),得表达式:(3)逻辑电路如图(c)。

S11502G用“与非门”设计一组合逻辑电路,输入为四位二进制数,当数时,输出,其余情况。

解:S11405I有一个能将两个一位二进制数A、B进行比较的数字比较器,其逻辑状态列于下表中。

试写出各输出,,逻辑图如右图所示。

分析如图所示的逻辑电路,做出真值表,说明其逻辑功能。

解:该电路为“判奇电路”——输入为奇数个“1”,输出为“1”。

(真值表如下所示)S11503I试设计一个三变量的“判奇电路”。

解:真值表如下所示:S11503I如果对键盘上108个符号进行二进制编码,则至少要()位二进制数码。

(a) 5 (b) 6 (c) 71、用逻辑代数的基本公式和常用公式化简下列逻辑函数:解:2、证明下列异或运算公式。

解:3、用卡诺图化简下列函数。

解:分别将题中给定的逻辑函数卡诺图画出如图所示,并化简写出最简与或表达式。

4、编码器的逻辑功能是( )。

(a) 把某种二进制代码转换成某种输出状态(b) 将某种状态转换成相应的二进制代码(c) 把二进制数转换成十进制数5、译 码 器 的 逻 辑 功 能 是 ( )。

(a) 把 某 种 二 进 制 代 码 转 换 成 某 种 输 出 状 态(b) 把 某 种 状 态 转 换 成 相 应 的二 进 制 代 码(c) 把 十 进 制 数 转 换 成 二进 制 数十二、[共8分]两个输入端的与门、 或门和与非门的输入波形如图所示, 试画出其输出信号的波形。