门电路74182

华中科技大学 组成原理实验报告 运算器组成实验

课程实验报告课程名称:计算机组成原理专业班级:信息安全1003班学号:U**********名:***同组成员:张源信报告日期:2012年5月计算机科学与技术学院目录一、实验名称 (3)二、实验目的 (3)三、实验设备 (3)四、实验任务 (3)五、预备知识 (4)1、运算器的相关知识 (4)2、注意事项: (4)六、设计思路、电路实现与电路分析说明 (4)1、任务分析 (4)2、设计思路 (6)3、电路实现与详细分析说明 (7)七、实验结果的记录与分析 (9)八、实验中碰到的问题及解决办法 (10)九、收获与体会 (10)十、参考书目 (11)一、实验名称实验名称:运算器组成实验二、实验目的1、掌握带累加器的运算器实验2、掌握溢出检测的原理及实现方法3、理解有符号数和无符号数运算的区别4、理解基于补码的加\减运算实现原理5、熟悉运算器的数据传输通路6、利用74181和74182以及适当的门电路和多路选择器设计一个运算,要求支持有符号数和无符号数的运算支持补码加减法运算,支持有符号数溢出检测等功能三、实验设备JZYL—Ⅱ型计算机组成原理实验仪一台芯片:74LS181运算器芯片2片74LS373 8D锁存器3片四、实验任务自己设计一个电路和利用实验参考电路进行实验,实验要求先将多个运算数据事先存入存储器中,再由地址选中,选择不同的运算指令,进行运算,并将结果显示,还可以进行连续运算和移位,最后将最终结果写入到存储器中。

五、预备知识 1、运算器的相关知识运算器是对数据进行加工处理的部件,它具体实现数据的算术运算和逻辑运算,所以又称算术逻辑运算部件,简称ALU ,它是中央处理器的重要组成部分。

计算机中的运算器结构一般都包含如下几个部分:加法器、一组通用寄存器、输入数据选择电路和输出数据控制电路等。

74LS181能执行16种算术运算和16种逻辑运算,当工作方式控制端(M )为低电平时执行算术运算,当工作方式控制端(M )为高电平时执行逻辑运算,运算功能由功能选择端(S0-S3)决定。

数字电子技术概述—门电路

三、输入噪声容限

在 V 在 I偏 VI偏 V 离 IV H 离 和 IH V 和 IV L 的 IL 的 一 一 定 定 范 VO 范 基 VO 围 基 围 本 内 本 内 不 , 不 , 变 变 ; ; 在 在 输 输 出 出 变 变 化 , 化 , 允 允 允 允 许 许 许 许 范 输 范 输 围 入 围 称 入 内 称 的 内 为 的 为 变 输 变 输 化 入 化 入 范 噪 范

例题: 扇出系数计算举例

例2.4.1 查得基本的TTL与非门的参数如下: IOL=16mA, IIL=-1.0mA,IOH=0.4mA,IIH=0.04mA.试计算其带同类非 门时的扇出数。

解: (1)低电平输出时的扇出数

NOLIIO ILL11.06m mA A16

(2)高电平输出时的扇出数

NOHIIO IH H00.0 .4m 4 mA A 10

T2

T'2

R3

T4

0.9 v

D

T'1

B

0.2 V

T3

3.6V

A

图 2.4.22 TTL或非门的逻辑电路 B

≥1 Y A B

二、集电极开路门 (Open Collector Gate)

VCC(5 V)

R2 1.6k

R2 1.6k

R4 130

T4

Y1

A

T1

T2

vD3 OH

B

T5

R3 1k

1. 普通门电路输 出端不能并连。

R3 1k

VCC(5 V) R4 130

T4

D3

3.2V × T3

vI

输入全为高 电平 (3.6V) 输入有低电 平 (0.2V)

哈工大计算机考研真题2003-2008

哈尔滨工业大学2008年考研试题Ⅰ数据结构部分一填空题1.已知一个线性表有n个元素,其中每个元素的数据占8个字节,假设一个指针的大小为4个字节,如果采用有30个元素的数组存储,那么当数组中有效元素个数满足⑴条件时,数组的存储效率比不带头结点的单链表更高。

2. 给定14个字母,假设它们的权值都相等.采用huffman编码,则每个字母的平均代码长度是⑵。

3. 按C语言的运算符优先级,中缀表达式“A&&B||!(E>F)”的等价后缀形式为⑶。

4. 设按顺时针方向移动的循环队列Q[N]的头尾指针分别为F、R,头指针F总是指在队列中的第一个元素的前一位置,尾指针R在最后一个元素的位置,则队列中的元素个数为⑷。

5. 从空二叉树开始,严格按照BST(二又查找树)的插入算法,逐个插入关键字{18,73,10,5,68,99,27,41,32,25)构造出一颗BST ,对该BST按照先根遍历得到的序列为⑸。

6. 将两个长度为m的有序序列归并为一个有序序列,最少需要做⑹次关键字比较,最多需要做⑺次关键字比较。

7. 散列查找中,⑻现象称为冲突,⑼现象称为聚集。

8. 设可用的内存单元可处理4个记录,采用4 路归并的选择树法生成由小到大的初始归并段,对有12个记录在案的文件,产生的第一个初的归并段长度为⑽个。

9. 在两种求图的最小生成树的算法中,⑾算法适合于边稀疏的图的最小生成树。

10. 已知一个序列为{21,39,35,12,17,43},则利用堆排序方法建立的初始堆为:⑿。

二、判断(每题1分.共9分)1. 倒排文件只能按关键字的顺序存储。

(①)2. 堆的存储表示可能是链接式的,也可以是顺序的。

(②)3. 在AOE网中,任何一个关键活动的延迟,都会使整个工程延迟。

(③)4. 有环路的有向图不能进行拓扑排序。

(④)5. 对无向图进行一次深度优先搜索可以访问到图中的所有顶点。

(⑤)6. 大根堆的最大元素应该在堆顶,即根结点。

门电路PPT

3.2.2 二极管与门

其输入输出及真值表如表 3.2.1和3.2.2所示

其输出Y和输入A、B是与的关系,

即

Y AB

表3.2.1

表3.2.2

A BY

A BY

0V 0V 0.7V 规定3V以上为“1” 0 0 0

0V 3V 0.7V

或门

与门

即Y=A+B,对偶式为YD=

与非门

或非门

AB。正负逻辑的使用依个人 的习惯,但同一系统中采用

或非门

与非门

一种逻辑关系,本书采用

异或门

同或门

正逻辑

同或门

异或门

3.1 概述

3. 高低电平的实现

在数字电路中,输入输出

都是二值逻辑,其高低电平用

“0”和“1”表示。其高低电平

的获得是通过开关电路来实现,

兼容型( FET +BJT )

数字集成电路的基本逻辑单元是集成逻辑门,因 此本章先介绍CMOS和TTL数字集成逻辑门的结构、 工作原理

3.2 半导体二极管门电路

3.2.1半导体二极管的开关特性 1. 稳态开关特性 将图3.1.2中的开关用二极管代替,则可得到图 3.2.1所示的半导体二极管开关电路

符号如图3.3.1所示

D

D

BG

G

S

S

(a)标准符号

(b)简化符号

图3.3.1 增强型NMOS管的符号

3.3.1 MOS管的开关特性 NMOS共源极接法电路如图3.3.2(a)所示,输出特性 如(b)所示

图3.3.2 NMOS管共源极接法电路及其输出特性

3.3.1 MOS管(绝缘栅)的开关特性

74ls08实验原理知识描述

74ls08实验原理知识描述74LS08是一种四路与门芯片,它由四个与门组成。

在数字电路中,与门是最基本的逻辑门之一,它的输出信号只有在所有输入信号都为高电平时才为高电平,否则为低电平。

74LS08的实验原理是通过实验验证其与门的工作原理。

我们需要准备实验所需的器材和元件,包括74LS08芯片、电源、电路连接线、开关和LED等。

接下来,我们将根据74LS08的引脚图将芯片正确连接到电路中。

一般来说,74LS08的引脚分为四个与门输入引脚(1A、1B、2A、2B、3A、3B、4A、4B)、四个与门输出引脚(1Y、2Y、3Y、4Y)以及两个电源引脚(Vcc和GND)。

接下来,我们可以开始进行实验了。

首先,将电源连接到芯片的Vcc和GND引脚上,以提供工作电压。

然后,通过开关设置不同的输入信号组合,观察LED灯的亮灭情况。

根据与门的工作原理,只有当所有输入信号都为高电平时,与门的输出才为高电平,此时LED灯将亮起;否则,与门的输出为低电平,LED灯将熄灭。

通过实验,我们可以验证74LS08的工作原理。

当我们设置输入信号为高电平时,与门的输出为高电平,LED灯亮起;当我们设置输入信号为低电平时,与门的输出为低电平,LED灯熄灭。

通过对多个与门的连接和组合,我们可以构建更复杂的数字逻辑电路,实现各种功能。

总结一下,74LS08是一种四路与门芯片,通过实验可以验证它的与门工作原理。

通过观察输入和输出信号的变化,我们可以了解与门在数字电路中的作用和应用。

在实际的电子设计和开发中,我们可以使用74LS08芯片来构建各种数字逻辑电路,实现不同的功能和任务。

同时,我们还可以结合其他类型的逻辑门芯片,如或门、非门和异或门等,来构建更加复杂和多样化的数字电路。

通过深入理解和掌握74LS08的实验原理,我们可以更好地应用和设计数字电路,提高电子系统的性能和可靠性。

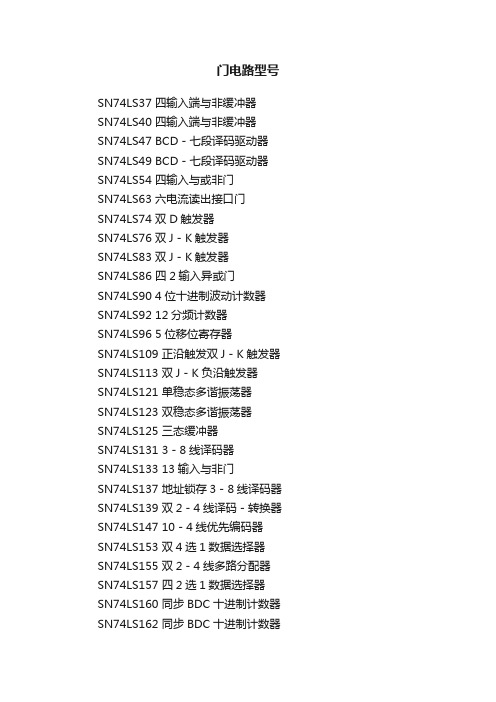

门电路型号

门电路型号SN74LS37 四输入端与非缓冲器SN74LS40 四输入端与非缓冲器SN74LS47 BCD-七段译码驱动器SN74LS49 BCD-七段译码驱动器SN74LS54 四输入与或非门SN74LS63 六电流读出接口门SN74LS74 双D触发器SN74LS76 双J-K触发器SN74LS83 双J-K触发器SN74LS86 四2输入异或门SN74LS90 4位十进制波动计数器SN74LS92 12分频计数器SN74LS96 5位移位寄存器SN74LS109 正沿触发双J-K触发器SN74LS113 双J-K负沿触发器SN74LS121 单稳态多谐振荡器SN74LS123 双稳态多谐振荡器SN74LS125 三态缓冲器SN74LS131 3-8线译码器SN74LS133 13输入与非门SN74LS137 地址锁存3-8线译码器SN74LS139 双2-4线译码-转换器SN74LS147 10-4线优先编码器SN74LS153 双4选1数据选择器SN74LS155 双2-4线多路分配器SN74LS157 四2选1数据选择器SN74LS160 同步BDC十进制计数器SN74LS162 同步BDC十进制计数器SN74LS164 8位串入并出移位寄存SN74LS166 8位移位寄存器SN74LS169 4位可逆同步计数器SN74LS172 16位多通道寄存器堆SN74LS174 6D型触发器SN74LS176 可预置十进制计数器SN74LS182 超前进位发生器SN74LS189 64位随机存储器SN74LS191 二进制同步可逆计数器SN74LS193 二进制可逆计数器SN74LS195 并行存取移位寄存器SN74LS197 可预置二进制计数器SN74LS238 3-8线译码/多路转换器SN74LS241 八缓冲/驱动/接收器SN74LS243 四总线收发器SN74LS245 八总线收发器SN74LS248 BCD-七段译码驱动器SN74LS251 三态8-1数据选择器SN74LS256 双四位选址锁存器SN74LS258 四2选1数据选择器SN74LS260 双5输入或非门SN74LS266 四2输入异或非门SN74LS275 七位树型乘法器SN74LS279 四R-S触发器SN74LS283 4位二进制全加器SN74LS293 4位二进制计数器SN74LS365 六缓冲器带公用启动器SN74LS367 六总线三态输出缓冲器SN74LS373 8D锁存器SN74LS375 4位双稳锁存器SN74LS386 四2输入异或门SN74LS393 双4位二进制计数器SN74LS574 8位D型触发器SN74LS684 8位数字比较器SN74LSO1 四2输入与非门SN74LS03 四2输入与非门SN74LS05 六反相器SN74LS07 六缓冲器/驱动器SN74LS09 四2输入与非门SN74LS11 三3输入与非门SN74LS13 三3输入与非门SN74LS15 三3输入与非门SN74LS17 六反相缓冲器/驱动器SN74LS21 双4输入与门SN74LS25 双4输入与门SN74LS27 三3输入与非门SN74LS30 八输入端与非门SN74LS33 四2输入或门SN74LS38 双2输入与非缓冲器SN74LS42 BCD-十进制译码器SN74LS48 BCD-七段译码驱动器SN74LS51三3输入双与或非门SN74LS55 四4输入与或非门SN74LS73 双J-K触发器SN74LS75 4位双稳锁存器SN74LS78 双J-K触发器SN74LS85 4位幅度比较器SN74LS88 4位全加器SN74LS91 8位移位寄存器SN74LS93 二进制计数器SN74LS95 4位并入并出寄存器SN74LS107 双J-K触发器SN74LS112 双J-K负沿触发器SN74LS114 双J-K负沿触发器SN74LS122 单稳态多谐振荡器SN74LS124 双压控振荡器SN74LS126 四3态总线缓冲器SN74LS132 二输入与非触发器SN74LS136 四异或门SN74LS138 3-8线译码/转换器SN74LS145 BCD十进制译码/驱动器SN74LS148 8-3线优先编码器SN74LS151 8选1数据选择器SN74LS154 4-16线多路分配器SN74LS156 双2-4线多路分配器SN74LS158 四2选1数据选择器SN74LS161 4位二进制计数器SN74LS163 4位二进制计数器SN74LS165 8位移位寄存器SN74LS168 4位可逆同步计数器SN74LS170 4x4位寄存器堆SN74LS173 4D型寄存器SN74LS175 4D烯触发器SN74LS181 运算器/函数发生器SN74LS183 双进位保存全价器SN74LS190 同步BCD十进制计数器SN74LS192 BCD-同步可逆计数器SN74LS194 双向通用移位寄存器SN74LS196 可预置十进制计数器SN74LS221 双单稳态多谐振荡器SN74LS240 八缓冲/驱动/接收器SN74LS242 四总线收发器SN74LS244 八缓冲/驱动/接收器SN74LS247 BCD-七段译码驱动器SN74LS249 BCD-七段译码驱动器SN74LS253 双三态4-1数据选择器SN74LS257 四3态2-1数据选择器SN74LS259 8位可寻址锁存器SN74LS261 2x4位二进制乘发器SN74LS273 八进制D型触发器SN74LS276 四J-K触发器SN74LS280 9位奇偶数发生校检器SN74LS290 十进制计数器SN74LS295 4位双向通用移位寄存器SN74LS366 六缓冲器带公用启动器SN74LS368 六总线三态输出反相器SN74LS374 8D触发器SN74LS377 8位单输出D型触发器SN74LS390 双十进制计数器SN74LS573 8位三态输出D型锁存器SN74LS670 8位数字比较器SN74HC00 四2输入与非门SN74HC02 四2输入或非门SN74HC03 四2输入或非门SN74HC04 六反相器SN74HC05 六反相器SN74HC08 四2输入与门SN74HC10 三3输入与非门SN74HC11 三3输入与门SN74HC14 六反相器/斯密特触发器SN74HC20 双四输入与门SN74HC21 双四输入与非门SN74HC27 三3输入与非门SN74HC30 八输入端与非门SN74HC32 四2输入或门SN74HC42 BCD十进制译码器SN74HC73 双J-K触发器SN74HC74 双D型触发器SN74HC76 双J-K触发器SN74HC86 四2输入异或门SN74HC107 双J-K触发器SN74HC113 双J-K负沿触发器SN74HC123 双稳态多谐振荡器SN74HC125 三态缓冲器SN74HC126 四三态总线缓冲器SN74HC132 二输入与非缓冲器SN74HC137 二输入与非缓冲器SN74HC138 3-8线译码/解调器SN74HC139 双2-4线译码/解调器SN74HC148 8选1数据选择器SN74HC151 双4选1数据选择器SN74HC154 4-16线多路分配器SN74HC157 四2选1数据选择器SN74HC161 4位二进制计数器SN74HC163 4位二进制计数器SN74HC164 8位串入并出移位寄存器SN74HC165 8位移位寄存器SN74HC173 4D型触发器SN74HC174 6D触发器SN74HC175 4D型触发器SN74HC191 二进制同步可逆计数器SN74HC221 双单稳态多谐振荡器SN74HC238 3-8线译码器SN74HC240 八缓冲器SN74HC244 八总线3态输出缓冲器SN74HC245 八总线收发器SN74HC251 三态8-1数据选择器SN74HC259 8位可寻址锁存器SN74HC266 四2输入异或非门SN74HC273 8D型触发器SN74HC367 六缓冲器/总线驱动器SN74HC368 六缓冲器/总线驱动器SN74HC373 8D锁存器SN74HC374 8D触发器SN74HC393 双4位二进制计数器SN74HC541 8位三态输出缓冲器SN74HC573 8位三态输出D型锁存器SN74HC574 8D型触发器SN74HC595 8位移位寄存器/锁存器SN74HC4028 7级二进制串行加数器SN74HC4046 锁相环SN74HC4050 六同相缓冲器SN74HC4051 8选1模拟开关SN74HC4053 三2选1模拟开关SN74HC4060 14位计数/分频/振荡器SN74HC4066 四双相模拟开关SN74HC4078 3输入端三或门SN74HC4511 7段锁存/译码驱动器SN74HC4520 双二进制加法计数器74F00 高速四2输入与非门74F02 高速四2输入或非门74F04 高速六反相器74F08 高速四2输入与门74F10 高速三3输入与门74F14 高速六反相斯密特触发74F32 高速四2输入或门74F38 高速四2输入或门74F74 高速双D型触发器74F86 高速四2输入异或门74F139 高速双2-4线译码/驱动器74F151 高速双2-4线译码/驱动器74F153 高速双4选1数据选择器74F157 高速双4选1数据选择器74F161 高速6D型触发器74F174 高速6D型触发器74F175 高速4D型触发器74F244 高速八总线3态缓冲器74F245 高速八总线收发器74F373 高速8D锁存器SN74HCT04 六反相器。

门电路知识介绍

通过输入信号vi,控 制二极管或三极管工 作在截止和导通两个 状态,就可以达到开 关S的作用。

正逻辑和负逻辑

正逻辑: 高电平—1;低电平—0 负逻辑: 高电平—0;低电平—1

高低电平都有一个允许 的范围

2.2 半导体二极管和三极管的开关特性

二极管:具有单向导电 性。相当于一个受外 加电压极性控制的开 关。 假定:VIH=VCC,VIL=0 D为理想二极管(正 向导通,电阻为0; 反向电阻为无穷大)

二极管正向压降0.7V。

3. 真值表(状态表) A 0 0 1 1 B O 1 0 1 Y 0 0 0 1

Da 导通 导通 截止 导通

Db 导通 截止 导通 导通

UY 0.7V 0.7V 0.7V 3.7v

4. 输出函数式 5. 逻辑符号

Y=A•B A B & Y

二极管与门的特点

缺点: ①输出的高低电平数值与输入的高 低电平数值不相等,相差VDF。多极时, 发生高低电平的偏移。 ②当输出端对地接上负载电阻时, 负载电阻的改变有时会影响输出的高电 平。 仅用作集成电路内部的逻辑单元。

t

uO

夹断区: UGS< Uth, ID=0

——D、S间相当于开关断开。

t

0V

+VDD

§2—3 最简单的与、或、非门电路

2-3-1 二极管与门

A B Ua Ub 0 0 0 3v 3v 0 3v 3v Da

+VCC

1. 电路组成(以二输入为例)

2. 工作原理 设:VCC=5V,

R

Y

Db

UIH=3v,UIL=0v

MOS管开关特性

MetalOxidesemiconductorfield-Effect-Transistor N沟道,P沟道 增强型,耗尽型 是电压控制型器件

门电路工作原理

门电路工作原理

门电路是一种基础的电子电路,它能够实现逻辑运算。

门电路的工作原理是基于数字逻辑运算的原理。

其中包括与门、或门、非门和异或门等不同类型的门电路。

首先,让我们来讨论与门的工作原理。

与门有两个输入端和一个输出端,只有当两个输入信号同时为高电平时,输出信号才为高电平;否则,输出信号为低电平。

这个原理可以用以下的真值表表示:

输入A 输入B 输出

0 0 0

0 1 0

1 0 0

1 1 1

下面是与门的电路图示意图:

┌───┐

│ │

A B

│ │

└───┘

│

▼

┌───┐

│ │

输出

│ │

└───┘

与门的工作原理是通过两个输入信号经过逻辑运算,通过晶体管或其他逻辑门元件的控制,实现输出信号的电平变化。

只有当两个输入信号同时为高电平时,门电路才会产生高电平输出,否则输出为低电平。

其他类型的门电路工作原理与与门类似,只是其逻辑运算规则有所不同。

例如,或门只有当两个输入信号中至少一个为高电平时,输出信号才为高电平。

非门则将输入信号的电平反转,当输入信号为高电平时,输出信号为低电平,反之亦然。

通过组合不同类型的门电路,我们可以实现更复杂的逻辑运算,从而搭建起计算机的基础。

门电路的工作原理是通过逻辑运算实现对输入信号的处理和转换,最终得到期望的输出信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

© 2000 Fairchild Semiconductor Corporation DS009492April 1988Revised September 200074F182 Carry Lookahead Generator74F182Carry Lookahead GeneratorGeneral DescriptionThe 74F182 is a high-speed carry lookahead generator. It is generally used with the 74F181 or 74F381 4-bit arith-metic logic units to provide high-speed lookahead over word lengths of more than four bits.Featuress Provides lookahead carries across a group of four ALUs s Multi-level lookahead high-speed arithmetic operation over long word lengthsOrdering Code:Devices also available in T ape and Reel. Specify by appending the suffix letter “X” to the ordering code.Logic Symbols Connection DiagramOrder Number Package NumberPackage Description74F182SJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide 74F182PCN16E16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide 274F 182Unit Loading/Fan OutFunctional DescriptionThe 74F182 carry lookahead generator accepts up to four pairs of Active LOW Carry Propagate (P 0–P 3) and Carry Generate (G 0–G 3) signals and an Active HIGH Carry input (C n ) and provides anticipated Active HIGH carries (C n +x ,C n +y , C n +z ) across four groups of binary adders. The 74F182 also has Active LOW Carry Propagate (P) and Carry Generate (G) outputs which may be used for further levels of lookahead. The logic equations provided at the outputs are:C n +x = G 0 + P 0 C nC n +y = G 1 + P 1 G 0 + P 1 P 0 C nC n +z = G 2 + P 2 G 1 + P 2 P 1 G 0 + P 2 P 1 P 0 C n G = G 3 + P 3 G 2 + P 3 P 2 G 1 + P 3 P 2 P 1 G 0P = P 2 P 2 P 1 P 0Also, the 74F182 can be used with binary ALUs in an active LOW or active HIGH input operand mode. The con-nections (Figure 1) to and from the ALU to the carry looka-head generator are identical in both cases. Carries are rippled between lookahead blocks. The critical speed path follows the circled numbers. There are several possible arrangements for the carry interconnects, but all achieve about the same speed. A 28-bit ALU is formed by dropping the last 74F181 or 74F381.*ALUs may be either 74F181 or 74F381FIGURE 1. 32-Bit ALU with Rippled Carry between 16-Bit Lookahead ALUsPin Names DescriptionU.L.Input I IH /I IL HIGH/LOW Output I OH /I OL C n Carry Input1.0/2.020 µA/−1.2 mA G 0, G 2Carry Generate Inputs (Active LOW) 1.0/14.020 µA/−8.4 mA G 1Carry Generate Input (Active LOW) 1.0/16.020 µA/−9.6 mA G 3Carry Generate Input (Active LOW) 1.0/8.020 µA/−4.8 mA P 0, P 1Carry Propagate Inputs (Active LOW) 1.0/8.020 µA/−4.8 mA P 2Carry Propagate Input (Active LOW) 1.0/6.020 µA/−3.6 mA P 3Carry Propagate Input (Active LOW) 1.0/4.020 µA/−2.4 mAC n +x − C n +z Carry Outputs50/33.3−1 mA/20 mA G Carry Generate Output (Active LOW)50/33.3−1 mA/20 mA PCarry Propagate Output (Active LOW)50/33.3−1 mA/20 mA74F182 Truth TableH = HIGH Voltage Level L = LOW Voltage Level X = Immaterial Inputs OutputsC n G0P0G1P1G2P2G3P3C n+x C n+y C n+z G PX H H LL H X LX L X HH X L HX X X H H LX H H H X LL H X H X LX X X L X HX L X X L HH X L X L HX X X X X H H LX X X H H H X LX H H H X H X LL H X H X H X LX X X X X L X HX X X L X X L HX L X X L X L HH X L X L X L HX X X X X H H HX X X H H H X HX H H H X H X HH H X H X H X HX X X X X L X LX X X L X X L LX L X X L X L LL X L X L X L LH X X X HX H X X HX X H X HX X X H HL L L L L 474F 182Logic DiagramPlease note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.74F182Absolute Maximum Ratings (Note 1)Recommended Operating ConditionsNote 1: Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.Note 2: Either voltage limit or current limit is sufficient to protect inputs.DC Electrical CharacteristicsStorage Temperature−65°C to +150°C Ambient Temperature under Bias −55°C to +125°C Junction Temperature under Bias −55°C to +150°C V CC Pin Potential to Ground Pin −0.5V to +7.0V Input Voltage (Note 2)−0.5V to +7.0V Input Current (Note 2)−30 mA to +5.0 mAVoltage Applied to Output in HIGH State (with V CC = 0V)Standard Output −0.5V to V CC 3-STATE Output −0.5V to +5.5VCurrent Applied to Output in LOW State (Max)twice the rated I OL (mA)ESD Last Passing Voltage (Min)4000VFree Air Ambient Temperature 0°C to +70°CSupply Voltage+4.5V to +5.5VSymbol ParameterMin TypMaxUnits V CCConditionsV IH Input HIGH Voltage 2.0V Recognized as a HIGH Signal V IL Input LOW Voltage 0.8V Recognized as a LOW Signal V CD Input Clamp Diode Voltage −1.2V Min I IN = −18 mA V OH Output HIGH 10% V CC 2.5V Min I OH = −1 mA Voltage 5% V CC 2.7I OH = −1 mA V OL Output LOW 10% V CC0.5V Min I OL = 20 mA Voltage I IH Input HIGH 5.0µA Max V IN = 2.7V CurrentI BVI Input HIGH Current 7.0µA Max V IN = 7.0V Breakdown Test I CEX Output HIGH 50µA Max V OUT = V CC Leakage Current V ID Input Leakage 4.75V 0.0I ID = 1.9 µATestAll Other Pins Grounded I OD Output Leakage 3.75µA 0.0V IOD = 150 mVCircuit Current All Other Pins Grounded I ILInput LOW −1.2mAMax V IN = 0.5V (C n )Current−2.4V IN = 0.5V (P 3)−3.6V IN = 0.5V (P 2)−4.8V IN = 0.5V (G 3, P 0, P 1)−8.4V IN = 0.5V (G 0, G 2)−9.6V IN = 0.5V (G 1)I OS Output Short-Circuit Current −60−150mA Max V OUT = 0V I CCH Power Supply Current 18.428.0mA Max V O = HIGH I CCLPower Supply Current23.536.0mAMaxV O = LOW 674F 182AC Electrical CharacteristicsSymbolParameterT A = +25°CT A = −55°C to +125°CT A = 0°C to +70°C UnitsV CC = +5.0V V CC = +5.0V V CC = +5.0V C L = 50 pFC L = 50 pF C L = 50 pF MinTyp Max Min Max Min Max t PLH Propagation Delay 3.0 6.68.5 3.012.0 3.09.5ns t PHL C n to C n +x , C n +y , C n +z 3.0 6.89.0 3.011.0 3.010.0t PLH Propagation Delay 2.5 6.28.0 2.511.0 2.59.0ns t PHL P 0, P 1, or P 2 to 1.53.75.01.07.01.56.0C n +x , C n +y , or C n +z t PLH Propagation Delay 2.5 6.58.5 2.511.0 2.59.5nst PHL G 0, G 1, or G 2 to 1.53.95.21.07.01.56.0C n +x , C n +y , or C n +z t PLH Propagation Delay 3.07.910.0 3.012.0 3.011.0ns t PHL P 1, P 2, or P 3 to G 3.0 6.08.0 2.510.0 3.09.0t PLH Propagation Delay 3.08.310.5 3.012.0 3.011.5ns t PHL G n to G3.0 5.77.5 2.510.0 3.08.5t PLH Propagation Delay 3.0 5.77.5 2.510.0 3.08.5nst PHLP n to P2.54.15.52.58.02.56.5 74F182Physical Dimensions inches (millimeters) unless otherwise noted16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm WidePackage Number M16D874F 182 C a r r y L o o k a h e a d G e n e r a t o rPhysical Dimensions inches (millimeters) unless otherwise noted (Continued)16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 WidePackage Number N16EFairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICYFAIRCHILD ’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user. 2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.。