Allegro16.6 中Constraint Area 设置

ALLEGRO中区域约束规范

ALLEGRO中区域约束规范

首先打开再进入physical这一项设置区域的线宽等,具体步骤选中Physical Constraint Set,,点中ALL Layers再建个区域(如BGA),设置线宽等,如图

1.1

再选中Region,在右下图中创建一个规划的区域如(BGA_BGA),在Referenced Physical C Set 项选择BGA ,进行线宽等设置。

见图1.2

接着进入Spacing这一相进行间距等设置,选中Spacing Constraint Set 建立一个规范区域(如BGA)进行间距设置,如图1.3

接着选中Region,,在Objects一项建立规划区域(如BGA_BGA), 在Referenced Physical C Set 项选择BGA进行间距设置,如图1.4

以上内容便可完成ALLEGRO中区域约束规范。

怎么画ALLEGRO中区域来约束规范:

1、首先选中,再选择option,见下图

2、

再确实即可。

Allegro16.6约束管理器及使用示例

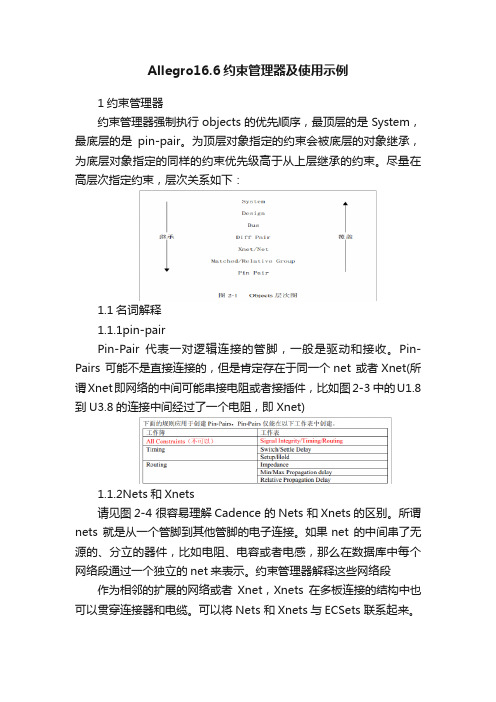

Allegro16.6约束管理器及使用示例1约束管理器约束管理器强制执行objects的优先顺序,最顶层的是System,最底层的是pin-pair。

为顶层对象指定的约束会被底层的对象继承,为底层对象指定的同样的约束优先级高于从上层继承的约束。

尽量在高层次指定约束,层次关系如下:1.1名词解释1.1.1pin-pairPin-Pair代表一对逻辑连接的管脚,一般是驱动和接收。

Pin-Pairs 可能不是直接连接的,但是肯定存在于同一个net 或者Xnet(所谓Xnet即网络的中间可能串接电阻或者接插件,比如图2-3 中的U1.8到U3.8的连接中间经过了一个电阻,即Xnet)1.1.2Nets和Xnets请见图2-4 很容易理解Cadence 的Nets 和Xnets的区别。

所谓nets 就是从一个管脚到其他管脚的电子连接。

如果net 的中间串了无源的、分立的器件,比如电阻、电容或者电感,那么在数据库中每个网络段通过一个独立的net来表示。

约束管理器解释这些网络段作为相邻的扩展的网络或者Xnet,Xnets在多板连接的结构中也可以贯穿连接器和电缆。

可以将Nets 和Xnets与ECSets 联系起来。

1.1.3Match GroupsMatch Group 是nets,Xnets或者pin-pairs 的集合,此集合一定要都匹配(delay 或者length)或者相对于组内的一个明确的目标。

如果delta 值没有定义,组内的所有成员都将是绝对匹配的,并允许有一定的偏差。

如果定义了delta 值,那么组内所有成员将相对匹配于明确的目标网络。

1.2在线检查设置首先在约束管理器中需要进行以下设置Analyze -> Analysis Modes这样在布线后,在相应的地方都会显示线长或约束相差值;如下图1.3示例通过一个实例来理解约束管理器U1看作是MCU,U2为DDR,ADDR0-3为地址线,需要作等长处理;CLK为时钟线,差分处理;U3,U4为连接同一个MCU的DDR;地址线是复用的,设置通过T型网络连接;需要作等长处理U5为DDR,DDR_DQ0-3为数据线,需要作等长处理1.3.1差分对约束即上图中的DDR_CLKP,DDR_CLKN设置Electrical ->Electrical Constraint Set -> Differential Pair 在Object的Name下方Project右键Create -> Electrical CSet;并输入参数差分对约束参数主要有以下几个:Min line spacing:内间距最小线距,若实际走线内间距小于这个值,DRC就会出错。

Allegro 16.6功能操作

Allegro 16.6 功能操作在Allegro中增加零件及修改连线关系1. Setup - User Preferences Editor – Logic –logic _edit_enabled的Value勾选2. 增加零件:Logic - Part Logic 在Part Modification Area 填入相关信息(也可以在Part Selection Area中找到类似的元器件)单击Add再OK3. 修改连接关系:单击元器件焊盘,在右边的Options中选择网络。

或者增加新的网络(Create)编辑网络名(Rename)删除网络名(Remove)如何在Allegro中即时显示dynamic length(动态走线长度)对话框Setup - User Preferences Editor – Route – Connect – allegro_etch_length_on勾选。

在Allegro中如何将尖角走线改成圆弧走线1. 可以直接画圆弧:右边的Options选项中的Line lock选择Arc并勾选最下面的Replace etch(替换原有走线)2. 使用slide命令(移动走线):右边的Options选项中 Vertex Action中Move改成Arc Corner,去拉动走线在Allegro中如何把DRC标记显示为实心Setup - User Preferences Editor – Display – Visual – display_drcfill勾选在Allegro中怎么增加和删除泪滴(teardrop)1. 增加泪滴(teardrop):Route – Gloss – parameters... – Fillet and tapered trace勾选,注意勾选前在Fillet and tapered trace 点击跳出编辑框选择你所需要的对象2. Edit – Delete 右边的Options栏中选择Cline ,在Find栏中Find by name中选择Property ,点击More ,点选Fillet= ,/Apply/OK即可注意:无论加泪滴还是删掉泪滴,一定要先打开所有的走线层,否则,没打开的走线层就不会有执行如何在Allegro中设置自动存盘系统自动存盘需要用户自己设置,具体方法如下:Setup - User Preferences Editor – File_management – AutosaveAutosave_dbcheck:设置存盘时是否需要数据检查,如果此项设为存盘时需要数据检查则会使存盘时间加长 Autosace_time:自动存盘时间设置。

Allegro约束规则设置

约束规则的设置孙海峰在PCB设计中规则设置是必不可少的,它也可以被称为DRC检查规则,用来确定电路板的走线规则是否符合设计要求。

在Allegro PCB的电路板设计过程中,设计约束规则主要包括时序规则、走线规则、间距规则、信号完整性规则等以及物理规则等设置。

首先,需要认识一下,Allegro PCB的约束管理器:在PCB设计界面中,执行Setup/Constraints/Constraint Manager命令,弹出Allegro Constraint Manager对话框,如下图。

在约束管理器中,设计者可以对电路板的电气规则、物理规则、间距规则等设计规则进行设置定义。

约束规则可以按板层、网络或者区域进行设置。

约束管理器是Cadence系统提供的专用规则设置系统,主要有菜单栏、工具栏、工作表选择区、工作状态报告栏四部分,在工作表中选择一个对象,然后右击,在弹出的命令菜单中,可以进行任意操作。

工作表选择区内可以选择电气规则、物理规则、间距规则等规则设置。

在对应Net文件夹内,可以创建指定网络的对象分组,如:系统、设计、总线、差分对、扩展网络(XNet)、网络、相对或匹配群组,也可以创建基于相关属性的电气规则(ECSet)、物理规则(PCSet)、间距规则(SCSet)等。

约束管理器的约束对象分为引脚对、总线和匹配群组,她们相互之间存在优先级差异,即底层对象会集成顶层对象指定约束,为底层对象指定的约束优先高于上层继承的约束,对象层次的优先级为系统、设计、总线、差分对、扩展网络、相对或匹配群组、引脚对。

一、电气规则设置在约束管理器中,选择Electrical选项卡,其中可以为设计或网络来设置时序规则、信号完整性规则、布线的电气规则(延时、差分对)等,执行Objects/Create/Electrical CSet命令可新建电气规则。

1、选择信号完整性仿真规则Signal Integrity属性,其中包括电气属性、反射属性、单调失真属性、初始串扰、仿真串扰以及同步开关噪声这六个规则设置。

Allegro16.6约束规则设置详解_SCC

Allegro16.6约束规则设置详解前言:本文主要讲解Allegro16.6约束管理器的使用,从基本约束规则到高级约束规则的设置。

目录:一、基本约束规则设置1、线间距设置2、线宽设置3、设置过孔4、区域约束规则设置5、设置阻抗6、设置走线的长度范围7、设置等长7.1、不过电阻的NET等长7.2、过电阻的XNET等长7.3、T型等长8、设置通用属性9、差分规则设置9.1、创建差分对9.2、设置差分约束10、Pin Delay二、高级约束规则设置11、单个网络长度约束12、a+b类长度约束13、a+b-c类长度约束14、a+b-c在最大和最小传播延迟中的应用1、线间距设置(1)、设置默认间距规则点击CM图标,如下图所示,打开约束管理器。

单击Spacing,再点击All Layers,如下图所示。

右边有一个DEFAULT就是默认规则,我们可以修改其值。

按住Shift键,点击第一个和最后一个即可选中所示,然后输入一个值,这样就都修改了,如下图所示(2)、定义特殊的间距约束点选Default按鼠标右键,执行Create-Spacing CSet加入新规则。

取一个有意义点的名字,如下图所示,单击OK。

其值是从默认规则拷贝的,先修改其值。

按住Shift键选中所有,输入12,回车。

然后为所需要设置的网络分配规则单击左边的Net-All Layers,在右边工作簿中,为GND网络设置12MIL_SPACE规则,在Referenced Spacing CSet下选中12MIL_SPACE,如下图所示(3)、设置Class-Class规则若针对不同的信号群组有不同的间距规则,则需要设置Class-Class选到Net Class-Class后,在右边CLOCK(2)上右键选择Ctreat-Class-Class...,如下图所示选择2个不同的Net Classes,如下图所示,单击OK如下图所示。

在右边的Referenced Spacing CSet栏可以修改其值。

allegro设置区域规则

allegro设置区域规则以Allegro 设置区域规则为标题,本文将探讨Allegro 平台中设置区域规则的方法和重要性。

区域规则是Allegro 平台中的一项重要功能,它可以帮助卖家更好地管理和展示商品,提供更好的购物体验。

区域规则主要用于控制商品的展示范围和销售限制,使卖家能够根据不同地区的需求和法律法规进行灵活的调整。

设置区域规则可以帮助卖家更好地针对不同地区的需求进行定制化展示。

不同地区的消费者对商品的需求和偏好有所不同,通过设置区域规则,卖家可以根据地区特点进行展示策略的调整。

比如,某些地区对某种商品的需求量较大,卖家可以通过设置区域规则将该商品在该地区的展示位置提前,以便更好地满足消费者需求,提高销售量。

设置区域规则还可以帮助卖家合理控制商品的销售范围和限制。

有些商品可能受到地区法律法规的限制,或者卖家只希望在特定地区销售某些商品。

通过设置区域规则,卖家可以将商品的销售范围限制在特定地区,避免违反法律法规或者销售策略。

同时,卖家也可以根据销售情况进行调整,及时调整销售范围,以便更好地控制库存和销售效果。

设置区域规则还可以帮助卖家更好地管理价格和促销活动。

不同地区的消费能力和购买习惯不同,通过设置区域规则,卖家可以根据地区特点进行灵活的定价和促销策略。

比如,在某些地区消费者对价格敏感,卖家可以通过设置区域规则在该地区进行价格调整或者促销活动,以吸引更多消费者,提高销售额。

设置区域规则还可以帮助卖家更好地管理物流和售后服务。

不同地区的物流能力和售后服务水平有所差异,通过设置区域规则,卖家可以根据地区特点进行灵活的物流和售后服务策略。

比如,在物流能力较强的地区,卖家可以提供更快速的物流服务,提高消费者的满意度和购买意愿。

Allegro 平台中设置区域规则对卖家来说具有重要的意义。

通过合理设置区域规则,卖家可以更好地管理和展示商品,提高销售效果,满足消费者的需求,增强竞争力。

因此,卖家应该充分利用Allegro 平台提供的区域规则功能,根据地区特点进行灵活调整,以获得更大的商机和利润。

Allegro16.6设置等长规则

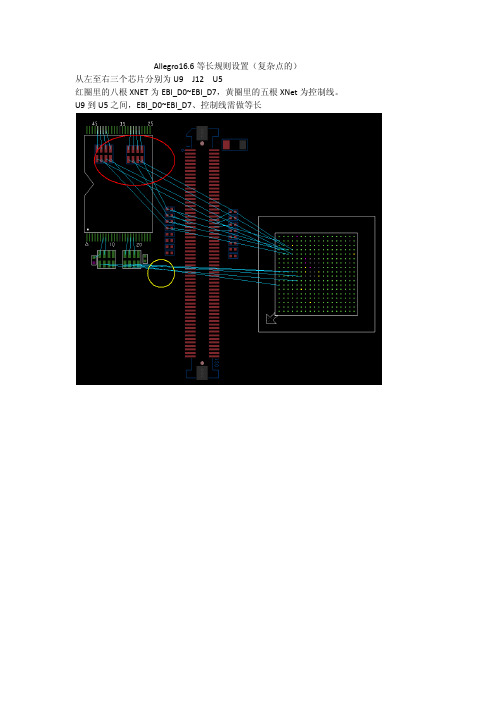

Allegro16.6等长规则设置(复杂点的)从左至右三个芯片分别为U9 J12 U5红圈里的八根XNET为EBI_D0~EBI_D7,黄圈里的五根XNet为控制线。

U9到U5之间,EBI_D0~EBI_D7、控制线需做等长多出来的八根XNET为EBI_D8~EBI_D15J12到U5之间EBI_D0‐ EBI_D15做等长接下来开始步骤:(设模型、X‐NET就不说啦,坛子里有很多说的挺清楚的)将EBI_D0~EBI_D15设为一个Class,EBI_D将EBI_D0~EBI_D15设PINPAIREBI_D0~EBI_D7设置两组PINPAIREBI_D8~EBI_D15设置一组PINPAIR设EBI_D0 拓扑Set‐Constraint红框中填好点ADD再新增另一个规则点ADD点OK后回到以下界面,FILE‐Update Constraint Manager点是出现两组MGrp,每组下面只出现一对,因为仅对EBI_D0设了规则。

EBI_D0和EBI_D1~D7的拓扑一样的,将刚才生成的ElecCset赋予它们赋予它们的同时,两组MGrp里的PPr也在增多但EBI_D8~D15的拓扑和它们不一样,所以得重新建拓扑设规则省略几步,和之前设的时候一样的点是,可以看到EBI_D8被赋予规则EBI_D8,EBI_D9~D15拓扑与EBI_D8一样的,所以把EBI_D8这一规则分别赋予它们。

目前为止,EBI_D0~D15从U5到J12就做了等长,走线时就有控制进度条显示但是从U5到U9这一段还有几根控制线未加进来找到这几根控制线,add to MatchGroupEBINAND这一MatchGroup里就有这些XNET了。

红色框中选择ALL DRIVERS..红色框中改为0mil:100milU9到U5之间,EBI_D0~EBI_D7、控制线就做好等长啦、这种设等长的方式思路挺清晰的,所以就推荐给大家,或者是给还不会设等长的一点参考。

allegro中的约束规则

allegro中的约束规则摘要:1.Allegro 中的约束规则概述2.约束规则的分类3.常见约束规则介绍4.约束规则的设置与应用5.约束规则对PCB 设计的影响正文:【1.Allegro 中的约束规则概述】Allegro 是一款专业的EDA 工具,广泛应用于PCB 设计领域。

在Allegro 中,约束规则是一种用于指导布局布线过程的重要工具,能够帮助设计者实现高效、精准的PCB 设计。

通过设置约束规则,设计者可以对元件、走线等进行精确控制,从而提高设计质量。

【2.约束规则的分类】在Allegro 中,约束规则主要分为以下几类:1.元件约束:对元件的位置、尺寸等进行限制。

2.走线约束:对走线的宽度、长度、角度等进行限制。

3.区域约束:对PCB 上的特定区域进行限制,如禁止布线区、固定区域等。

4.设计规则约束:对整个设计过程进行控制,如设置最小线宽、最小间距等。

【3.常见约束规则介绍】1.元件约束:元件约束是针对PCB 上的元件进行设置的。

常见的元件约束有:- 元件位置:设置元件在PCB 上的具体位置。

- 元件尺寸:限制元件的大小,以确保元件不会过大或过小。

- 元件与其他元件的距离:限制元件与其他元件之间的距离,以确保电气性能和可制造性。

2.走线约束:走线约束是针对PCB 上的走线进行设置的。

常见的走线约束有:- 走线宽度:设置走线的最小宽度,以确保走线的电气性能。

- 走线长度:限制走线的最大长度,以减少信号传输的延迟。

- 走线角度:限制走线的拐角角度,以减小信号反射。

3.区域约束:区域约束是针对PCB 上的特定区域进行设置的。

常见的区域约束有:- 禁止布线区:设置禁止布线的区域,以确保这些区域的功能不受影响。

- 固定区域:设置固定不变的区域,以确保这些区域的功能不受布线影响。

【4.约束规则的设置与应用】在Allegro 中,设计者可以通过以下步骤设置和应用约束规则:1.打开Allegro 软件,导入PCB 设计文件。