Allegro中的约束规则设置V1.2

ALLEGRO中区域约束规范

ALLEGRO中区域约束规范

首先打开再进入physical这一项设置区域的线宽等,具体步骤选中Physical Constraint Set,,点中ALL Layers再建个区域(如BGA),设置线宽等,如图

1.1

再选中Region,在右下图中创建一个规划的区域如(BGA_BGA),在Referenced Physical C Set 项选择BGA ,进行线宽等设置。

见图1.2

接着进入Spacing这一相进行间距等设置,选中Spacing Constraint Set 建立一个规范区域(如BGA)进行间距设置,如图1.3

接着选中Region,,在Objects一项建立规划区域(如BGA_BGA), 在Referenced Physical C Set 项选择BGA进行间距设置,如图1.4

以上内容便可完成ALLEGRO中区域约束规范。

怎么画ALLEGRO中区域来约束规范:

1、首先选中,再选择option,见下图

2、

再确实即可。

ALLEGRO约束设置

ALLEGRO约束规则设置介绍目录:第一部分:差分对的约束设置 (1)第二部分:非差分信号约束设置 (8)第三部分:区域约束设置 (11)第四部分:XNet等长设置 (12)本文所有操作与设置均在Allegro PCB editor 15.5环境中进行。

第一部分:差分对的约束设置下面我们将通过对LVDS差分对信号的约束设置分步骤的讲解各个设置过程,其约束条件如步骤1:全局约束设置。

在PCB editor界面下,点击“Setup→Constraints”或点击图标打开“Constraints Sys”窗口,将出现下图所示窗口。

点击“Set standard values”,弹出“Default values form”界面,在此可设置默认值,且窗口中所有设置值各自分属于spacing rule 和Physical rule 中名为“Default”的约束集。

此处我们取默认值。

图1下面步骤2-步骤4为Physical(Line/vias)rule物理特性(线宽和过孔)约束设置过程步骤2:线宽约束设置。

点击“Physical(Line/vias)rule set→set values”,在出现的窗口上方空白处填入新约束名称,如“LVDS_SIG”,然后点击“ADD”,新的约束就产生了。

如果需要设置这是某一层的约束,还要在“subclass”中选择相应的层面。

接下来就在相应栏填入需要的值。

如下图所示:图2如果还有其它信号的线宽要求,请重复上述步骤。

Min line width:最小线宽Max line width:最大线宽,填0=∞Min neck width:Neck 模式最小线宽Max neck length:Neck 模式最大走线长度DiffPair primary gap:首选差分间距(单端线可不填)DiffPair neck gap:Neck 模式差分间距(单端线可不填)过孔规格在“Via list property”中设定,一般设定在默认约束规则下。

allegro教程之基本规则设置布线规则设置线宽及线间距的设置

A l l e g r o教程之基本规则设置布线规则设置线宽及线间距的设置-CAL-FENGHAI.-(YICAI)-Company One1在PCB设计过程中,需要通过设置各种规则,以满足各种信号的阻抗。

比如,常用的高速差分线,我们常控的100欧姆,那么到底走多宽的线以及差分线之间的间距到底是多少,才能满足设计要求的100欧姆阻抗呢本文就对 Allegro 种的基本规则设置做一个详细的讲解。

注:本文是基于 Allegro 15 版本的。

对于16版本不适用。

首先需要打开规则管理器,可通过以下三种方式打开:一、点击工具栏上的图标。

二、点击菜单Setup->Constraints三、在命令栏内输入 "cns" 并回车打开的规则管理器如下:在最上面一栏有一个On-line DRC,这是对画板过程中不停检测是否违反规则,并可产生DRC。

一般我们都默认开启。

可以实时查看产生的 DRC 错误,并加以修正。

接下来的 Spacing rule set 是对走线的线间距设置。

比如对于时钟线、复位线、及高速查分线。

我们可以再这里面加一规则,使其离其它信号线尽可能的远。

Physical(lines/vias)rule set 是针对各种物理规则设置,比如线宽,不同信号线的过孔等。

例如我们可通过电源网络的设置,使其默认线宽比普通信号走线更粗,已满足走线的载流能力。

现针对一个时钟及电源,分别设置间距规则和物理规则。

首先筛选网络,对于需要设置线间距规则的网络赋上 Net_Spacing_Type 属性、而对于需要设置线宽规则的网络赋上 Net_Physical_type 。

而对于即要线间距和线宽规则约束的网络,可将Net_Spacing_Type 及Net_Physical_type 属性同时赋上。

本例针对的时钟网络,只需要对其赋上Net_Spacing_Type ,方法如下:点击菜单 Edit->Properties然后在右侧 Find 一栏中选择 Nets 。

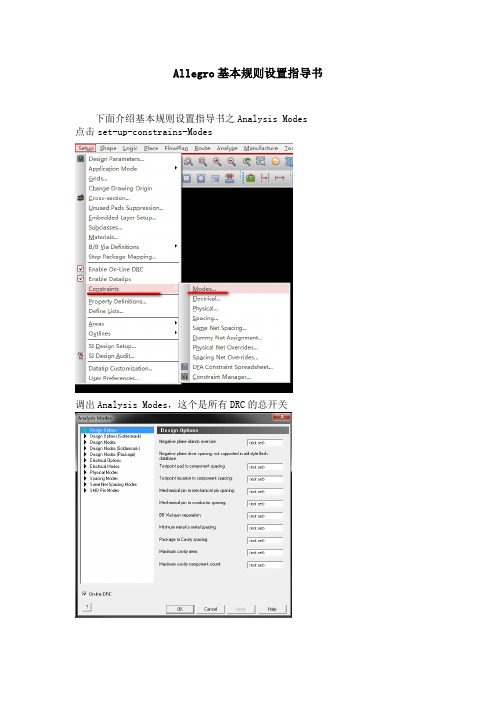

Allegro基本规则设置指导书

Allegro基本规则设置指导书下面介绍基本规则设置指导书之Analysis Modes 点击set-up-constrains-Modes调出Analysis Modes,这个是所有DRC的总开关下面介绍常用的一些开关设置1.Design Options (Soldermask)从上往下阻焊到阻焊的间距阻焊到pad和走线间距阻焊到shape1的间距钢网到钢网的间距2.Design Mode从上往下测试点Pad到器件DRC开关测试点到器件的DRC开关测试点在器件下方的DRC开关重孔开关3.Design Mode(soldermask)从上往下阻焊到阻焊的DRC开关阻焊到Pad和线的DRC开关阻焊到shape的DRC开关钢网到钢网的DRC开关4.Design Modes(Package)从上到下器件和器件的DRC开关器件超出package keepin的DRC开关器件在器件禁布的DRC开关5.Electric options从上往下开启最短长度延时开启相对长度延时开启pin delay开启Z轴延时6.Electric Modes从上往下绝对长度延时开关相对长度延时开关总长DRC开关差分检查DRC开关7.Physical Mode从上往下走线出现T分支DRC开关Pad和Pad连接的DRC开关过孔使用类型DRC开关8.Spacing Modes默认全部选择所有间距相关的DRC开关都要打开9.Same Net Spacing Modes同名网络DRC开关,默认全部打开10.SMD Pins Modes盘中孔DRC默认是关闭的,可以用来检查孔是否打在SMD的pin上的情况11.开启DRC总开关On-line DRC是需要开启的,否则所有DRC都不起作用Physical规则设置下面介绍规则设置指导书之Physical规则设置点击Set-up-constraints-Constraint Manager打开规则管理器1.设置Physical规则2.打开时默认有个Default规则从左往右Line Width最小线宽最大线宽Neck最小线宽Neck的走线长度3.如果是差分规则,需要额外设以下参数从左往右最小线间距差分对之间的间距Neck走线差分之间的间距正公差负公差4.Pad-Pad connect选择Not Allowed,不允许Pad和Pad直接连接简而言之,就是允许盘中孔Physical规则匹配下面介绍基本规则设置指导书之Physical规则匹配1.在这里给网络匹配上相应的规则2.可以给同一类型的网络建立一个Net Class,匹配规则更方便选中需要的net右击创建Class3.同时如果是差分对的话,需要创建差分对选择需要的两个net,Create Differential PairPhysical Region下面介绍基本规则设置指导书之Physical Region1.空白的地方创建一个Region2.给新建的Region匹配一个规则,所有区域里面的Physical相关的都按照Region的规则来3.当部分网络想按照本身的规则来匹配,可以创建region-Class4.然后匹配回它原来的规则5.后面这些规则一般按照Physical里面设置的规则不修改Spacing规则设置下面介绍基本规则设置指导书之Spacing规则设置1.设置Line到其它的间距规则从左往右线到线,通孔pin,表贴pin,测试pin,通孔Via,盲埋孔,测试孔,微孔,铜皮,Bond finger,hole之间的间距2.设置pin到其它的间距,通孔pin和表贴pin3.设置Via到其它的间距4.设置shape到其它的间距5.设置Bond Finger到其它的间距7.设置盲埋孔之间的间距Spacing规则匹配下面介绍基本规则设置指导书之Spacing规则匹配2.可以把同一类网络创建一个Net Class给Net Class匹配间距规则会更为方便Spacing规则Class to Class 下面介绍基本规则设置指导书之Spacing规则Class to Class1.当我们需要给组和组之间设置一个间距规则时候需要用到这个功能在需要的Net Class地方创建一个Class to Class2.Class to Class匹配一个规则Spacing Region 下面介绍基本规则设置指导书之Spacing Region1.空白的地方创建一个Region2.给创建好的Region 匹配一个规则3.当网络需要在Region中需要按照自身的规则匹配时,可以创建RegionClass来匹配4.Region也支持Class to Class规则,点击ok即可5.设置好的如下图Same Net Spacing规则设置下面介绍基本规则设置指导书之Same Net Spacing规则设置8.设置Line到其它的间距规则从左往右线到线,通孔pin,表贴pin,测试pin,通孔Via,盲埋孔,测试孔,微孔,铜皮,Bond finger,hole之间的间距9.设置pin到其它的间距,通孔pin和表贴pin10.设置Via到其它的间距11.设置shape到其它的间距12.设置Bond Finger到其它的间距13.设置Hole到其它的间距14.打开或者关闭同名网络开关Same Net Spacing规则匹配下面介绍基本规则设置指导书之Same Net Spacing规则匹配3.匹配设置好的Same Net间距规则Same Net Spacing Region下面介绍基本规则设置指导书之Same Net Spacing Region6.空白的地方创建一个Region7.给创建好的Region 匹配一个规则8.当网络需要在Region中需要按照自身的规则匹配时,可以创建RegionClass来匹配Electrical Min Max Propagation Delay下面介绍基本规则设置指导书之Electrical Min Max Propagation Delay在这里可以设置走线的最短和最长的长度,这个过孔和pin delay的长度也会计算进去Electrical Total Etch Length下面介绍Allegro基本规则设置指导书之Electrical Total Etch Length这里可以设置走线的最短和最长的值,这里的值只是走线长度,不包含过孔和pin delay的长度Electrical Differentail Pair下面介绍基本规则设置指导书之 Electrical Differentail Pair这里一般用来设置差分的对内等长,在tolerance这里设置Electrical Relative Propagation Delay下面介绍基本规则设置指导书之 Electrical Relative Propagation Delay1.这里用来设置等长规则2.在创建Match Group之前要创建pin pair3.创建好pin pair之后,选中需要做等长的网络,创建Match Group4.创建好Match Group之后,Scope选择Global, Tolerance 输入公差值5.选择一个网络作为基准。

Allegro规则约束管理器的初始化设置

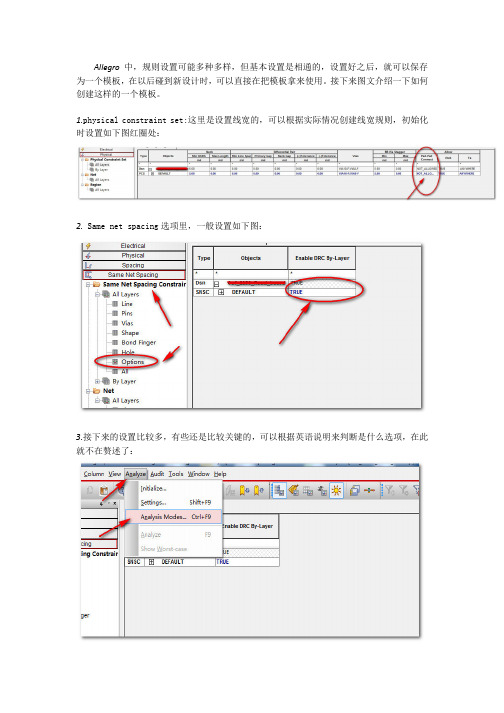

Allegro中,规则设置可能多种多样,但基本设置是相通的,设置好之后,就可以保存为一个模板,在以后碰到新设计时,可以直接在把模板拿来使用。

接下来图文介绍一下如何创建 样的一个模板。

1.physical constraint set: 里是设置线宽的,可以根据实际情况创建线宽规则,初始化时设置如下图红圈处

2. Same net spacing选项里,一般设置如下图

3.接下来的设置比较多,有些 是比较关键的,可以根据英语说明来判断是什么选项,在此就不在赘述了

3.2

3.4

3.6

3.8

3.10

在此,就介绍了constraint manager的初始化设置情况 在实际的设计中,可能需根据具体的情况,对设置进行一些调整。

Edited by kevin

2014/2/10。

allegro 约束规则设置

Allegro约束规则设置随着电子商务的不断发展,大量的交易评台涌现出来。

其中,Allegro 作为东欧最大的电商评台,拥有数百万的用户和商家。

为了保证评台的可持续发展和用户的利益,Allegro评台制定了一系列的约束规则,以规范和管理用户的行为。

本文将详细介绍Allegro评台的约束规则设置。

一、账户注册与使用规定1.1 注册要求在注册Allegro评台账户时,用户需要提供真实尊称、唯一识别信息号码等个人信息,以确保账户的真实性和有效性。

1.2 账户使用规定用户在使用账户进行交易时,需要遵守评台规定的交易流程和规则,不得有任何违反法律法规和评台规定的行为,如欺诈、虚假宣传、侵权等。

二、商品交易规定2.1 商品发布规定商家在发布商品时,需提供详细、真实的商品信息,不得发布违禁品或虚假商品,如有违反将面临相应的处罚。

2.2 交易行为规范买家和卖家在交易过程中应遵守规定的交易流程,如按时付款、按时发货,不得擅自修改订单或逾期交易。

三、评价与投诉规定3.1 评价规定买家在收到商品后,可对交易进行评价,评价内容需客观、真实,不得进行恶意、虚假的评价。

3.2 投诉处理规定对于买家或卖家的投诉,评台将进行核实和处理,如发现违规行为,将给予相应的处罚,并保障投诉方的权益。

四、违规处理规定4.1 违规行为处罚对于违反评台规定的行为,评台将根据情节严重程度给予相应的处罚,如下架商品、冻结账户等。

4.2 申诉机制对于被处罚的用户,可通过评台设立的申诉机制进行申诉,评台将重新审核相关情况,并依据申诉结果做出处理。

五、合作商家规定5.1 合作资格要求Allegro评台对合作商家有一定的资质和经营要求,包括经营年限、信誉度等。

5.2 合作权益合作商家可享受评台提供的一系列增值服务和营销支持,提升业务竞争力。

Allegro评台的约束规则设置是为了维护评台的正常运营秩序,保障用户和商家的合法权益,促进良好的交易环境。

用户在使用评台时,需严格遵守相关规定,如有违规行为,将面临相应的处罚。

allegro中如何设置class与class的规则

在Allegro中,设置类与类的规则通常涉及到约束管理器(Constraint Manager)的使用。

约束管理器是Allegro提供的一个强大的工具,用于定义、管理和应用各种约束,如物理约束、间距约束、高级约束等。

以下是如何在Allegro中设置类与类的规则的一般步骤:1. 启动约束管理器:在Allegro中,首先需要打开约束管理器。

这通常可以通过菜单栏的“工具”->“约束管理器”来完成。

2. 创建或编辑类:在约束管理器中,你可以创建新的类或编辑现有的类。

类是用来定义一组对象的约束规则的。

3. 设置类与类的规则:选择目标对象:首先,选择你想要应用约束的第一个对象或一组对象。

添加约束:在约束管理器中,选择适当的约束类型(例如,物理约束、间距约束等)。

设置参数:为所选约束设置适当的参数,例如距离、角度等。

关联类:为所选的约束指定一个或多个类。

这意味着你正在为一个或多个特定的对象组设置规则。

4. 应用约束:一旦你设置了所需的规则和参数,你可以将这些约束应用到你的设计中。

这通常是通过选择“应用”或“确定”按钮来完成的。

5. 验证和查看结果:在你应用约束之后,你可以通过验证工具来检查设计的合规性。

验证工具可以帮助你确定设计是否满足了你设置的约束条件。

6. 更新和编辑:随着设计的进行,你可能会需要更新或编辑这些约束。

你可以随时返回到约束管理器中进行这些更改。

7. 导出和导入:对于大型项目,你可能需要与其他团队成员共享这些约束。

Allegro 允许你导出这些约束到一个文件中,然后导入到其他Allegro项目中。

8. 使用脚本自动化:对于更高级的用户,Allegro还支持使用Tcl/Tk脚本来自动化和定制化这些过程。

Allegro约束规则设置详解SCC

Allegro约束规则设置详解SCCAllegro16.6约束规则设置详解前言:本文主要讲解Allegro16.6约束管理器的使用,从基本约束规则到高级约束规则的设置。

目录:一、基本约束规则设置1、线间距设置2、线宽设置3、设置过孔4、区域约束规则设置5、设置阻抗6、设置走线的长度范围7、设置等长7.1、不过电阻的NET等长7.2、过电阻的XNET等长7.3、T型等长8、设置通用属性9、差分规则设置9.1、创建差分对9.2、设置差分约束10、Pin Delay二、高级约束规则设置11、单个网络长度约束12、a+b类长度约束13、a+b-c类长度约束14、a+b-c在最大和最小传播延迟中的应用1、线间距设置(1)、设置默认间距规则点击CM图标,如下图所示,打开约束管理器。

单击Spacing,再点击All Layers,如下图所示。

右边有一个DEFAULT就是默认规则,我们可以修改其值。

按住Shift键,点击第一个和最后一个即可选中所示,然后输入一个值,这样就都修改了,如下图所示(2)、定义特殊的间距约束点选Default按鼠标右键,执行Create-Spacing CSet加入新规则。

取一个有意义点的名字,如下图所示,单击OK。

按住Shift键选中所有,输入12,回车。

然后为所需要设置的网络分配规则单击左边的Net-All Layers,在右边工作簿中,为GND网络设置12MIL_SPACE规则,在Referenced Spacing CSet下选中12MIL_SPACE,如下图所示(3)、设置Class-Class规则若针对不同的信号群组有不同的间距规则,则需要设置Class-Class选到Net Class-Class后,在右边CLOCK(2)上右键选择Ctreat- Class-Class...,如下图所示选择2个不同的Net Classes,如下图所示,单击OK如下图所示。

在右边的Referenced Spacing CSet栏可以修改其值。

allegro差分线分组约束规则设置

allegro差分线分组约束规则设置摘要:I.简介- 什么是Allegro- 差分线分组约束规则的作用II.差分线分组约束规则设置- 设置规则概述- 具体设置步骤- 步骤1:定义分组- 步骤2:设置差分线属性- 步骤3:应用规则III.应用实例- 实例1:设置差分线分组约束规则- 步骤1:创建工程- 步骤2:添加元件- 步骤3:设置差分线分组约束规则- 实例2:使用差分线分组约束规则进行设计优化- 步骤1:发现问题- 步骤2:应用规则优化设计- 步骤3:验证优化结果IV.总结- 差分线分组约束规则的重要性- 在实际应用中的优势正文:I.简介Allegro 是一款广泛应用于PCB 设计领域的EDA 工具,可以帮助设计师快速、高效地完成电路板设计。

在Allegro 中,差分线分组约束规则设置是一项关键功能,它能够帮助设计师更好地管理差分线,提高设计效率和质量。

差分线分组约束规则主要用于对差分线进行分类和约束,以便在设计过程中更加方便地管理和调整。

通过设置差分线分组约束规则,可以确保差分线在设计中的正确性和一致性,避免因差分线问题导致的设计错误。

II.差分线分组约束规则设置在Allegro 中设置差分线分组约束规则主要包括以下几个步骤:1.定义分组:首先,设计师需要根据设计需求,定义差分线的分组。

分组可以根据差分线的功能、性能等特点进行划分,以便于后续的管理和调整。

2.设置差分线属性:在定义分组的基础上,设计师需要为每个分组设置差分线的属性。

这些属性包括差分线的宽度、间距、过孔等参数,可以根据设计规范和实际需求进行调整。

3.应用规则:设置好差分线属性后,设计师需要将规则应用到实际的设计中。

在Allegro 中,可以通过菜单命令或脚本语言等多种方式应用差分线分组约束规则,确保差分线在设计中的正确性和一致性。

III.应用实例以下是两个关于差分线分组约束规则设置的应用实例:实例1:设置差分线分组约束规则1.创建工程:首先,设计师创建一个新的Allegro 工程,并导入所需的元器件和设计文件。

Allegro constraint 设定之范例讲解

設定與其他trace的space

設定space

15

Constraint 設定之範例講解-11

Group1設定BUS name (HA1) Group2設定BUS name (HA2)

設定與其他trace的space

設定與其他trace的space

設定BUS name (HC1)

16

Constraint 設定之範例講解-12

24

Constraint 設定之範例講解-20

設定BUS name (LVDS) 1.依據阻抗表設定100ohm的線寬及線距 2.設定differential pair最小的space 3.設定differential pair 4.設定與其他trace的space

25

Constraint 設定之範例講解-21

設定BUS name (DDR-CLK) 1.依據阻抗表設定70ohm的線寬及線距 2.設定differential pair最小的space 3.設定differential pair

19

Constraint 設定之範例講解-15

設定與其他trace的space 設定BUS name (DDRA-D1), 其餘GROUP以此類推

23

Constraint 設定之範例講解-19

設定BUS name (DVI) 設定BUS name (DVO) 1.依據阻抗表設定100ohm的線寬及線距 2.設定differential pair最小的space 3.設定differential pair 4.設定與其他trace的space

設定BUS name (HC2)

17

Constraint 設定之範例講解-13

設定BUS name (DMI)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

A llegro中的约束规则设置Allegrophan刚好五个字修订记录日期版本描述作者2008-12V1.0初版,学完的总结。

适用于Cadence15.5版本。

Allegrophan 2009-09-08V1.1小改,修改部分措辞Allegrophan2009-10-14V1.2小改,更正、修改几个错漏之处。

添加一些说明性文字。

感谢群里的佳猪、梦姑娘等朋友的指正!Allegrophan目录一:Physical(Line/vias)rule物理特性(线宽和过孔)约束设置: (4)1)“Set values”设置约束特征值 (5)2)“Attach property”绑定约束 (6)3)“Assignment table”约束规则分配 (8)二“Spacing rule”间距约束设置 (9)1)“Set values”设置约束特征值 (9)2)“Attach property”绑定约束 (10)3)“Assignment table”约束规则分配 (11)三Constraint areas区域约束设置 (12)四Allegro中走线长度的设置 (13)1)差分线等长设置 (13)2)一组Net等长 (16)3)XNet等长 (17)线宽、线距、区域的约束主要在“Constraints Sys ”中设置,点击“Setup/Constraints ”或点击图标打开“Constraints Sys”窗口,如下:“Constraints Sys ”窗口分两个级别,第一级别有两类:Standard design rules 和Exte Extendednded design rules 。

Standard design rules 仅有一级分类,点击“Set standard values ”设置默认约束值,如下:“Extended design rules”下一级分为三类不同约束设置:Spacing rule间距约束设置、Physical(Line/vias)rule物理特性(线宽和过孔)约束设置和Constraint areas区域约束设置。

它们的下一级分类其实是具体约束设置的操作步骤,分别有:“Set values”、“Attach property”、“Assignment table”和“Set DRC modes”。

一:Physical(Line/vias)rule物理特性(线宽和过孔)约束设置:我们以以下的DDR2部分的线宽要求为例进行设置:间距,其中B)的线宽线距可用于Neck mode在BGA区域的出线。

1)“Set values”设置约束特征值在窗口上方空白处填入新约束名称,然后点击“ADD”,新的约束就产生了,接下来就按部就班在相应栏填入需要的值。

由于DDR2有单端线、差分线两种,我们可以相应的设置两种Physical特性如:DDR2_50OHM,DDR_100OHM。

如下图所示:过孔规格在“Via list property”中设定,一般设定在默认约束规则下。

在左侧数据库可用via 列表中点击所需规格钻孔,右侧“Current via list”就会显示选中钻孔,可多选。

Min line widht:最小线宽Max line widht:最大线宽,填0=∞Min neck widht:Neck模式最小线宽Max neck length:Neck模式最大走线长度DiffPair primary gap:首选差分间距(单端线可不填)DiffPair neck gap:Neck模式差分间距(单端线可不填)2)“Attach property”绑定约束“Attach property”是绑定约束的操作,操作对象是信号(以net名来区分),将相应类别的约束名称与信号绑定,该信号就会遵循绑定约束的设定。

点击后可以直接框选板上各Net选取,也可以点击右侧的more,在弹出的“Find by Name or Preoperty”选择框中选取。

“Name filter”处填写要绑定的Net名,“?”可以代替任意一个字符,“*”可以代替任意长字符,如我们要给DDR2的DQS差分线添加“DDR_DQS”的“Net_Physical_Type”属性,就可以输入“*dqs*”,就可以将所有DQS、DQS#的Net过滤出来,如图:点击“All”选定net,点击“Apply”,出现“Edit Property”窗后,在左侧下拉选项中选择约束类型“Net_Physical_Type”,然后在右侧相应内容后填入约束名称“DDR_DQS”,点击“Apply”,这样就完成了约束绑定,如图:3)“Assignment table”约束规则分配“Assignment table”是约束规则分配列表,分配不同情形下适用怎样的规则。

Physical rule 的约束分配列表如下:第一列“Net Physical Property”:在2)“Attach property”中绑定的约束第二列“Area Property”:约束绑定区域第三列“Physical Constraint Set”:在1)“Set values”中设置的约束特征值关于约束绑定区域我们以后再说,那么这四行的意思就是:绑定约束“DDR_DQS”的信号在“BGA”区域内应用Physical约束“BGA”绑定约束“NO_Type”的信号在“BGA”区域内应用Physical约束“DEFAULT”绑定约束“DDR_DQS”的信号在“NO_Type”区域内应用Physical约束“DDR_100OHM”绑定约束“NO_Type”的信号在“NO_Type”区域内应用Physical约束“DEFAULT”二“Spacing rulerule””间距约束设置Spacing rule的设置和Physical rule设置大同小异,方法基本形同。

我们以DDR2一组DQ 线的线距要求为例进行设置:一组DQ线DQSet00包含以下信号:DDR2A_DQ[7:0]:8根DQ线,单端DDR2A_DM0:一根DM,单端DDR2A_DQS0/DDR2A_DQS#0:一对DQS,差分线要求:组内间距3倍线宽,DQS/DQS#与其他信号间距不小于5倍线宽1)“Set values”设置约束特征值同样在窗口上方空白处填入新约束名称,然后点击“ADD”,新的约束就产生了。

由于我们要设置的间距有3倍线宽、5倍线宽两种,我们可以相应的设置两种Spacing特性:“3W”,“5W”。

如下图所示:V1.1→V1.2要注意这里的“3W”、“5W”是对那种线的3倍、5倍!现在是图中设置的是L05_MD2层的差分线,所以5W应该是MD2层差分线宽的五倍:3.5*5=17.52)“Attach property ”绑定约束Spacing rule 的绑定约束的操作和Physical rule 设置基本相同。

选取“DDR2A_DQ[7:0]”、“DDR2A_DM0”绑定约束“3W/5W”,如图:同样的方法给“DDR2A_DQS0/DDR2A_DQS#0”绑定约束“5W ”。

V1.1→V1.2这里的名字是可以随便起的,但是为了阅读方便,和便于以后同行的改版,名字尽量取得简单易懂,做到以后看到名字,就可以明白表达的什么意思。

3)“Assignment table”约束规则分配Spacing rule的约束分配列表如下:举例,红色下划线的三行的意思是(关于约束绑定区域以后再说):绑定Spacing约束“3W/5W”的信号和绑定Spacing约束“5W”的信号在“BGA”区域内应用Spacing约束“BGA”绑定Spacing约束“3W/5W”的信号和绑定Spacing约束“3W/5W”的信号在“No_Type”区域内应用Spacing约束“3W”——即组内间距3W绑定Spacing约束“5W”的信号和绑定Spacing约束“No_Type”的信号在“No_Type”区域内应用Spacing约束“BGA”“5W”——即DQS和其他信号间距5WV1.1-->V1.2:此处应为5W这里要说一下约束的起名,我开始学设置时,约束的起名比较乱,如DDR的DATA线,线宽约束值叫DDR_DATA,绑定线宽约束名也叫DDR_DATA,间距约束值也叫DDR_DA TA,绑定线距约束名还叫DDR_DATA,到最后在约束分配表中分配的时候,我自己都被搞晕了。

后来总结了一下,优化了起名方式,如:DDR单端线阻抗50Ω的线宽约束值:DDR_50OHM间距3W、10Mil的线距约束值:3W、10MilDDR组内间距3W组外间距5W的绑定约束:DDR_3W/5W这样约束分配起来就清晰明了了很多,如间距绑定DDR_3W/5W与DDR_3W/5W在No_Type区域,明显他们是同组,所以应用组内间距约束值3W。

三Constraint areas 区域约束设置在前面的Physical 和Spacing 设置分配表中,为什么有个区域“No_Type ”和“BGA ”?这是因为有些区域约束是不可能达到的,比如在BGA 封装的CPU 内,引线出来,线间距不可能达到30,20甚至10个mil 。

在这些地方,如果你也按照这个约束那么你的PCB 中的DRC 就不可能消的掉。

这时一个解决办法就是把这些地方划为一个Area ,然后给它加上Net_Physical_Type 和Net_Spacing_Type 属性。

针对这些Area 内,设定合适的、比较宽松的约束值。

如果不设置,也就是没有区域约束的地方,就是No-Type 。

提示:约束区域是shape 。

具体做法是先在“Set values ”中各添加Physical 和Spacing 的约束值“BGA ”,填上相对比较宽松的、合理的值。

Constraint areas 中选Add ,(注意这时的绘图层),选择好画shape 的工具,在工作区绘制shape 。

如图:点击“Attach property ,shapes ”选刚才画的shape ,绑定约束Net_Physical_Type 和Net_Spacing_Type 。

绑定后shape 属性如图:1:点击Add ,添加区域3:画出的约束区域另外,也可以直接用画shape的工具添加约束区域,工作层应选:BOARD GEOMETRY →CONSTRAINT_AREA。

绑定约束也可以用“Edit/Properties”(默认快捷键Ctrl+P)。

出现“Edit Property”窗后,操作对象(Find)视情况选net或shapes。

以上约束设置也可以在约束管理器(Constraint Manager)中设置,我没用过,感兴趣的朋友可以自己研究下。