Allegro中等长线或差分线设置的一些方法

allegro建立差分线规则

allegro建立差分线规则

建立差分线规则的方法如下:

1. 确定差分线的标准:差分线指的是MACD指标中的DIF线

和DEA线之间的差值。

一般情况下,当DIF线由负值变为正

值时,表示买入信号;当DIF线由正值变为负值时,表示卖

出信号。

2. 设定阈值:根据市场经验和个人风险偏好,设定一个合适的阈值来判断买入和卖出信号。

比如,当DIF线大于等于阈值时,触发买入信号;当DIF线小于等于阈值的负值时,触发

卖出信号。

3. 确定持仓策略:根据买入和卖出信号,制定持仓策略。

比如,当触发买入信号时,可以全仓买入;当触发卖出信号时,可以全部卖出或者部分卖出。

4. 设置止损和止盈点:为了控制风险,可以设置一定的止损和止盈点。

比如,当买入后的价格下跌到设定的止损点时,自动卖出;当买入后的价格上涨到设定的止盈点时,自动卖出。

5. 定期回顾和调整规则:市场行情时刻变化,所以需要定期回顾和调整差分线规则。

可以根据历史回测结果和市场环境来优化规则,提高交易效果。

需要注意的是,差分线规则只是一种参考,投资者应根据个人

情况和市场情况综合考虑。

此外,差分线规则也具有一定的局限性,不能完全依赖于它进行投资决策。

Allegro16.6约束规则设置详解_SCC

Allegro16.6约束规则设置详解_SCCAllegro16.6约束规则设置详解前言:本文主要讲解Allegro16.6约束管理器的使用,从基本约束规则到高级约束规则的设置。

目录:一、基本约束规则设置1、线间距设置2、线宽设置3、设置过孔4、区域约束规则设置5、设置阻抗6、设置走线的长度范围7、设置等长7.1、不过电阻的NET等长7.2、过电阻的XNET等长7.3、T型等长8、设置通用属性9、差分规则设置9.1、创建差分对9.2、设置差分约束10、Pin Delay二、高级约束规则设置11、单个网络长度约束12、a+b类长度约束13、a+b-c类长度约束14、a+b-c在最大和最小传播延迟中的应用1、线间距设置(1)、设置默认间距规则点击CM图标,如下图所示,打开约束管理器。

单击Spacing,再点击All Layers,如下图所示。

右边有一个DEFAULT就是默认规则,我们可以修改其值。

按住Shift键,点击第一个和最后一个即可选中所示,然后输入一个值,这样就都修改了,如下图所示(2)、定义特殊的间距约束点选Default按鼠标右键,执行Create-Spacing CSet加入新规则。

取一个有意义点的名字,如下图所示,单击OK。

按住Shift键选中所有,输入12,回车。

然后为所需要设置的网络分配规则单击左边的Net-All Layers,在右边工作簿中,为GND网络设置12MIL_SPACE规则,在Referenced Spacing CSet下选中12MIL_SPACE,如下图所示(3)、设置Class-Class规则若针对不同的信号群组有不同的间距规则,则需要设置Class-Class选到Net Class-Class后,在右边CLOCK(2)上右键选择Ctreat- Class-Class...,如下图所示选择2个不同的Net Classes,如下图所示,单击OK如下图所示。

在右边的Referenced Spacing CSet栏可以修改其值。

Allegro16.6设置等长规则

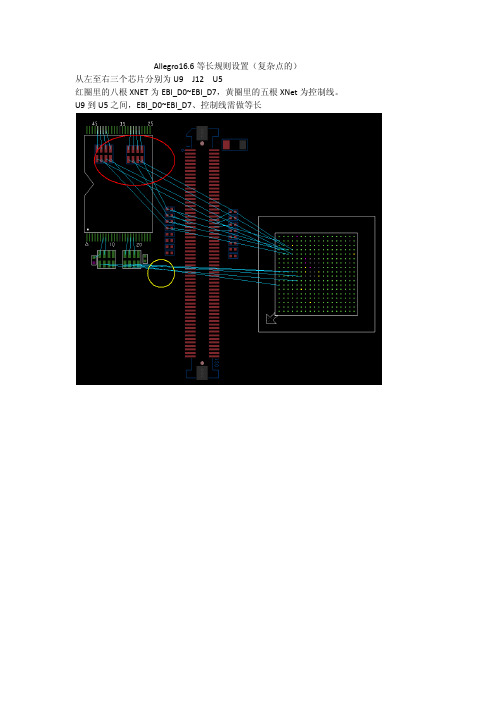

Allegro16.6等长规则设置(复杂点的)从左至右三个芯片分别为U9 J12 U5红圈里的八根XNET为EBI_D0~EBI_D7,黄圈里的五根XNet为控制线。

U9到U5之间,EBI_D0~EBI_D7、控制线需做等长多出来的八根XNET为EBI_D8~EBI_D15J12到U5之间EBI_D0‐ EBI_D15做等长接下来开始步骤:(设模型、X‐NET就不说啦,坛子里有很多说的挺清楚的)将EBI_D0~EBI_D15设为一个Class,EBI_D将EBI_D0~EBI_D15设PINPAIREBI_D0~EBI_D7设置两组PINPAIREBI_D8~EBI_D15设置一组PINPAIR设EBI_D0 拓扑Set‐Constraint红框中填好点ADD再新增另一个规则点ADD点OK后回到以下界面,FILE‐Update Constraint Manager点是出现两组MGrp,每组下面只出现一对,因为仅对EBI_D0设了规则。

EBI_D0和EBI_D1~D7的拓扑一样的,将刚才生成的ElecCset赋予它们赋予它们的同时,两组MGrp里的PPr也在增多但EBI_D8~D15的拓扑和它们不一样,所以得重新建拓扑设规则省略几步,和之前设的时候一样的点是,可以看到EBI_D8被赋予规则EBI_D8,EBI_D9~D15拓扑与EBI_D8一样的,所以把EBI_D8这一规则分别赋予它们。

目前为止,EBI_D0~D15从U5到J12就做了等长,走线时就有控制进度条显示但是从U5到U9这一段还有几根控制线未加进来找到这几根控制线,add to MatchGroupEBINAND这一MatchGroup里就有这些XNET了。

红色框中选择ALL DRIVERS..红色框中改为0mil:100milU9到U5之间,EBI_D0~EBI_D7、控制线就做好等长啦、这种设等长的方式思路挺清晰的,所以就推荐给大家,或者是给还不会设等长的一点参考。

如何在Allegro16.3里设置Xnet并进行等长设置

附件是一篇网上找到的文章,此文详细介绍了如何设置Xnet以及进行等长设置走线。

本人的应用相对更简单,由于不是经常画板子,所以对于如何使用Xnet常常忘记,而本文介绍的相对复杂,为了在每次画板子的时候相对快速的使用Xnet,特记录本人使用Xnet的过程于此。

首先,介绍本人为何要使用Xnet。

本人使用Xnet的场合主要有两种场合,一种是走线路径阻抗匹配,所以走线中串接了一个匹配电阻,如果需要等长,所以要给这一组走线设置Xnet;另一种是高速差分走线以及像Altera的高速Transciever的差分走线一般都需要对高速差分线进行AC耦合,所以每根线上串接了一个0.1uF的电容,而差分走线都需要进行等长,所以需要计算电容两端走线之和来进行等长控制。

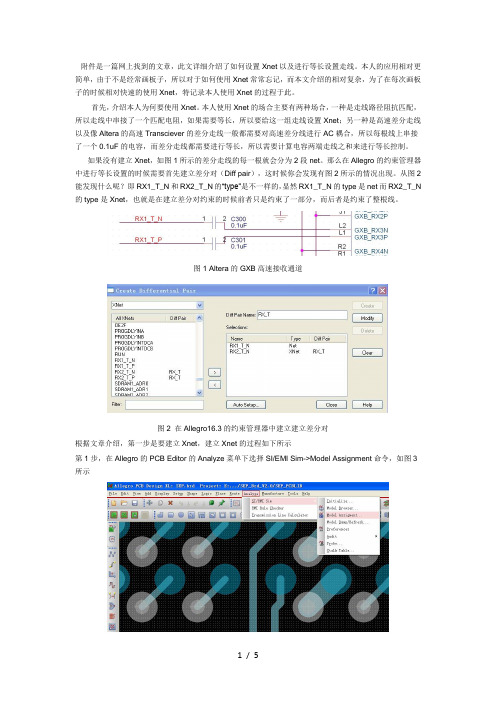

如果没有建立Xnet,如图1所示的差分走线的每一根就会分为2段net。

那么在Allegro的约束管理器中进行等长设置的时候需要首先建立差分对(Diff pair),这时候你会发现有图2所示的情况出现。

从图2能发现什么呢?即RX1_T_N和RX2_T_N的“type”是不一样的,显然RX1_T_N的type是net而RX2_T_N 的type是Xnet,也就是在建立差分对约束的时候前者只是约束了一部分,而后者是约束了整根线。

图1 Altera的GXB高速接收通道图2 在Allegro16.3的约束管理器中建立建立差分对根据文章介绍,第一步是要建立Xnet,建立Xnet的过程如下所示第1步,在Allegro的PCB Editor的Analyze菜单下选择SI/EMI Sim->Model Assignment命令,如图3所示图3 启动开始建立Xnet第2步,进去以后会看到如图4所示的界面,由于差分线中串接的是0402封装的0.1uF的电容,所以选择此项。

可以看到此项下包含了所有工程里使用的所有的该类电容,选择你需要建立Xnet的电容,如图5所示。

图4图5第3步,在上述图4,和图5中选择相应的电容,这里是C300,(注意,这里我们事先已经将C301建好了Xnet),然后点击“Create Model”命令进入创建模型界面,如图6所示。

allegro 等长规则设置方法

allegro 等长规则设置方法allegro是一种用于信号处理和控制系统开发的开源信号处理库。

它支持等长规则设置,可以在控制台或命令行中使用。

以下是使用 allegro 等长规则设置的基本步骤:1. 创建等长规则:在 allegro 中,可以使用 `规则` 命令创建等长规则。

例如,要创建一个长度为 10 的等长规则,可以使用以下命令:```let allele = channel(0) | channel(1) | channel(2) | channel(3) | channel(4) | channel(5) | channel(6) | channel(7) | channel(8) | channel(9) | channel(10)allele << 1```2. 设置规则条件:在创建等长规则后,需要设置规则的条件。

例如,要设置规则只有在信号值为 0 时才会触发,可以使用以下命令:```let allele = channel(0) | channel(1) | channel(2) | channel(3) | channel(4) | channel(5) | channel(6) | channel(7) | channel(8) | channel(9) | channel(10)allele << if all(get(allele, "值")) == 0 then "0" else "1" end```这里使用了 `get(allele, "值")` 来获取信号值,如果信号值为 0,则返回 0,否则返回 1。

`all(get(allele, "值", 0))` 表示计算所有信号值之和,如果结果为 0,则返回 0,否则返回 1。

3. 运行规则:等长规则准备好后,可以使用 `send(allele)` 命令将规则触发。

Allegro中等长设置方法

创建模型:

如果排阻PinNumber顺序是这样的,则:

注:Pin Number与Pin Number之间有空格

创建模型:

d)完成模型设置后,查看这个排阻的Net属性,在Net name下面会多 一个Net名字,这表示Xnet已经创建好了。

导入PACAGE长度:

1、File->Import->Pin Delay:

2、Pin Delay File是芯片厂提供的 文件,因没有这一文件,暂时没法演示。

等长规则应用:

i)完成的效果,如下图:

总结

这是通过模型来设置等长规则的一种 方法,如果Xnet已经创建好了,则在 Constraint Manager一样可以设置,会 更方便,之所以提出这种方法,只是多 一种选择,当匹配比较复杂的时候,模 型创建就相对复杂

设置等长规则:

设置等长规则:

设置等长规则:

c)选择菜单Set->Constraints,出现如下窗体:

设置等长规则:

Rule Name:等长规则名字,这里可以随便输入,不过最好方便辨认 From:开始Pin To:结束Pin Scope:规则适应范围

Local:适用本网络 Global:适用所有网络 Bus:适用所在Bus Class: 适用所在Class Delta Type:Delta匹配类型,Delta为与基准线对比值,如果一组线要 求等长,我们可以把Delta设为None,或把Delta值设为0 Delay: 延迟 Length:长度,一般都设长度 Delta: 设定值 Tol Type: 误差类型 Tolerance: 误差范围。

f)在Constraint Manager中就有更新提示:

allegro等长设置总结.doc

对于专业的PCB layoutlay比较复杂PCB就亲自操刀,allegro当时向他们讲解如何操作,于是就准备亲自动手整理一开始之前,如果信号线长度差别较大,对应的延时就会有较大的差别,关于误差值,DDR2BUS CM,进行CM的DDR28BUS选中信号---右键选择create---BUSBUS OK BUSBUSBUSBUS BUS1.BUS SiXplorer…2.3.1Rel Prop Delayrule name From和ToFrom和To.Delta和Tolerance就是误差长度,如0mil和25mil,50mil,信号线和参考基准信号线25milAdd—Apply—OK.CM File---update CM.constraint manager.1.回到CM rule nameBUS name的MGrp2.MGrp的name,右键analyzelength,升序or降序,1.delay tune2.1.BUS中的信号的模型不一样,如MGrp2.BUS rule name建的rule name MGrp 关于XnetXnetXnet1.Analyze>SI/EMI Sim>Model…DC net,直接YesModel2.model Detype value/refdes3.点选create mode…4.okModenameCircuit typeSingle pins116pin,就连着,接着215相当于另一个电阻…pin number之间用空格隔开,如1和1616和22和15之间…net的property Member of XNet:…XnetPin Pair1.在BUS create---pin pairok net pin pair netppr pin pair2.match group MGrp BUS中所有的ppr,右键create...membership3.MGrp就ok4.set target有时,Pin pin type,pin type,pin pair1,Edit>Properties…2,在Find栏位中勾选Pin3,在PCB中选中需要修改Pin Type的Pin4,Edited by Kevin2013/11/10。

Allegro线宽、间距、等长、差分

A llegro 中的约束规则设置Allegrophan 刚好五个字w w w .pc b b b s .c o m修订记录日期版本描述作者2008-12V1.0初版,学完的总结。

适用于Cadence 15.5版本。

Allegrophan 2009-09-08V1.1小改,修改部分措辞Allegrophan 2009-10-14V1.2小改,更正、修改几个错漏之处。

添加一些说明性文字。

感谢群里的佳猪、梦姑娘等朋友的指正!Allegrophanw w w .p c b b b s .c o m目录一:Physical (Line/vias )rule 物理特性(线宽和过孔)约束设置:.............41)“Set values”设置约束特征值....................................................................52)“Attach property ”绑定约束.....................................................................63)“Assignment table ”约束规则分配........................................................8二“Spacing rule”间距约束设置...........................................................................91)“Set values ”设置约束特征值................................................................92)“Attach property ”绑定约束.................................................................103)“Assignment table ”约束规则分配......................................................11三Constraint areas 区域约束设置......................................................................12四Allegro 中走线长度的设置............................................................................131)差分线等长设置......................................................................................132)一组Net 等长..........................................................................................163)XNet 等长................................................................................................17w w w .p c b b b s .c o m线宽、线距、区域的约束主要在“Constraints Sys ”中设置,点击“Setup/Constraints ”或点击图标打开“Constraints Sys ”窗口,如下:“Constraints Sys ”窗口分两个级别,第一级别有两类:Standard design rules 和Exte Extended nded design rules 。

allegro等长设置总结.doc

对于专业的PCB layoutlay比较复杂PCB就亲自操刀,allegro当时向他们讲解如何操作,于是就准备亲自动手整理一开始之前,如果信号线长度差别较大,对应的延时就会有较大的差别,关于误差值,DDR2BUS CM,进行CM的DDR28BUS选中信号---右键选择create---BUSBUS OK BUSBUSBUSBUS BUS1.BUS SiXplorer…2.3.1Rel Prop Delayrule name From和ToFrom和To.Delta和Tolerance就是误差长度,如0mil和25mil,50mil,信号线和参考基准信号线25milAdd—Apply—OK.CM File---update CM.constraint manager.1.回到CM rule nameBUS name的MGrp2.MGrp的name,右键analyzelength,升序or降序,1.delay tune2.1.BUS中的信号的模型不一样,如MGrp2.BUS rule name建的rule name MGrp 关于XnetXnetXnet1.Analyze>SI/EMI Sim>Model…DC net,直接YesModel2.model Detype value/refdes3.点选create mode…4.okModenameCircuit typeSingle pins116pin,就连着,接着215相当于另一个电阻…pin number之间用空格隔开,如1和1616和22和15之间…net的property Member of XNet:…XnetPin Pair1.在BUS create---pin pairok net pin pair netppr pin pair2.match group MGrp BUS中所有的ppr,右键create...membership3.MGrp就ok4.set target有时,Pin pin type,pin type,pin pair1,Edit>Properties…2,在Find栏位中勾选Pin3,在PCB中选中需要修改Pin Type的Pin4,Edited by Kevin2013/11/10。

allegero设置差分和等长

1,设置差分

要设置的选项包括

GATHER CONTROL 为include

TOLERANCE 为5mil

LINE SPACE MIN 为5mil

PRIMARY GAP 为7Mil PRIMARY WIDTH 为6.1mil NECK GAP 为5mil

2,设置等长

进入ACM ALLEGRO CONSTRAINT MAGANEMT

比如现在要将E_AD1和E_AD2设为等长组,我们先将这两个设为BUS1

首先,将E-AD1和E-AD2选中右键CREATE –BUS

建立BUS1后上面出现了BUS1

然后我们在BUS1下的点E-AD1 E-AD2 右键

这样就出现了一个BUS 和一个等长组MG2 ,

MG右键ANALYZE分析长度

在SCOPE 下设置GLOBAL

DELTA TOLERANCE 设置0mil

右键CHANGE 设置误差范围0mil –到50mil 这里误差范围设成50mil 就是表示大于或小于50mil范围是正确的。

然后右边选定一个目标值

设为目标值。

注意我们加入等长组后,我们分析后下面为变成引脚对的形式。

但是有时候会出现这种情况

有时候我们点分析后,后面不会出现长度报告

这个时候我们要将它们创建成PIN PAIR,比如U-AD0 UAD1 我们要CREATE PIN PAIR之后然后再加入到等长组里面即可。

我们可以在ALLEGRO中EDIT PROPERTITY .点NET

在右边加入BUS这个属性之后就可以在allegro constraint magager 中发现已加入了BUS 或者我们可以直接进入约束管理中加入BUS。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

以千兆以太网为例说明,差分等长设置;

首先,拉好差分线;

打开约束管理器,创建BUS(也可以再拉线之前创建,个人习惯拉线前设好所有的总线BUS);

创建MG;

差分的对内等长设置;

其他信号等长线路(点对点或一组像具有相同模型)可以参照以上做法!

若一组线内有多种模型;一般选择使用相同模型最多的一根做模型创建MG;驱动后不同模型会自动显示红色,把显示红色的clear掉规则,设置点对点的PIN pair ,然后membership到之前创建的MG即可,等长范围手动添加。

创建不同的模型和PIN pair 最后都是要membership到一个每个里面,这样才能一起等长;

Pin pair很费时间,如果拖的器件多了,做起来很费事。