晶体的串联和并联谐振图解

并联谐振电路(2)串并联谐振电路

而当 R >

L

C 时,电路不会发生谐振,因为此时 0 是虚数。

当电路发生谐振时,电路相当于一个电阻(或电导):

Z(0 )

R0

R2

(0L)2

R

L RC

Y (0 ) G0

R2

R

(0 L)2

RC L

返回 上页 下页

谐振电路

电容可以调节时,情况有所不同。

由C

R2

L

( L)2

可以看出,不论R、L、ω为何

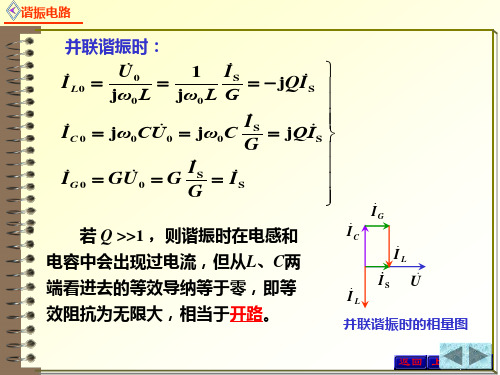

IL IL IS U

并联谐振时的相量图

返回 上页 下页

谐振电路

谐振时有 QL QC 0

QL

UI L

s in 90o

UI L

U

U

0L

1 U2

0L

QC UI C sin(90o ) UI C U0CU 0CU 2

表明谐振时,电感的磁场能量与电容的电场能量相互交换。

电容和电感上的总能量为

W

WL

=

1 2

LQ2 IS2mcos2 (ω0t )

WL

=

1 2

LiL2

=

1 2

LQ

2

I

2 Sm

sin2

(ω0

t

)

电场能量 磁场能量

W

= WL

+ WC

=

1 2

LQ2 IS2m

=

LQ2 IS2

=

LI

2 L

常量

上式表明,电感和电容的能量按正弦规律变化,最大 值相等 ;它们的总和是常量,不随时间变化,正好等于最 大值。

值,

调节电容C总能达到谐振。

Beq

=

ωC

晶体的串联和并联谐振图解

晶体的串联和并联谐振图解

石英晶体的外壳上标有器件的额定工作频率,但那只是一个近似值,实际上晶体有多个谐振频率,即使在理想情况下也是如此。

图1显示了理想晶体的等效电路,其中只有三个电路元件,串联的电容C1和电感L1、与该L1 C1串联对并联的另一个电容C2。

图1:理想石英晶体的等效电路

在特定的串联谐振频率,输入阻抗Z为零,L1和C1处于串联谐振。

电容C2与此无关。

然而,在特定的并联谐振频率,输入阻抗Z达到无穷大。

这是C2与L1 C1的串联组合发生并联谐振的频率,呈现电感性阻抗。

要使L1 C1对在并联谐振时呈现感性,并联谐振必须发生在比串联谐振更高的频率。

因此,并联谐振频率只能比串联谐振频率高,即使只高一点点。

并联谐振频率绝不会低于串联谐振频率。

至于哪个谐振对你更重要,则取决于应用。

借助不复杂的数学运算,阻抗Z可以表示如下:

图2:阻抗公式

串联谐振频率:Fseries = 1/(2 * pi * sqrt(L1 C1))

并联谐振频率:Fparallel = 1/(2 * pi * sqrt(L1 C1 C2 /(C1 + C2)))

图3:串联和并联谐振的相对位置。

第29讲并联谐振电路-课件

G ωLGG L ρ

0

(电压响应)

感性

容性

三、实用的简单并联谐振电路

通常,电容器损耗比电感线 圈的损耗小很多,可忽略不 计,故等效电路如右。

Y(j)jCr1jL

I + r

S U

_

r2(rL)2jCr2(L L)2

当 Q 很 高 ,r2 时 ( L)2

I 1

I2

1

jωL j ω C

Y (j ) ( L r)2j C 1 L G j C 1 L

C2

定量Z分(j 析)jL3jj L L1 1 jj 1 1 C C2 2 jL31 j2L L 11C2 j(L1L3)3L1L3C2 12L1C2

分别令分子、分母为零,可得:

串联 谐振

01

1

L1 L3 L1 L3

C2

>

02

1 L1C2

并联 谐振

定性分析

2

1 L1C2

=2 时, 并联谐振

C3

L1

C2

<2 时,并联支路呈感性,发生串联谐振

定量分析

Z(jω)

1

jC3

jL1

1

jC2

jL1

1

jC2

1

jC3

jL1

1ω2L1C2

j1ω2L1(C2 C3)

C3(1ω2L1C2)

分别令分子、分母为零, 可得:

< 串联

谐振

ω1

1 L1(C2 C3)

ω2

1 L1C 2

并联 谐振

推广:

对于任意含有电抗元件的一端口电路, 在一定 的条件下, 若其端口电压与电流同相(这时电路呈 电阻性, 阻抗的虚部为零或导纳的虚部为零),则称 此一端口电路发生谐振, 此时相应的激励频率称为 谐振频率。

串联谐振电路ppt课件

串联谐振的电路特性

在信号源电压有效值 U 保持不 变的情况下,谐振时电流有效值 I0=U/Z=U/R达到最大值,并且与同相 位。电流I随ω的变化如下图所示:

谐振时,因 X=0 ,所以谐振 时电路的阻抗 Z0=R ,是一个纯电 阻,此时阻抗为最小值。阻抗 Z 随ω的变化如下图所示:

14

串联电路谐振时,电阻上的电压

I

U

R,L,C 电路

5

发生 谐振

2.1 串联谐振电路

2、串联谐振的条件:

Z R j(ωL 1 ) R j( X L X C ) ωC R jX

+

I

R j L

1 j C

感抗=容抗

U

_

当 X 0

ω 0L 1 0C

时,电路发生谐振。

谐振条件 谐振的定义

含有R、L、C的一端口电路,在特定条件下出现端口电 压、电流同相位的现象时,称电路发生了谐振。 阻抗:在具有电阻、电感和电容的电路里,对交流电所 起的阻碍作用叫做阻抗。阻抗常用 Z 表示。阻抗由电阻、 U Z R 感抗和容抗三者组成,但不是三者简单相加。阻抗的单位 I 是欧。

Bw w2 w1 w0 / Q

Q值越高,谐振曲线越尖锐,选择性越好,但

通频带越窄。二者存在制约关系。在RFID应用中, 21 Q值应兼顾二者。

前面定义的Q是无载品质因数,其体现的是谐振电路自身的特 性 ,谐振电路总是要与外负载耦合,会使总的品质因数下降。 假设外负载为 RL ,外部品质因数定义为: Qe

射频识别(RFID)要解决不同物体之间的无线

通信问题,就要用到本章所学的知识——谐振电路。

1

谐振电路有很多种应用,可以在滤波器、振荡

9种晶体振荡器电路汇总

9种晶体振荡器电路汇总一、70MHz并联晶体振荡器电路:图1. 70MHz并联晶体振荡器电路三极管TV2进行信号放大,经电容C8耦合输出。

其中,电阻RI、R2和电阻R5、R6、R7是三极管VT1和VT2的直流偏置元件。

L2是高频扼流线圈,给振荡管VT1的集电极电流提供一个直流通路。

C2为隔直电容。

C3、C7是交流旁路电容,使VT1的发射极处于交流零电位,但直流电位不为零。

电感L1,电容C6,电阻R3为改善电源滤波电路,其作用是减少纹波电压以振高直流分量。

略调电容C4、C8,可以改变耦合信号的大小。

1.元器件选择电容C1为20p,C2为100p,C3、C7为820p,C4为56p,C5、C8为47p, C6为47u/50V。

电感L1为22uH(色码电感),L2为0.3uH。

电阻R1为1.6kΩ,R2为1kΩ,R3为750Ω,R4为180Ω、1W,R5为1.3kΩ,R6为3kΩ,R7为360Ω,R8为470Ω,R9—R12为300Ω、2W。

三极管VT1、VT2选3DG82B,65≤β≤115。

晶体SJT用JA9B型-70MHz。

继电器KM为JUC-1M。

2.使用时应注意(1) 在应用石英晶体时,有一个必须注意的实际问题,这就是晶体本身的激励功率。

激励功率较大时,输出功率也大,这时,晶体三极管引入的噪声影响不大。

但是,晶体激励功率过大会使晶体长期稳定性(老化特性)变坏。

晶体激励功率小时,长期稳定性较好,但是使用低噪电子元件技术网是第一个针对电子元器件应用、选型和实用设计方案的技术网络媒体。

声晶体三极管较佳。

(2) 由于晶体频率受温度影响很大,为保证对晶体频率稳定度的要求,必须注意晶体恒温。

即将晶体放在恒温槽内,由恒温控制电路来保证恒温槽内的温度使其维持在晶体的拐点温度。

因此,为使振荡频率和震荡幅度稳定,将晶体SJT和VT1、VT2放入恒温箱内。

恒温箱是用R9-R12四只2W金属膜电阻加热,一只小型密封温度继电器KM作温度控制元件。

晶振旁的电阻(并联与串联)

晶体的Q值非常高, Q值是什么意思呢? 晶体的串联等效阻抗是 Ze = Re + jXe, Re<< |jXe|, 晶体一般等效于一个Q很高很高的电感,相当于电感的导线电阻很小很小。Q一般达到10^-4量级。

避免信号太强打坏晶体的。电阻一般比较大,一般是几百K。

串进去的电阻是用来限制振荡幅度的,并进去的两颗电容根据LZ的晶振为几十MHZ一般是在20~30P左右,主要用与微调频率和波形,并影响幅度,并进去的电阻就要看 IC spec了,有的是用来反馈的,有的是为过EMI的对策

Xin和Xout的内部一般是一个施密特反相器,反相器是不能驱动晶体震荡的.因此,在反相器的两端并联一个电阻,由电阻完成将输出的信号反向 180度反馈到输入端形成负反馈,构成负反馈放大电路.晶体并在电阻上,电阻与晶体的等效阻抗是并联关系,自己想一下是电阻大还是电阻小对晶体的阻抗影响小大?

电阻的作用是将电路内部的反向器加一个反馈回路,形成放大器,当晶体并在其中会使反馈回路的交流等效按照晶体频率谐振,由于晶体的Q值非常高,因此电阻在很大的范围变化都不会影响输出频率。过去,曾经试验此电路的稳定性时,试过从100K~20M都可以正常启振,但会影响脉宽比的。

问: 我发现在使用晶振时会和它并一个电阻,一般1M以上,我把它去掉,板子仍可正常工作,请问这个电阻有什么用?可以不用吗? 我有看到过不用的!不理解~

答: 这个电阻是反馈电阻,是为了保证反相器输入端的工作点电压在VDD/2,这样在振荡信号反馈在输入端时,能保证反相器工作在适当的工作区。虽然你去掉该电 阻时,振荡电路仍工作了。但是如果从示波器看振荡波形就会不一致了,而且可能会造成振荡电路因工作点不合适而

可是转化为 并联等效阻抗后,Re越小,Rp就越大,这是有现成的公式的。晶体的等效Rp很大很大。外面并的电阻是并到这个Rp上的,于是,降低了Rp值 -----> 增大了Re -----> 降低了Q

谐振器

晶体谐振器与振荡器晶体谐振器在RLC振荡电路中的主要作用就是滤波,晶振一般采用如图1a的电容三端式(考毕兹) 交流等效振荡电路;实际的晶振交流等效电路如图1b,其中Cv是用来调节振荡频率,一般用变容二极管加上不同的反偏电压来实现,这也是压控作用的机理;把晶体的等效电路代替晶体后如图1c。

其中Co,C1,L1,RR是晶体的等效电路。

分析整个振荡槽路可知,利用Cv来改变频率是有限的:决定振荡频率的整个槽路电容C=Cbe,Cce,Cv三个电容串联后和Co并联再和C1串联。

可以看出:C1越小,Co越大,Cv变化时对整个槽路电容的作用就越小。

因而能“压控”的频率范围也越小。

实际上,由于C1很小(1E-15量级),Co不能忽略(1E-12量级,几PF)。

所以,Cv变大时,降低槽路频率的作用越来越小,Cv变小时,升高槽路频率的作用却越来越大。

这一方面引起压控特性的非线性,压控范围越大,非线性就越厉害;另一方面,分给振荡的反馈电压(Cbe上的电压)却越来越小,最后导致停振。

采用泛音次数越高的晶振,其等效电容C1就越小;因此频率的变化范围也就越小。

晶振的指标总频差:在规定的时间内,由于规定的工作和非工作参数全部组合而引起的晶体振荡器频率与给定标称频率的最大偏差。

说明:总频差包括频率温度稳定度、频率老化率造成的偏差、频率电压特性和频率负载特性等共同造成的最大频差。

一般只在对短期频率稳定度关心,而对其他频率稳定度指标不严格要求的场合采用。

例如:精密制导雷达。

频率稳定度:任何晶振,频率不稳定是绝对的,程度不同而已。

一个晶振的输出频率随时间变化的曲线如图2。

图中表现出频率不稳定的三种因素:老化、飘移和短稳。

图2 晶振输出频率随时间变化的示意图曲线1是用0.1秒测量一次的情况,表现了晶振的短稳;曲线3是用100秒测量一次的情况,表现了晶振的漂移;曲线4 是用1天一次测量的情况。

表现了晶振的老化。

频率温度稳定度:在标称电源和负载下,工作在规定温度范围内的不带隐含基准温度或带隐含基准温度的最大允许频偏。

并联谐振和串联谐振

并联谐振和串联谐振一、概述谐振电路是一种能够在特定频率下实现高效能量传输的电路。

谐振电路分为并联谐振和串联谐振两类,它们的共同点是在特定频率下具有较大的阻抗,从而实现了高效能量传输。

本文将详细介绍并联谐振和串联谐振的原理、特点、应用等方面。

二、并联谐振1. 原理并联谐振电路由一个电感L和一个电容C组成,如图1所示。

当交流信号通过该电路时,如果信号频率与电感和电容的共振频率相同,则会在该频率下形成高阻抗状态,从而实现了高效能量传输。

2. 特点(1)具有较大的输入阻抗,在输入端不会对信号源造成负载影响;(2)输出端阻抗小,适合驱动低阻抗负载;(3)对于变化较小的负载变化具有一定的稳定性。

3. 应用(1)用于滤波器设计中,可以实现对某一特定频率进行滤波;(2)用于无线通信系统中,可以实现对信号进行选择性放大;(3)用于音频放大器中,可以实现对特定频率的信号进行放大。

三、串联谐振1. 原理串联谐振电路由一个电感L和一个电容C组成,如图2所示。

当交流信号通过该电路时,如果信号频率与电感和电容的共振频率相同,则会在该频率下形成低阻抗状态,从而实现了高效能量传输。

2. 特点(1)具有较小的输入阻抗,在输入端会对信号源造成一定的负载影响;(2)输出端阻抗大,适合驱动高阻抗负载;(3)对于变化较小的输入信号变化具有一定的稳定性。

3. 应用(1)用于无线通信系统中,可以实现对信号进行选择性滤波;(2)用于音频放大器中,可以实现对特定频率的信号进行放大;(3)用于LC振荡器中,可以实现产生稳定的正弦波输出。

四、总结并联谐振和串联谐振是两种常见的谐振电路,在特定应用场景下具有各自独特的优势。

并联谐振适合驱动低阻抗负载,具有较大的输入阻抗和对负载变化的稳定性;串联谐振适合驱动高阻抗负载,具有较小的输入阻抗和对输入信号变化的稳定性。

在实际应用中,需要根据具体情况选择合适的谐振电路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

晶体的串联和并联谐振图解

石英晶体的外壳上标有器件的额定工作频率,但那只是一个近似值,实际上晶体有多个谐振频率,即使在理想情况下也是如此。

图1显示了理想晶体的等效电路,其中只有三个电路元件,串联的电容C1和电感L1、与该L1 C1串联对并联的另一个电容C2。

图1:理想石英晶体的等效电路

在特定的串联谐振频率,输入阻抗Z为零,L1和C1处于串联谐振。

电容C2与此无关。

然而,在特定的并联谐振频率,输入阻抗Z达到无穷大。

这是C2与L1 C1的串联组合发生并联谐振的频率,呈现电感性阻抗。

要使L1 C1对在并联谐振时呈现感性,并联谐振必须发生在比串联谐振更高的频率。

因此,并联谐振频率只能比串联谐振频率高,即使只高一点点。

并联谐振频率绝不会低于串联谐振频率。

至于哪个谐振对你更重要,则取决于应用。

借助不复杂的数学运算,阻抗Z可以表示如下:

图2:阻抗公式

串联谐振频率:Fseries = 1/(2 * pi * sqrt(L1 C1))

并联谐振频率:Fparallel = 1/(2 * pi * sqrt(L1 C1 C2 /(C1 + C2)))

图3:串联和并联谐振的相对位置。