第4章_复位时钟同步和初始化_mpc83xx中文手册

STM32F40x 41x微控制器时钟配置工具说明书

2011 年 10 月文档 ID 022298 第 1 版1/21AN3988应用笔记适用于 STM32F40x/41x 微控制器的时钟配置工具简介本应用笔记介绍了适用于 STM32F4xx 微控制器系列的时钟系统配置工具。

此工具的目的是帮助用户配置微控制器时钟,并将电源和 Flash 访问模式等参数考虑在内。

此配置工具在“STM32F4xx_Clock_Configuration_VX.Y .Z.xls ”文件中实现,该文件随 STM32F4xx 标准外设库提供,并可以从 下载。

此工具支持 STM32F4xx 的下列功能:●配置系统时钟、HCLK 源和输出频率。

●配置 Flash 延迟(等待周期数取决于 HCLK 频率)。

●设置 PCLK1、PCLK2、TIMCLK (定时器时钟)、USBCLK 和 I2SCLK 频率。

●生成含有上述全部设置的可直接使用的 system_stm32f4xx.c 文件(STM32F4xx CMSIS Cortex-M4 器件外设访问层系统源文件)。

在本文档中,STM32F4xx_Clock_Configuration_VX.Y .Z.xls 称为“时钟工具”。

在使用时钟工具之前,必须阅读 STM32F4xx 微控制器参考手册 (RM0090)。

本应用笔记不是参考手册的替代。

此工具仅支持 A 版 STM32F4xx 。

注:对于 VX.Y .Z ,请参见工具版本,例如 V1.0.0目录AN3988目录1词汇表 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52使用入门 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62.1软件要求 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62.2硬件要求 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72.2.1简介 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72.2.2STM32F4xx 微控制器的时钟方案 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72.2.3I2S 时钟发生器 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93教程 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113.1向导模式 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113.1.1分步过程 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113.2专家模式 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 4已知限制 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 5结论 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 6版本历史 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202/21文档 ID 022298 第 1 版AN3988表格索引表格索引表 1.术语定义. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5表 2.等待周期数与 CPU 时钟 (HCLK) 频率对应关系 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9表 3.文档版本历史 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20文档 ID 022298 第 1 版3/21图片索引AN3988图片索引图 1.时钟方案. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8图 2.I2S 时钟发生器架构 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9图 3.向导模式用户界面. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11图 4.HSE 值超出范围. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12图 5.VDD 超出范围. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12图 6.HCLK 错误消息. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13图 7.选择时钟源 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13图 8.无可用配置错误. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14图 9.文件生成错误 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14图 10.专家模式用户界面. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15图 11.超出系统时钟频率. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16图 12.超出 PLL 输入频率 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16图 13.I2S 频率超出范围 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 4/21文档 ID 022298 第 1 版AN3988词汇表1 词汇表表 1.术语定义术语说明HCLK AHB 时钟PCLK1APB1 时钟PCLK2APB2 时钟TIMCLK定时器时钟USB OTG FS USB 全速 OTGF CPU Cortex-M4 时钟Ext.Clock外部时钟V DD电源HSI高速内部时钟HSE高速外部时钟MCLK主时钟I2S内部集成音频Fs采样频率I2SCLK I2S 时钟RNG随机数发生器SDIO安全数字输入/输出接口文档 ID 022298 第 1 版5/21使用入门AN3988 2 使用入门本节介绍开始使用时钟工具所需的系统要求和步骤。

第3章_信号描述_mpc83xx中文手册

- - - - - - - - - 13-3/13-6 - - 13-3/13-6 13-3/13-6 - 21-1/21-2 13-3/13-6 13-3/13-6 13-3/13-6 21-1/21-2 21-1/21-2 21-1/21-2 21-1/21-2 21-1/21-2 13-3/13-6 13-3/13-6

在本文档中,所有的内部信号都用小写斜体字表示。例如,sys_logic_clk是一个内部信号。仅在需 要了解设备的外部功能时才参考这些信号。

3.1 信号概述 MPC8349E信号分为以下几组: � DDR存储器接口信号 � PCI接口信号 � DUART接口信号 � I2C接口信号 � 串行外围接口信号 � Ethernet管理接口信号 � TSEC1接口信号 � TSEC2接口信号 � 本地总线接口信号 � USB 2.0端口接口信号 � 全局定时器接口信号 � PIC接口信号 � JTAG、Test、PMC和系统控制信号 � 时钟信号

18-2/18-4 17-2/17-4 17-2/17-4 17-2/17-4 17-2/17-4 19-2/19-7 19-2/19-7 19-2/19-7 19-2/19-7 15-1/15-9 15-1/15-9 15-1/15-9 15-1/15-9 15-1/15-9 15-1/15-9 15-1/15-9 15-1/15-9 15-1/15-9 15-1/15-9 15-1/15-9 15-1/15-9 15-1/15-9 15-1/15-9 15-1/15-9 15-1/15-9 15-1/15-9 15-1/15-9 15-1/15-9 15-1/15-9 15-1/15-9 15-1/15-9 15-1/15-9 15-1/15-9

第6章_仲裁器和总线监控器_mpc83xx中文手册

第六章仲裁器和总线监控器本章介绍MPC8349E设备中的仲裁器的工作原理。

此外,还介绍仲裁器的配置、控制和状态寄存器。

6.1概述仲裁器负责提供一致性系统总线(coherent system bus)的仲裁。

它跟踪所有的地址和数据的总线占用,并为主设备和从设备提供仲裁信号。

此外,它还监控总线,报告错误和协议违反情况。

仲裁器具有以下特点:●支持可编程流水线深度(从1到4)●支持4层优先级的总线仲裁●支持重发请求模式:源自同一主设备的可编程连续事务的数量(最多8个事务)●支持数据流操作●支持可编程地址总线驻留(parking)模式:禁用、驻留在最后一个总线所有者、驻留在软件选择的主设备。

●仅要求地址、保留的和非法的事务类型,提出有关报告,且可以提出可屏蔽中断●提供地址占用超时定时器和数据占用超时检测定时器,任何一个定时器超时都可以发出可屏蔽中断●报告传输错误,可以发出可屏蔽中断●可以为每种错误事件发出常规或机器检查中断(可编程)6.1.1一致性系统总线概述一致性系统总线是MPC8349E的核心总线。

设备内从主设备到从设备的所有数据事务都经过该一致性系统总线。

MPC8349E一致性系统总线支持流水事务。

它拥有独立的地址和数据占用(tenure)。

流水深度决定在第一个数据占用完成之前可以开始的地址占用的数量。

基本突发长度等于核的高速缓存线(cache line)的长度,为32字节。

使用重复请求模式,一个主设备可以执行最多8个连续的突发。

连续事务的最大数量可以用可编程仲裁器配置寄存器限制。

详情请参见6.2.1节“仲裁器控制寄存器(ACR)”。

6.2仲裁器内存映射/寄存器定义表6-1展示了仲裁器的配置、控制和状态寄存器的内存映射。

复位值由复位字的核PLL配置确定。

需求参见第四章“复位、时钟定时和初始化”。

2寄存器AEATR和AEADR仅受/PORESET断言(assertion)的影响。

6.2.1仲裁器配置寄存器(ACR Arbiter Configuration Register)仲裁器配置寄存器(ACR)定义仲裁器模式和总线上的驻留(parked)主设备。

第15章_三速Ethnernet控制器_mpc83xx中文手册

图15-1

Ethernet协议与OSI协议栈的比较

� � �

千兆位Ethernet提供下列子层: 介质访问控制 (MAC) 子层——MAC子层在MAC与其对等站点之间提供一条逻辑连接, 其主要任务是初始化、控制和管理对等站点之间的连接。 调和子层——调和子层担当命令翻译器。它把MAC子层中使用的术语和命令映射成适 合于物理层实体的电气形式。 MII(介质独立接口)子层——MII子层MAC层和物理层之间的标准接口,支持10/100M

� �

�

� �

操作。它将MAC层和物理层分离,使得MAC层可以用于各种物理层实现。 GMII (千兆位介质独立接口) 子层——GMII子层提供MAC层和物理层之间的标准接口, 支持1Gbps操作。它将MAC层和物理层分离,使得MAC层可以用于各种物理层实现。 PCS(物理编码子层)——PCS负责对进入和离开MAC子层的数据流进行编码和解码。 介质(1000BASEX)8B/10B编码用于光纤,介质(1000BASET)8B/1Q编码用于无屏 蔽双绞线(UTP) 。 PMA(物理介质连接)子层——PMA负责将码组串行化为适合于位串行物理设备 (SerDes)的位流,或相反。为保证正确数据解码,该子层还要实现同步。PMA位于 PCS和PMD子层之间。 对于光纤介质 (1000BASEX) , PMA PMD端的接口是1位1250MHz 的信号,而在PMA PCS端的接口是125MHz的10位接口(TBI 10-bit interface) 。TBI是 GMII接口的一个备选方案。如果使用TBI,千兆位Ethernet控制器就必须能执行PCS功 能。对于UTP介质,PMA PMD端的接口由四对62.5MHz、PAM5编码的信号组成,PCS 端则向8B1Q4 PCS提供1250MHz的输入。 PMD(物理介质依赖)子层——PMD子层负责信号传输。典型的PMD功能包括放大、 调制和波形整形。不同的PMD设备支持不同的介质。 MDI(介质依赖接口)子层——MDI是一个连接器,它为不同的物理介质和PMD设备 定义不同的连接器。 图15-2描述了不同的物理层接口标准。

MPC8xx 系列处理器的嵌入式系统复位电路设计

M PC8xx 系列处理器的嵌入式系统复位电路设计■上海大学 林学龙 摘 要MPC8xx 系列微处理器是基于Power PC 体系结构的嵌入式处理器,基于此类处理器的嵌入式系统设计将会涉及到许多特殊问题,复位电路设计就是其中之一。

本文根据MPC8xx 系列处理器复位模块的结构与特性,介绍基于MPC8xx 系列处理器的嵌入式系统复位电路设计方法,并且给出实用电路。

关键词嵌入式处理器 PowerPC PowerQICC MPC8xx 复位电路Motorola 公司的Power PC 嵌入式处理器在全球通信处理器市场上处于无可争议的地位(占据70%以上的市场份额),这主要应当归功于PowerQUICC 系列的Power 2PC 嵌入式处理器芯片,即MPC8xx 系列处理器(包括MPC850、MPC855、MPC860、MPC823等)。

MPC8xx 系列嵌入式处理器复位模块的结构和特性与其他类型的嵌入式处理器有较大差异,与微控制器(MCU )和数字信号处理器(DSP )差别更大。

正确了解和理解其结构和特点,对于其外部的复位电路设计是非常重要的。

因此,首先介绍复位模块的功能框图和复位引脚,然后在此基础上说明复位电路的设计方法和实用电路。

1 MPC8xx 系列处理器复位模块MPC8xx 系列处理器复位模块,内置有复位控制器和硬件复位配置控制器。

复位控制器功能是确定复位原因、同步复位模块(若有必要的话),并且复位相应片内的逻辑模块(包括Power PC 嵌入式处理器模块、系统接口单元模块和通信处理器模块等),其内含有记录和决定复位原因的32位复位状态寄存器(RSR ,Reset Stat us Register )。

硬件复位配置控制器内含有配置处理器仲裁方式、中断表位置、引导存储器区地址位置和端口大小、测试和调试端口引脚和外部总线分频系数的硬件复位配置字(HRCW ,Hard Reset Configuration Word )。

第10章_局部总线控制器_mpc83xx中文手册_下册

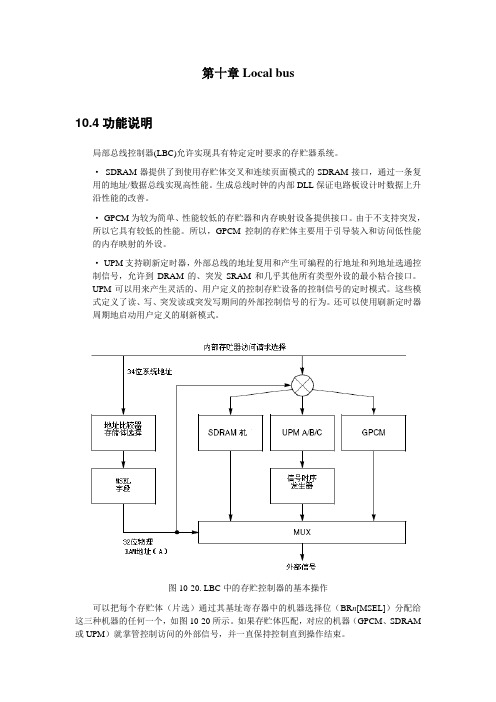

第十章Local bus10.4功能说明局部总线控制器(LBC)允许实现具有特定定时要求的存贮器系统。

·SDRAM器提供了到使用存贮体交叉和连续页面模式的SDRAM接口,通过一条复用的地址/数据总线实现高性能。

生成总线时钟的内部DLL保证电路板设计时数据上升沿性能的改善。

·GPCM为较为简单、性能较低的存贮器和内存映射设备提供接口。

由于不支持突发,所以它具有较低的性能。

所以,GPCM控制的存贮体主要用于引导装入和访问低性能的内存映射的外设。

·UPM支持刷新定时器,外部总线的地址复用和产生可编程的行地址和列地址选通控制信号,允许到DRAM的、突发SRAM和几乎其他所有类型外设的最小粘合接口。

UPM可以用来产生灵活的、用户定义的控制存贮设备的控制信号的定时模式。

这些模式定义了读、写、突发读或突发写期间的外部控制信号的行为。

还可以使用刷新定时器周期地启动用户定义的刷新模式。

图10-20. LBC中的存贮控制器的基本操作可以把每个存贮体(片选)通过其基址寄存器中的机器选择位(BR n[MSEL])分配给这三种机器的任何一个,如图10-20所示。

如果存贮体匹配,对应的机器(GPCM、SDRAM 或UPM)就掌管控制访问的外部信号,并一直保持控制直到操作结束。

10.4.1 基本系统结构下面几个小节介绍LBC的基本系统结构。

10.4.1.1 地址和地址空间检查将已定义的基址写入BR n寄存器,将对应的地址掩码写入OR n寄存器。

每当请求访问局部总线时,将内部事务的地址与每一个存贮体进行比较。

该地址由OR n[BA]和OR n[AM]屏蔽,通过将该地址的19个最高有效位与每个存贮体的基址进行比较来译码地址。

如果与一个存贮控制器存贮体匹配,那么就使用由该存贮体的BR n和OR n所定义的属性控制存贮器的访问;如果与多个存贮体匹配,那么编号最小的存贮体处理存贮器访问(也就是说,存贮体0的优先级高于存贮体1)。

第18章_DUART_mpc83xx中文手册

18章 DUART本章介绍MPC8394E的两个通用异步接收器/发送器(UART universal asynchronous receiver/transmitter)。

介绍其功能操作、DUART的初始化步骤、以及DUART寄存器的编程细节和特性。

18.1 概述DUART包括两个通用异步接收器/发送器(UART)。

这两个UART 独立工作。

本章所有UART相关的讨论都是针对其中一个接收器/发送器而言的。

各UART通过系统时钟进行时钟同步。

DUART编程模型和PC16552D兼容。

UART为点对点接口,即只能够把两个UART设备连到连接信号上。

如图18-1所示,每个UART模块的组成如下:接收和发送缓冲区用于数据流控制的清除发送输入端口()和请求发送输出端口用于产生波特率的16位计数器中断控制逻辑图18-1 UART结构图18.1.1 特性DUART包括以下特性:全双工操作。

可编程模式,兼容原来的PC16450UART和PC16550D(能工作在FIFO模式下的PC16450改进版本)。

PC16450寄存器复位值。

用于发送器和接收器的FIFO模式,提供16字节的FIFO。

采用标准的异步通信位(START、STOP和奇偶校验)封装和解封串行数据。

可屏蔽发送、接收、线路状态和MODEM状态中断。

软件可编程的波特率发生器,将系统时钟用1到(216-1)分频,为发送器和接收器引擎生成16倍时钟。

清除发送和发送就绪MODEM控制功能。

软件可选择的串行数据格式(数据长度、奇偶校验、1/1.5/2停止位、波特率)。

线路和MODEM状态寄存器。

线路断开(Line-break)检测和产生。

内部诊断支持、本地环路和断开功能。

具有优先级的中断报告。

过载、奇偶校验和帧错误检测。

18.1.2 操作模式信道提供一个全双工的异步发送器和接收器,使用源自系统时钟的操作频率。

发送器接收写入发送器保持寄存器(UTHR)的并行数据。

第19章_串行外围设备接口(SPI)_mpc83xx中文手册

SPISEL 有效则导致错误。

� 当 SPI 为从设备时, SPICLK 是时钟输入信号, 它从 SPIMOSI 移入接收到的数据, 将发送的数据通过 SPIMISO 移出。 SPISEL 是到 SPI 从设备的使能输入信号。 在 多主设备环境下, SPISEL (始终作为输入)还用来检测有多个主设备操作这样 的错误。 内存映射/寄存器定义 表 19-3 包含 SPI 的映射到内存空间的寄存器。 表中所列的地址为到 SPI 基址的偏移量, 同第二章“内存映射”中定义的那样。 表 19-3 SPI 寄存器汇总 19.4 偏移量 0x000-0x01F 0x020 0x024 寄存器 保留 SPI 模式寄存器 (SPMODE) SPI 事件寄存器 访问 - R/W R/W 复位值 - 0x0000_0000 0x0000_0000 节/页 - 19.4.1.1/19-9 19.4.1.2/19-13

19.3

外部信号说明 SPI 的四线接口包括发送、接收、时钟和从选择。

19.3.1 概述 表 19-1 列出了信号的属性。 表 19-1 名字 SPIMISO SPIMOSI SPICLK 功能 主设备入从设备出 主设备出从设备入 连接到其他 SPICLK 的输入 / 输出串行时 钟 SPI 从设备选择 信号属性 复位 - - - - 上拉 在漏极开路模式下需要 在漏极开路模式下需要 在漏极开路模式下需要 在漏极开路模式下需要

注意: 1.所有信号都是漏极开路的。 2.对于两个以上主设备的多主设备配置, SPISEL 和SPIE[MME]不能检测到所有可能的冲 突。 3.由软件负责SPI总线的仲裁(例如使用如令牌传递)。 4. SELOUTx 信号用软件使用通用I/O信号实现。 图19-3 多主设备配置

第4章 复位、时钟同步和初始化

第四章复位、时钟同步和初始化本章介绍复位、时钟同步和MPC8349E设备的整体初始化,包括复位配置信号的定义及其选项。

此外还介绍配置、控制和状态寄存器。

注意,本书的每一章都介绍了一个部件额外的具体的初始化过程。

4.1概述复位、时钟同步和控制信号为设备的操作提供很多选项。

可以在硬复位或上电复位期间配置不同的模式和特性。

大多数可配置特性由复位配置字装入设备,只有很少一部分信号用作复位序列期间的复位配置输入。

4.2外部信号说明下面几节详细说明复位和时钟信号。

4.2.1复位信号表4-1说明了MPC8349E的复位信号。

4.4.2节“复位配置字”介绍了还作为复位配置信号的信号。

表4-1 系统控制信号——详细信号说明4.2.2时钟信号表4-2说明了MPC8349E的外部时钟信号。

注意,某些信号对设备内的某些部件来说是特定的,虽然4.5节“时钟同步”介绍了它们的某些功能,但分别在各章中对它们进行了详细定义。

表4-2 时钟信号——详细信号说明4.3功能说明本节介绍复位设备的各种方法、上电复位配置和设备的时钟同步。

4.3.1复位操作设备有数个到复位逻辑的输入:●上电复位(/PORESET)●外部硬复位(/HRESET)●外部软复位(/SRESET)●软件看门狗复位●系统总线监控器复位●检查停止(checkstop)复位●JTAG复位●软件硬复位所有这些复位源都被馈送到复位控制器,并根据复位源的不同采取不同的行动。

4.6.1.3节“复位状态寄存器(RSR)”中介绍的复位状态寄存器指示引起复位的最后的复位源。

4.3.1.1复位原因表4-3介绍了复位原因。

表4-3 复位原因4.3.1.2复位操作复位控制逻辑确定复位的原因,必要时对其进行同步,并复位适当的内部硬件。

每个复位流对设备有不同的影响:∙上电复位的影响最大,它复位整个设备,包括时钟逻辑和错误捕获寄存器。

∙硬复位复位整个设备,但不包括时钟逻辑和错误捕获寄存器。

∙软复位则初始化内部逻辑,但保持系统的配置。

第2章_内存映射_mpc83xx中文手册

寄存器

系统配置寄存器

0x0_0000

IMMRBAR-内部内存映射基址寄存器

0x0_0004 保留,应被清零

0x0_0008

ALTCBAR-备用配置基址寄存器

0x0_000C– 保留,应被清零

0x0_001C

0x0_0020

LBLAWBAR0-LBC 本地访窗口 0 基址寄存器

0x0_0024

LBLAWAR0-LBC本地访问窗口0属性寄存器

-

5.3.2.8/5-30 5.3.2.9/5-32

-

-

5.4.4.1/5-35 5.4.4.2/5-36

-

5.4.4.3/5-37

5.5.5.1/5-43 5.5.5.2/5-44 5.5.5.3/5-44 5.5.5.4/5-45 5.5.5.5/5-46 5.5.5.6/5-47

-

5.6.5.1/5-52 5.6.5.2/5-53

R/W

0x0_012C DDR调试状态寄存器(DDRDSR)

R

0x0_0130– 保留

-

0x0_01FC

看门狗定时器(WDT)寄存器

0x0_0200– 保留,应被清零

-

0x0_0203

0x0_0204

SWCRR-系统看门狗控制寄存器

R/W

0x0_0208

SWCNR-系统看门狗计数寄存器

R

0x0_020C– 保留,应被清零

0x0_0408 0x0_040C 0x0_0410 0x0_0410– 0x0_041F

0x0_0500 0x0_0501– 0x0_0503 0x0_0504 0x0_0505– 0x0_050F 0x0_0510 0x0_0512 0x0_0514 0x0_0516 0x0_0518 0x0_051A 0x0_051C 0x0_051E 0x0_0520 0x0_0522 0x0_0524 0x0_0526 0x0_0528 0x0_052A 0x0_052C 0x0_052E 0x0_0530 0x0_0532 0x0_0534 0x0_0536 0x0_0538 0x0_053A 0x0_053C 0x0_053E

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第四章复位、时钟同步和初始化本章介绍复位、时钟同步和MPC8349E设备的整体初始化,包括复位配置信号的定义及其选项。

此外还介绍配置、控制和状态寄存器。

注意,本书的每一章都介绍了一个部件额外的具体的初始化过程。

4.1概述复位、时钟同步和控制信号为设备的操作提供很多选项。

可以在硬复位或上电复位期间配置不同的模式和特性。

大多数可配置特性由复位配置字装入设备,只有很少一部分信号用作复位序列期间的复位配置输入。

4.2外部信号说明下面几节详细说明复位和时钟信号。

4.2.1复位信号表4-1说明了MPC8349E的复位信号。

4.4.2节“复位配置字”介绍了还作为复位配置信号的信号。

表4-1 系统控制信号——详细信号说明4.2.2时钟信号表4-2说明了MPC8349E的外部时钟信号。

注意,某些信号对设备内的某些部件来说是特定的,虽然4.5节“时钟同步”介绍了它们的某些功能,但分别在各章中对它们进行了详细定义。

表4-2 时钟信号——详细信号说明4.3功能说明本节介绍复位设备的各种方法、上电复位配置和设备的时钟同步。

4.3.1复位操作设备有数个到复位逻辑的输入:●上电复位(/PORESET)●外部硬复位(/HRESET)●外部软复位(/SRESET)●软件看门狗复位●系统总线监控器复位●检查停止(checkstop)复位●JTAG复位●软件硬复位所有这些复位源都被馈送到复位控制器,并根据复位源的不同采取不同的行动。

4.6.1.3节“复位状态寄存器(RSR)”中介绍的复位状态寄存器指示引起复位的最后的复位源。

4.3.1.1复位原因表4-3介绍了复位原因。

表4-3 复位原因4.3.1.2复位操作复位控制逻辑确定复位的原因,必要时对其进行同步,并复位适当的内部硬件。

每个复位流对设备有不同的影响:∙上电复位的影响最大,它复位整个设备,包括时钟逻辑和错误捕获寄存器。

∙硬复位复位整个设备,但不包括时钟逻辑和错误捕获寄存器。

∙软复位则初始化内部逻辑,但保持系统的配置。

所有复位类型都产生到e300c1核的复位。

/PORESET、/HRESET和/SRESET对给定应用的影响是核将MSR[IP]的值复位为复位寄存器字高端的BMS字段中的值。

参见4.4.2.12节“引导内存空间(BMS)”。

存贮器控制器、系统保护逻辑、中断控制器和I/O信号仅在硬复位时初始化。

软复位初始化内部逻辑,但保持系统的配置。

外部/SRESET有效向核和其余的设备产生硬复位。

表4-4标识了每个复位源的复位操作。

4.3.2上电复位流/PORESET外部信号有效启动上电复位流。

在设备的外部供电稳定之后,应保持/PORESET外部有效至少32个输入时钟周期。

在/PORESET无效之后,设备立即开始配置过程。

设备在整个上电复位过程期间,包括配置期间,宣告/HRESET和/SRESET有效。

配置时间根据配置源和CLKIN(PCI 主机模式)或PCI_CLK(PCI代理模式)频率的不同而变化。

首先对复位配置输入进行采样,确定配置源和输入时钟的分配模式。

然后设备开始装入复位配置字。

系统PLL根据复位配置字低端中的时钟模式值开始锁定。

当系统PLL锁时序,时钟单元开始在设备中分配时钟信号。

在这个阶段,e300c1核的PLL开始锁定。

当它被锁定并完成了复位配置字的装入时,释放/HRESET,在4个时钟之后释放/SRESET。

4.3.2.1详细上电复位流程MPC8349E的详细上电复位(POR)流程如下:1.加电,满足MPC8349E硬件规范的要求。

2.系统宣告/PORESET(以及可选的/HRESET)和/TRST有效,让所有寄存器初始化到它们的缺省状态,让大部分I/O驱动器释放为高阻(某些时钟、时钟允许和系统控制信号仍保持有效)状态。

3.系统施加稳定的CLKIN(PCI主机模式)或PCI_CLK(PCI代理模式)信号和稳定的复位配置输入信号(CFG_RESET_SOURCE和CFG_CLKIN_DIV)。

4.在至少32个稳定的CLKIN(PCI主机模式)或PCI_CLK(PCI代理模式)时钟周期之后,系统将/PORESET置为无效。

5.设备对复位配置输入信号进行采样,确时时钟分配和复位配置源。

6.设备开始装入复位配置字。

装入时间与复位配置字源有关。

7.一旦装入了复位配置字低端,系统PLL就开始锁定。

当系统PLL锁时序,向e300c1 PLL提供csb_clk。

8.e300c1 PLL开始锁定。

9.设备一直驱动/HRESET有效,直到e300c1 PLL锁定且装入了复位配置字为止。

10.如果前面未将/HRESET置为无效,此时用户可以选择将/HRESET置为无效。

注意JTAG逻辑必须总是能通过设置/TRST有效来初始化。

如果未使用JTAG信号,应将/TRST与/PORESET直接连接。

在/PORESET 无效之后,/TRST一定不能继续有效。

在/HRESET有效时,不需要让/SRESET有效。

11.将到核和其余逻辑的内部复位置为无效。

启用I/O驱动器。

LBC DLL开始锁定。

为响应配置周期,PCI接口可以宣告/DEVSEL有效。

12.设备停止驱动/SRESET,/SRESET变为无效。

将到e300核的复位置为无效,并启用核。

如果允许,释放引导定序器,让它从串行ROM装入配置数据,参见17.4.5节“引导定序器模式”。

13.在引导定序器完成操作之前,如果需要,可以清除PCI总线功能寄存器中的CFG_LOCK位以允许PCI接口接受外部请求。

PCI总线功能寄存器见表13-41。

如果e300核要求继续进行,引导定序器应清除ACR[COREDIS],允许取引导向量。

有关说明见6.2.1节“仲裁器配置寄存器(ACR)”。

14.如果允许,PCI接口现在可以接受外部请求。

如果允许,核可以取引导向量。

现在设备就处于就绪状态了。

图4-1给出了上电复位流的时序图图4-1 上电复位流4.3.3硬复位流/HRESET信号由外部通过设置/HRESET有效来启动,或在设备检测到某种情况时由内部产生内部硬复位序列来启动。

在上述两种情况中,设备在整个/HRESET状态期间继续宣告/HRESET和/SRESET有效。

硬复位序列的时间根据配置源和CLKIN(PCI主机模式)或PCI_CLK(PCI代理模式)频率的不同而变化。

硬复位不对复位配置输入信号(CFG_RESET_SOURCE和CFG_CLKIN_DIV)进行采样,所以设备立即开始装入复位配置字,并按4.4.3节“装入复位配置字”解释的那样配置设备。

在配置序列完成之后,设备释放/HRESET和/SRESET信号,并退出/HRESET状态。

一个外部上拉电阻应让信号无效。

在检测到信号无效之后,需要经过16个周期的时间才能开始测试外部(硬/软)复位是否存在。

注意因为设备在硬复位流期间不对复位配置输入信号(CFG_RESET_SOURCE和CFG_CLKIN_DIV)进行采样,所有对那些信号设置新值(不是上电复位期间设置的值)没有用。

图4-2给出了硬复位流的时序图。

图4-2 硬复位流4.3.4软复位流/SRESET信号可以由外部通过使/SRESET有效来启动,或在设备检测到某种情况时由内部宣告/SRESET有效来启动。

在上述两种情况中,设备宣告/SRESET有效512个PCI_CLK/PCI_SYNC_IN/SYNC_IN个时钟周期,然后设备释放/SRESET,并退出/SRESET信号。

一个外部上拉电阻应让/SRESET无效。

在检测到此信号无效之后,需要经过16个周期的时间才能开始测试外部(硬/软)复位是否存在。

当/SRESET有效时,复位内部硬件,但硬复位配置不会改变。

4.4复位配置用两种互补的方法初始化设备:锁存CFG_RESET_SOURCE和装入复位配置字。

开始时,在/PORESET置为有效期间对一小部分输入信号进行采样。

这些信号确定是否需要复位配置字,以及从哪个设备源接口装入。

根据这些信号的值,设备可以继续装入复位配置字。

4.4.1复位配置信号复位配置输入信号位于这样一些设备引脚上,在设备未处于复位状态时,这些引脚具有其他功能。

在/PORESET有效期间,提供的时钟稳定之后(/PORESET),对这些输入信号进行采样并放入寄存器,一旦/HRESET有效,这些输入信号就必须立即由外部电阻拉高或拉低。

在/PORESET和/HRESET信号期间,连接到这些信号的所有其他信号的驱动器必须处于高阻状态。

关于用于拉高或拉低复位配置信号的合适的电阻值参考MPC8349E硬件规范。

本节介绍由复位配置信号配置的模式。

注意,软件通过在4.6.1.3节“复位状态寄存器(RSR)”和4.6.2.1节“系统PLL模式寄存器(SPMR)”介绍的内存映射寄存器可以访问复位配置输入信号的采样值。

注意建议用户实现下列方法中的一种,来控制对这些引脚的复位和非复位功能的选择。

●电阻。

使用上拉或下拉电阻在复位配置输入信号上设置所期望的值。

在上电和硬复位序列期间,这些信号是到设备的输入信号。

●主动驱动设备。

使用/HRESET控制驱动设备。

当/HRESET有效时,驱动引脚的复位配置值;当/HRESET无效时,停止驱动复位配置输入信号。

4.4.1.1复位配置字源复位配置字源选项如表4-5所示,它选择是从本地总线EEPROM、还是从I2C EEPROM(I2C #1)装入复位配置字,或者使用硬编码的缺省选项。

注意这些信号的值还影响上电和硬复位序列的持续时间。

无论如何,复位序列不能超过1ms。

4.4.1.2CLKIN分配当把设备配置为PCI主机设备时,CFG_CLKIN_DIV配置输入选择CLKIN和PCI_SYNC_OUT/SYNC_OUT之间的关系,如表4-6所示。

当配置为PCI主机设备时,该设备支持八路PCI_CLK输出信号。

每个输出时钟的频率都可以在OCCR寄存器中设定,让它等于CLKIN频率或为CLKIN频率的一半。

如果至少有一个频率为CLKIN频率一半的输出PCI时钟,则应将CFG_CLKIN_DIV复位配置信号拉高,否则拉低。

当把设备配置为PCI代理设备时,如果在上电复位有效期间采样值为“1”,则可以使用CFG_CLKIN_DIV配置输入将内部时钟频率加倍。

如果期望不论PCI时钟是按33还是按66MHz运行,内部频率都固定,则该特性很有用。

PCI规范要求,由M66EN信号提供PCI时钟频率的信息。

4.4.1.3选择复位配置输入信号表4-7给出了一个例子,说明用户应如何拉低或拉高复位配置输入信号(CFG_RESET_SOURCE 和CFG_CLKIN_DIV)。

复位序列持续的时间从/PORESET无效时开始到/SRESET无效时结束。

4.4.2复位配置字复位配置字控制时钟的比率和其他基本设备功能,例如PCI主机或代理模式、引导定位、TSEC 模式和字节序模式等。