数电第二章

数电讲义--2章

1.0

VOL(max)0.5

输入标 准低电

平

0.4V

VNL

D VNH

E

V V 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0

SL VOFF VON

SH

Vi (V)

输入标准

高电平

2. 输入特性

+VCC

1) 输入伏安特性

iI

R1 3kΩ

1

-1.6 mA

<50 uA vI A

31

B

T1

1.4 V

和边沿,T4放大。 VO随iOH变化不大。 当由i于Oi以OHH受↑:线时功性,R耗变4上的化压限。降制增,大i0,H过T大3 、会T4烧饱毁和T,4管V,O随所

功耗 1mW IOH 400 A

输出高电平时的扇出系数 3.6V

R2 750Ω 2T3 Vc2 1 3 R4

VO

+VCC

R 4 +5V 100Ω

抗干扰能力越强。 高电平噪声容限

VNH= VSH ¯ VON 。

VNH越大,输入为1态下

抗干扰能力越强。

Vo (V)

4.0 A B

3.5

3.0

VOH(min)2.5 2.4V

C

2.0

1.5

A(0V, 3. 6V) B(0.6V, 3.6V) C(1.3V, 2.48V) D(1.4V, 0.3V) E(3.6V, 0.3V)

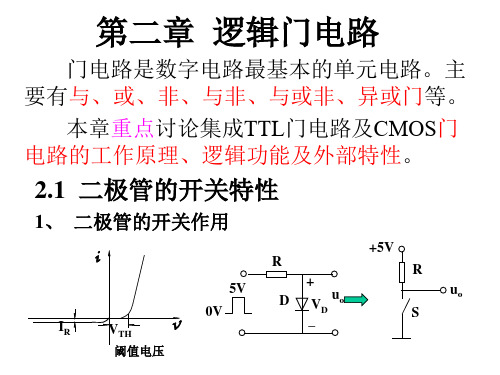

• 导通(VD>VTH) • 2、二极管的开关时间

截止5V(VDR<VT+H)

0V

D VD

uo

_

VF Vi

二极管开关状态的转换需要时间:

t1 t2

数字电路 第二章 逻辑代数基础.

⒊ 表达式 逻辑代数中“ 逻辑关系用“ 逻辑代数中“与”逻辑关系用“与”运 算描述。 运算又称逻辑乘, 算描述。“与”运算又称逻辑乘,其运算符 两变量的“ 运算可表示为: 为“⋅” ,两变量的“与”运算可表示为: F=A ⋅ B 简写为: 简写为:F=AB 读作: 等于 等于A与 读作:F等于 与B

⒊ 表达式 逻辑代数中“ 逻辑关系用“ 逻辑代数中“或”逻辑关系用“或”运算 描述。 运算又称逻辑加, 描述。“或”运算又称逻辑加,其运算符为 两变量的“ 运算可表示为: “+” 。两变量的“或”运算可表示为: F=A+B 读作: 读作:F 等于 A 或 B

三、“非”运算(逻辑非) 运算(逻辑非)

例:如 AB + AC + BC = AB + ( A + B )C = AB + ABC = AB + C 则 ( A + B) ⋅ ( A + C ) ⋅ ( B + C ) = ( A + B) ⋅ C

例: 证明包含律:(A+B)·(A+C)·(B+C)=(A+B)· (A+C) 证明包含律: 证: 已知 AB +A C+BC=AB+AC + + 等式两边求对偶: 等式两边求对偶:(A+B)·(A+C)·(B+C)=(A+B)· (A+C) 证毕

量进行描述,称布尔代数,统称逻辑代数。 量进行描述,称布尔代数,统称逻辑代数。 逻辑状态: 完全对立、截然相反的二种状态, ⒋ 逻辑状态: 完全对立、截然相反的二种状态,如:好坏、 好坏、 美丑、真假、有无、高低、开关等。 美丑、真假、有无、高低、开关等。 逻辑变量: ⒌ 逻辑变量: 代表逻辑状态的符号, 代表逻辑状态的符号,取值 0 和 1。不表示数 。 逻辑函数: 量的大小,而是表示两种对立的逻辑状态。 ⒍ 逻辑函数: 量的大小,而是表示两种对立的逻辑状态。 输出是输入条件的函数。 输出是输入条件的函数。

数字电子技术 第二章汇总

内容概述 第一节 标准TTL与非门 第二节 其它类型TTL门电路 第三节 ECL逻辑门电路 第四节 I2 L逻辑门电路 第五节 NMOS逻辑门电路 第六节 CMOS逻辑门电路 第七节 逻辑门的接口电路 小结

BJT : Bipolar Junction Transistor TTL : Transistor-Transistor Logic ECL : Emitter-Coupled Logic CMOS : Complementary Metal-Oxide-Semiconductor I2L : Integrated Injection Logic

A B

TTL与非门的外特性及主要参数 4. 关门电平U : OFF 和输出低电平 1. 输出高电平 U U

C

D

E

TTL与非门的外特性及主要参数 5. 噪声容限

TTL与非门的外特性及主要参数 外特性:指的是电路在外部表现出来的各种特性。 掌握器件的外特性及其主要参数是用户正确使用、维护 和设计电路的重要依据。 介绍手册中常见的特性曲线及其主要参数。

TTL与非门的外特性及主要参数

性区 区: . 6≤V ≤UI, ≤1.3V, 截线 止 :当 当0 U 0.6V I 0.7V ≤U时, T2导通,T5 (一)电压传输特性 b2<1.4V Ub1 ≤1.3V T2、时, T5 截止, 饱和区:UI继续升高, T1进入UC2随 仍截止, U 输出高电平 = 3.6V 。 b2 升高而下降, OH TTL 与非门输入电压 U 与输出电压 U 之间的关系曲线, I O 转折区:当 UI≥1.3V 倒置工作状态 U时, ,此时 经T 射随器使 UO下降。 b1=2.1V 4 即 U = f ( U )。 O T 、T I 输入电压略微升高,输出 2 5饱和,T4截止,输出低 电平UOL = 0.3V T ,且 电压急剧下降,因为 2、 UO不随UI 的增大而变化。 T4 、 T 5均处于放大状态。

数电——第2章放大电路基础学习要点

二、分压式偏置放大电路

(2) 动态分析 分压式偏置放大电路的微变 等效电路如图所示。 等效电路如图所示。 RS 电压放大倍数: 电压放大倍数: us + • RB1 RC

C1 + + C2

+VCC T RB2

+

+

RL

uo

-

Au =

Uo

•

=−

β ( RL // RC )

rbe

RE

CE

- (a) 放大电路

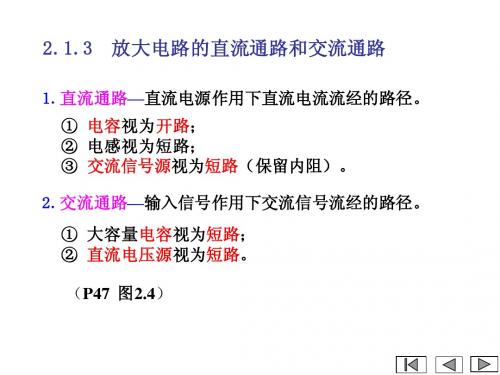

2.1.3 放大电路的直流通路和交流通路

1.直流通路 直流电源作用下直流电流流经的路径 1.直流通路—直流电源作用下直流电流流经的路径。 直流通路 直流电源作用下直流电流流经的路径。 电容视为开路; 视为开路 ① 电容视为开路; 电感视为短路; ② 电感视为短路; ③ 交流信号源视为短路(保留内阻)。 交流信号源视为短路(保留内阻)。 视为短路 2.交流通路 输入信号作用下交流信号流经的路径 2.交流通路—输入信号作用下交流信号流经的路径。 交流通路 输入信号作用下交流信号流经的路径。 大容量电容视为短路 电容视为短路; ① 大容量电容视为短路; 直流电压源视为短路。 视为短路 ② 直流电压源视为短路。 (P47 图2.4)

二、分压式偏置放大电路

分压式偏置放大电路, 自动调节 不随温度变化, 分压式偏置放大电路,能自动调节IC不随温度变化, 克服了固定偏置放大电路受温度影响的缺点。 克服了固定偏置放大电路受温度影响的缺点。 +V +VCC RB1 RC

C1 + + C2

CC

RB1

+

I1 RC IB I2

IC UCE

ri

注意射极电阻折算到基级: 注意射极电阻折算到基级 ×(1+β)

数字电子技术第2章

① 线与逻辑图

演 示 文 稿 Presentation

A B

&

L1 L=L1 L2

C D

&

L2

线与逻辑图 EXIT EXIT

第2章 逻辑门电路

②

UCC

母线传输

(BUS)

B1

× ×

演 示 文 稿 Presentation

RC

B1

& 1

& 2 E2 B1

& n En B2

选 通 信 号 E1 数字信号1

(5) UOH (min) :输出高电平的下限值,2.4 V。 输出高电平的下限值, 。 (6) UOL (max) :输出低电平的上限值,0.4 V。 输出低电平的上限值, 。 (7) IOH (max) :高电平输出电流(拉电流)的上限值,0.4 mA。 高电平输出电流(拉电流)的上限值, 。 (8) IOL (max) :低电平输出电流(灌电流)的上限值,-16 mA。 低电平输出电流(灌电流)的上限值, 。 (9) VCC :电源电压,( ±5%)V。 电源电压,( ,(5± ) 。 EXIT EXIT

× × √

VD3 Z VT5

0

EXIT EXIT

第2章 逻辑门电路

A

演 示 文 稿 Presentation

B 0 1 0 1

Z 1 1 1 0

0 0 1 1

Z = AB

EXIT EXIT

第2章 逻辑门电路

2.TTL与非门的电压传输特性 . 与非门的电压传输特性

TTL与非门的电压传输特性是指其输出电压 O 与非门的电压传输特性是指其输出电压u 与非门的电压传输特性是指其输出电压 与输入电压u 的关系特性。 与输入电压 I的关系特性。

精品课件-数字电子技术-第2章

第2章 集成逻辑门电路

图2-7 双极型三极管输入特性曲线

第2章 集成逻辑门电路

图2-8 双极型三极管输出特性曲线

第2章 集成逻辑门电路

3. 双极型晶体管的静态特性 在数字逻辑电路中,三极管作为开关元件,工作于饱和区 和截止区。图2-9是一个由双极性晶体管构成的典型的单管共 射放大电路,三极管V的门限电压为Uon,当输入电压ui小于门 限电压Uon时,发射结处于反向偏置,三极管工作于截止状态, iB≈0,iC≈0, uo=UCC。当输入电压ui大于某一数值时,发射 结和集电结均达到正向偏置,三极管工作于饱和状态,饱和导 通的条件为

第2章 集成逻辑门电路

图2-4 (a) 或门电路;(b) 逻辑符号

第2章 集成逻辑门电路

表2-2(a) 二极管或门电平

第2章 集成逻辑门电路

表2-2(b) 二极管或门真值表

第2章 集成逻辑门电路

从真值表分析可知:只要A、B当中有一个是高电平,Y即

为高电平,只有A、B同时为低电平,Y才为低电平, “或”

第2章 集成逻辑门电路

第2章 集成逻辑门电路

2.1 概述 2.2 分立元件逻辑门电路 2.3 TTL集成逻辑门 2.4 CMOS集成逻辑门

第2章 集成逻辑门电路

2.1 概 述

门电路(gate circuit)是构成数字电路的基本单元。所 谓“门”就是一种条件开关,在一定的条件下,它允许信号通 过,条件不满足时,信号无法通过,从而形成高电平和低电平 两种状态。在二值逻辑中,逻辑变量的取值不是1就是0,在 电子电路中用高、低电平分别表示1 和 0

图2-2 二极管伏安特性的近似方法与等效电路

第2章 集成逻辑门电路

2. 实现与逻辑关系的电路称为与门。最简单的与门可以由二 极管和电阻组成。图2-3(a)所示是有两个输入端的与门电路, 图2-3(b)所示为它的逻辑符号。图中A、B为两个信号输入端, Y为输出端。设UCC=5 V,A、B输入端的高低电平分别为UIH=3 V 和UIL=0 V,二极管VD1、VD2的正向导通压降为UD=0.7 V。输入 端A、B

数电第2章(门电路)课件

T1集电结正偏,

发射结反偏,倒 置工作状态

VIH A

3.4V

R1 4kW R2

1.6KW

2.1V

1V

+Vcc R4 130W 5V

数字电子技术(jìshù )基础 Fundamentals of Digital Electronic Technology

第二章 门电路

1

精品资料

第二章 门电路

2.1 概述

2.2 半导体二极管和三极管的开关特性

2.3 最简单(jiǎndān)的与、或、非门电路

2.4 TTL门电路

*2.5 其它类型的双极型数字集成电路

存储时间ts 下降时间tf 关闭时间1133toff

(1) 开启时间ton 三极管从截止(jiézhǐ)到饱和所需的时间。

ton = td +tr td :延迟时间 tr :上升时间

(2) 关闭时间toff 三极管从饱和到截止(jiézhǐ)所需的时间。

toff = ts +tf ts :存储时间(几个参数中最长的;饱和越深越长) tf :下降时间

4

精品资料

获得高、低电平的基本原理

Vcc

Vcc

R

Vo

只要(zhǐyào) 能判断高低电 平即可

1

Vi

K

可用二、三

极管代替

0V

0

K开------Vo=1, 输出(shūchū)高电平 K合------Vo=0, 输出(shūchū)低电平 对电路元件参数、电源的要求比模拟电路要低。

5

精品资料

2.2 半导体二极管和三极管的开关 (kāiguān)特性

rD≈几Ω ~几十Ω

应用(yìngyòng)于二

精品课件-数字电子技术-第2章

第2章 逻辑门电路

(2) 当输入A、B全为高电位时,即当VIH=3.6 V时,V1的 集电极、V2和V5发射极均导通,则V2和V5管处于饱和状态,故 VO=VOL=VCES5=0.3 V。另外,由于VC2=VB3= VCES2+VBE5=0.3+0.7=1 V,此电压不足以使V4导通,故V4处于截

(1) 高电平输出特性。当TTL与非门输出为高电平时,若 在门电路输出端接入负载,这时将有负载电流流出驱动门,好像 是负载从与非门拉走电流,此电流称为拉电流(或高电平输出电 流),如图2-25所示,记为IOH。一般IOH≤0.4 mA

(2) 低电平输出特性。当TTL与非门输出为低电平时,若 在门电路输出端接入负载,这时将有负载电流流入驱动门,好像 是负载向与非门灌入电流,此电流称为灌电流(或低电平输出电 流),如图2-26所示,记为IOL。一般IOL≤8 mA

(2) 低电平输入电流IIL。 IIL为与非门输入低电平时流 出输入端的电流,如图2-24所示,一般IIL≤0.4 mA

第2章 逻辑门电路

图2-23 TTL与非门高电平输入特性

第2章 逻辑门电路

图2-24 TTL与非门低电平输入特性

第2章 逻辑门电路

2) 输出特性是TTL与非门接入负载后,其输出电流与负载的关

(1) 输出逻辑高电平VOH和输出逻辑低电平VOL。 VOH和VOL的典型取值分别为3.6 V和0.3 V,但是,由于器件制 造中存在不可避免的差异,因此通常规定VOH≥3.0 V VOL≤0.3 V。器件手册规定,在额定负载情况下,VOHmin >2.4 V,VOLmax<0.8 V

第2章 逻辑门电路

或更多的输入,但只有一个输出。 通常,输入画在与门的一边,输出画在与门的另一边。两

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

【题2.1】试用真值表的方法证明下列异或运算公式。

(1)A⊕0=A

(2)A⊕1=A’

(3)A⊕A=0

(4)A⊕A’=1

(5)(A⊕B)⊕C=A⊕(B⊕C)

(6)A(B⊕C)=AB⊕AC

(7)A⊕B’=(A⊕B)’=A⊕B⊕1

【题2.2】证明下列逻辑恒等式(方法不限)

(1)AB’+B+A’B=A+B

(2)(A+C’)(B+D)(B+D’)=AB+BC’

(3)((A+B+C’)C’D)+(B+C’)(AB’D+B’C’)=1

(4)A’B’C’+A(B+C)+BC=(AB’C’+A’B’C+A’BC’)

【题2.3】已知逻辑函数Y1和Y2的真值表如表P2.3(a)、

P2.3(a)

【题2.4】已知逻辑函数和的真值表如表P2.4(a)、(b)所示,试写出对应的逻辑函数式。

P2.4(b)

【题2.5】列出下列逻辑函数的真值表。

(1)Y1=A’B+BC+ACD’

(2)Y2=A’B’CD’+(B⊕C)’D+AD

【题2.10】将下列各函数式化为最小项之和的形式。

(1)Y=A’BC+AC+B’C (2)Y=AB’C’D+BCD+A’D

(2)Y=A+B+CD (4)Y=AB+((BC)’(C’+D’))’

(5)Y=LM’+MN’+NL’(6)Y=((A⊙B)(C⊙D))’

【题2.15】用卡诺图化简法化简以下逻辑函数

(1)Y1=C+ABC

(2)Y2=AB’C+BC+A’BC’D

(3)Y3(A,B,C)=∑m(1,2,3,7)

(4)Y4(A,B,C,D)=∑m(0,1,2,3,4,6,8,9,10,11,14)

【题2.27】将下列逻辑函数化为或非—或非形式,并画出全部用或非逻辑单元组成的逻辑电路图。

(1)Y=AB’C+BC’

(2)Y=(A+C)(A’+B+C’)(A’+B’+C)

(3)Y=(ABC’+B’C)’D’+A’B’D

(4)Y=((CD’)’(BC)’(ABC)’D’)’。