硬件基带设计checklistV1.6-160222

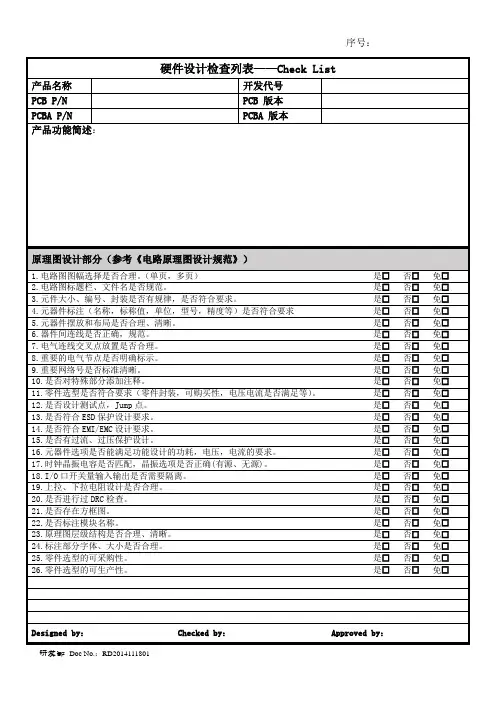

硬件-原理图布线图-设计审核表

23.当前版本的BOM是否需要变更确认。BOM 版本:_______, ECN:_________

是否免

24.过流保护是否工作正常,是否可靠

25.过压保护是否工作正常,是否可靠

Designedby:

Checkedby:

Approvedby:

是否免

4.元器件标注(名称,标称值,单位,型号,精度等)是否符合要求

是否免

5.元器件摆放和布局是否合理、清晰。

是否免

6.器件间连线是否正确,规范。

是否免

7.电气连线交叉点放置是否合理。

是否免

8.重要的电气节点是否明确标示。

是否免

9.重要网络号是否标准清晰。

是否免

10.是否对特殊部分添加注释。

是否免

11.零件选型是否符合要求(零件封装,可购买性,电压电流是否满足等)。

是否免

5.去耦电容摆放位置是否符合要求。

是否免

6.线宽,线距,GAP是否满足要求。

是否免

7.走线是否存在锐角、直角。

是否免

8.高频信号走线是否符合标准。

是否免

9.是否存在阻抗匹配要求。 阻抗匹配要求:

是否免

10.电源,GND是否符合要求。

是否免

11.器件PAD、焊盘大小是否符合要求。

是否免

12.过孔,通孔是否符合要求。

是否免

19.是否进行长时间可靠性测试(>=48H)。

是否免

20.当前版本是否需要Rework。ECN:___________________

是否免

21.当前版本原理图是否需要变更。原理图版本:________

是否免

22.当前版本PCB布线图是否需要变更。PCB版本:_______, ECN:_________

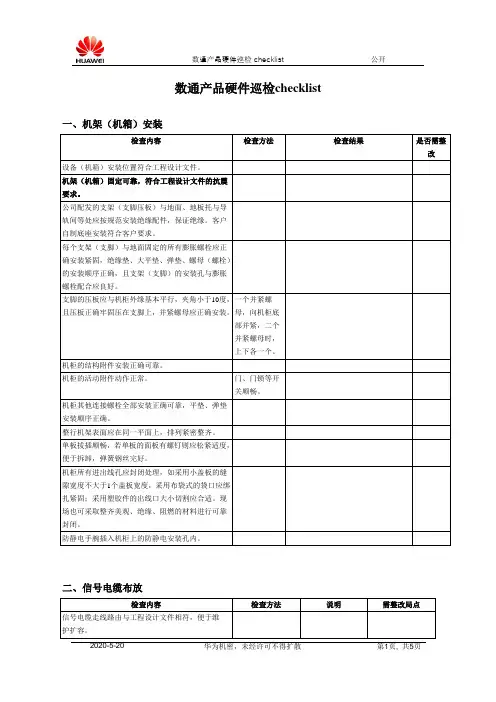

数通产品硬件巡检checklist

正确安装公司配发防雷箱。防雷箱到设备的交流电源线保留5-10m,多余部分可以盘绕。

电源线、地线一定要采用整段铜芯材料,中间不准许有接头。

地线、电源线连接至分线盒或PDF时,余长要剪除,不能盘绕。

并柜机柜间等电位线连接正确可靠。

电源线、地线与信号线分开布放。

机柜外电源线、地线与信号线间距符合设计要求,一般建议间距大于3cm。

机架或机箱内具有金属外壳或部分金属外壳的各种设备都应正确可靠接保护地。

一体化机框及盒式交流供电设备:

1、有直流保护地排时,设备的保护地接直流保护地排。

2、若无直流保护地排时,且条件不允许埋设接地体的情况下,可以通过交流电源的PE线接地,但应保证交流电源的PE线可靠接地。

五、其它

检查内容

检查方法

说明

需整改局点

1有直流保护地排时设备的保护地接直流保护地2若无直流保护地排时且条件不允许埋设接地体的情况下可以通过交流电源的pe线接地但应保证交流电源的pe线可靠接地

数通产品硬件巡检checklist

一、机架(机箱)安装

检查内容

检查方法

检查结果

是否需整改

设备(机箱)安装位置符合工程设计文件。

机架(机箱)固定可靠,符合工程设计文件的抗震要求。

保护套管应进入机柜内部,进入机柜内部的长度不宜超过10CM,且套管应绑扎固定。

尾纤保护套管切口应光滑,否则要用绝缘胶布等做防割处理。

尾纤布放:

1、布放尾纤时拐弯处不应过紧或相互缠绕,成对尾纤要理顺绑扎,且绑扎力度适宜,不能有扎痕。

2、尾纤在线扣环中可自由抽动,不能成直角拐弯。

3、布放后不应有其它电缆或物品压在上面。

在一个接线柱上安装两根或两根以上的电线电缆时,一般采取交叉或背靠背安装方式,重叠时建议将线鼻做450或900弯处理。重叠安装时应将较大线鼻安装于下方,较小线鼻安装于上方。

手机硬件设计Checklist-1

人工检查

15

FPC的设计应该保证每4~8根信号线就有一个地线, 如果有些信号的电流比较大,或者频率比较高,还 需要额外的包地线。

基带硬件 PCB

电源模块 布局布线 设计

原理图设 计

人工检查

对于有串联滤波网络的接口,除非滤波网络有特殊

ESD/EMI防

16

要求,并且滤波网络有足够的通流能力。否则防护 器件应该放在滤波网络和连接器之间,避免防护器

基带硬件 各种接口 原理图 功能模块

各种接口 功能模块

人工检查

电路中的MLCC电容耐压需要满足以下要求:当工作

27

电压大于等于5V时,所选电容要求降额达到60%,低 于5V,电容降额要求达到80%。Polymer钽电容耐压 要求:电压降额要求满足80%。电感、磁珠等的温升

基带硬件 原理图

电源管理 模块

计

11

ห้องสมุดไป่ตู้

防护器件要放在接口最入口处,但和射频天线冲突

时,可以适当调整。比如串联电感到Speaker,可以 把电感放在防护器件和Speaker之间,但必须考虑电 感的防静电能力,并且电感要放在Speaker附近,周

基带硬件 PCB

围没有其他可能间接放电的静电路径(地除外)

ESD/EMI防 护电路布 局布线设 计

序号

设计准则

主题 子主题 技术类别 检查方式

1

如果充电底座接口没有防呆结构设计防止正负极反 基带硬件 电源管理

接,则接口电路设计应该包含防反接保护电路

原理图 模块

原理图设 计

人工检查

2

在固定台手机中,要在听筒螺旋线接口处使用TVS或 基带硬件 音频功能

者对地并接电容进行防护;

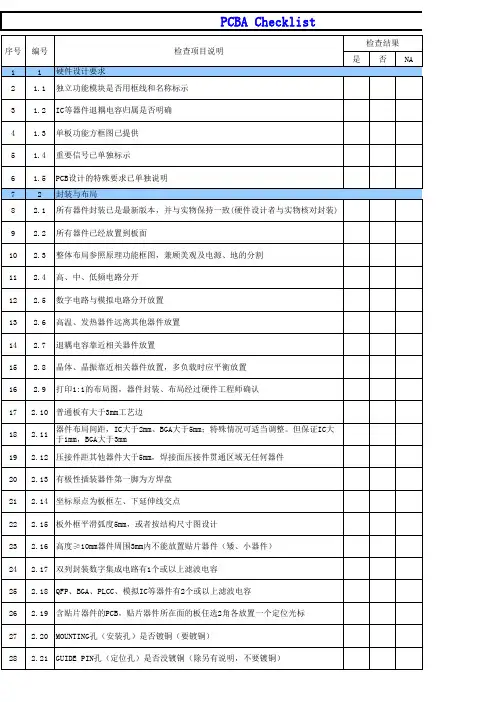

PCB设计检查表-PCB checklist

59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88

3.6 3.7 3.8 3.9

没有锐角和90布线 高速信号线、时钟信号线遵循回路面积最小原则 总体布线均匀,布线尽可能短,且少过孔 布线线宽保持一致,没有跳变

2.10 普通板有大于3mm工艺边 2.11 器件布局间距,IC大于2mm、BGA大于5mm;特殊情况可适当调整。但保证IC大 于1mm,BGA大于3mm

2.12 压接件距其他器件大于5mm,焊接面压接件贯通区域无任何器件 2.13 有极性插装器件第一脚为方焊盘 2.14 坐标原点为板框左、下延伸线交点 2.15 板外框平滑弧度5mm,或者按结构尺寸图设计 2.16 高度≥10mm器件周围3mm内不能放置贴片器件(矮、小器件) 2.17 双列封装数字集成电路有1个或以上滤波电容 2.18 QFP、BGA、PLCC、模拟IC等器件有2个或以上滤波电容 2.19 含贴片器件的PCB,贴片器件所在面的板任选2角各放置一个定位光标 2.20 MOUNTING孔(安装孔)是否镀铜(要镀铜) 2.21 GUIDE PIN孔(定位孔)是否没镀铜(除另有说明,不要镀铜)

29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58

2.22 元器件的1脚是否为方PAD 2.23 POWER PLANE 分割时是否出现瓶颈 2.24 BGA SOCKET 相同的POWER PIN 是否连接起来 2.25 BGA SOCKET相同的GND PIN 是否连接起来 2.26 BGA SOCKET的四圈及四角,是否加上DECOUBLING CAP 的PATTERN 2.27 是否在板上形成了一圈POWER RING(永不要在板上形成了一圈POWER RING,否 则会产生电磁噪音,可把POWER RING 割成两个半圈 )

戴尔硬件pcb设计checklist

戴尔硬件pcb设计checklist 戴尔硬件PCB设计Checklist

1. PCB设计前准备

在进行PCB设计之前,需要做以下准备工作:

- 确定电路功能和性能需求

- 选择合适的元器件

- 制定PCB设计方案

- 准备好必要的设计工具和软件

2. PCB设计中的注意事项

在进行PCB设计时,需要注意以下事项:

- PCB板面积和厚度要与电路需求匹配

- PCB布线要合理,避免信号交叉和干扰

- PCB元器件布局要合理,尽量缩短元器件间距离

- PCB的供电系统要稳定,避免电压波动

- 为PCB添加必要的测试点和排查故障点

3. PCB设计后的检查

在完成PCB设计后,需要进行以下检查:

- 检查PCB的电路连接是否正确

- 检查PCB的电气性能是否满足要求

- 检查PCB的机械尺寸和板面尺寸是否符合要求

- 检查PCB的焊盘、锡膏、防护层等是否符合生产标准4. PCB设计后的优化

在完成PCB设计后,可以进行以下优化:

- 优化PCB的电路布线和元器件排布

- 优化PCB的供电系统和防护层

- 优化PCB的机械结构和布局

- 优化PCB的测试点和排查故障点

5. PCB设计的注意事项

在进行PCB设计时,需要注意以下事项:

- 所有元器件的电气性能参数应符合要求

- PCB的机械结构和尺寸应与产品需求匹配

- PCB的测试点和排查故障点要定位准确

- PCB的焊盘、锡膏、防护层等需要满足生产标准

6. 结论

通过以上的检查和优化,可以减少PCB设计中出现的故障和问题,并最终得到满足需求的电路板。

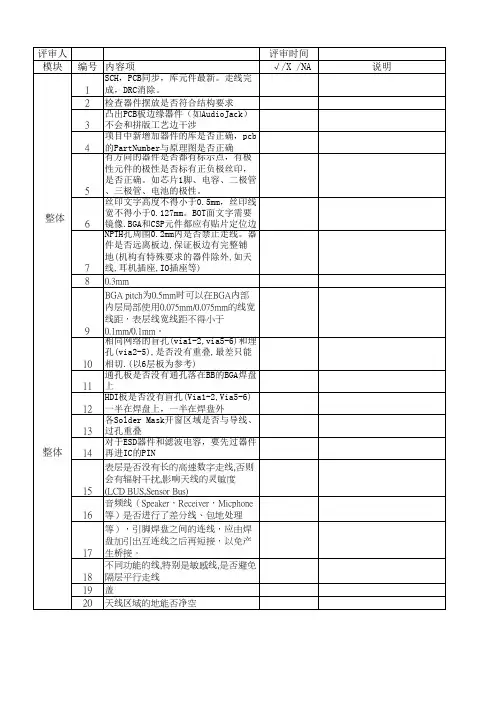

PCB评审CHECK LIST

SCH,PCB同步,库元件最新。走线完 成,DRC消除。 检查器件摆放是否符合结构要求 凸出PCB板边缘器件(如AudioJack) 不会和拼版工艺边干涉 项目中新增加器件的库是否正确, pcb的PartNumber与原理图是否正确 有方向的器件是否都有标示点,有极 性元件的极性是否标有正负极丝印, 是否正确。如芯片1脚、电容、二极 管、三极管、电池的极性。 丝印文字高度不得小于0.5mm,丝印 线宽不得小于0.127mm。BOT面文字需 要镜像.BGA和CSP元件都应有贴片定 NPTH孔周围0.2mm内是否禁止走线。 器件是否远离板边,保证板边有完整 铺 地(机构有特殊要求的器件除外,如天 各个器件之间的距离是否满足最 0.3mm 建议最小线宽线距为0.1mm/0.1mm, BGA pitch为0.5mm时可以在BGA内部 内层局部使用0.075mm/0.075mm的线 宽线距,表层线宽线距不得小于 0.1mm/0.1mm。 相同网络的盲孔(via1-2,via5-6)和 埋孔(via2-5),是否没有重叠,最差只 能 通孔板是否没有通孔落在BB的BGA焊 盘上 HDI板是否没有盲孔(Via1-2,Via5-6) 一半在焊盘上,一半在焊盘外 各Solder Mask开窗区域是否与导线 、过孔重叠 对于ESD器件和滤波电容,要先过器 件再进IC的PIN 表层是否没有长的高速数字走线,否则 会有辐射干扰,影响天线的灵敏度 (LCD BUS,Sensor Bus) 音频线(Speaker,Receiver,Micphone 等)是否进行了差分线、包地处理 多引脚的元器件(如SOIC、QFP 等),引脚焊盘之间的连线,应由焊 盘加引出互连线之后再短接,以免产 生桥接。 不同功能的线,特别是敏感线,是否避 免隔层平行走线 必须对BB芯片进行有效屏蔽,加屏 蔽盖 天线区域的地能否净空

华为硬件pcb设计checklist

附录B (规范性附录)器件间距要求

表B.1

4 BGA外形与其他元器件的间隙≥

5 mm(200 mil)。

5 PLCC表面贴转接插座与其他元器件的间隙≥3 mm(120 mil)。

6 表面贴片连接器与连接器之间应该确保能够检查和返修。

一般连接器引线侧应该留有比连接器高度

大的空间。

7 元件到喷锡铜带(屏蔽罩焊接用)应该2mm(80mil)以上。

8 元件到拼板分离边需大于1mm(40mil)以上。

9 如果B面(焊接面)上贴片元件很多、很密、很小,而插件焊点又不多,建议插件引脚离开贴片元

件焊盘5mm以上,以便可以采用掩模夹具进行局部波峰焊。

注:其中间隙一般指不同元器件焊盘间的间隙,器件体大于焊盘时,指器件体的间隙)

附录C

(规范性附录)

内外层线路及铜箔到板边、非金属化孔壁的尺寸要求

表C.1单位:mm(mil) 板外形要素内层线路及铜箔外层线路及铜箔

距边最小尺寸一般边≥0.5(20) ≥0.5(20) 导槽边≥1(40) 导轨深+2

附录D (规范性附录)PCB布线最小间距

表D.1

附录E

(资料性附录)

丝印字符大小 (参考值)

表E.1。

硬件单板详细设计文档模板

硬件单板详细设计文档模板1. 引言在本文档中,将详细地描述硬件单板的设计。

该设计旨在满足特定需求,并确保硬件单板的性能、可靠性和可扩展性。

本文档将提供硬件单板设计的详细信息,包括硬件组件、接口、电源、尺寸等方面的规格。

2. 总体设计2.1 硬件单板功能描述硬件单板的功能和主要特点,包括所需的输入和输出接口。

2.2 系统框图展示硬件单板与其他系统组件之间的连接关系,包括传感器、处理器、内存等。

2.3 总体架构描述硬件单板的整体架构,包括主要模块的布局和互联方式。

3. 硬件组件设计3.1 处理器描述所选用的处理器类型、主频、存储器等硬件规格。

3.2 存储器包括闪存、RAM等存储器组件的详细设计。

3.3 电源系统描述硬件单板所需的电源系统设计,包括电源输入、功率管理等内容。

3.4 接口设计描述与其他组件之间的接口设计,包括输入输出接口、通信接口等。

4. 物理布局设计4.1 尺寸和外观描述硬件单板的尺寸、外壳材料、散热设计等方面的设计。

4.2 微控制器和传感器的连接描述微控制器和传感器之间的物理连接方式和布局。

4.3 硬件板层间堆叠描述不同硬件板层之间的堆叠方式和间隙。

5. 测试计划5.1 功能测试定义硬件单板的功能测试计划,包括各个模块的测试目标和方案。

5.2 性能测试定义硬件单板的性能测试计划,包括各个性能指标的测试方法和要求。

5.3 可靠性测试定义硬件单板的可靠性测试计划,包括温度、湿度、震动等环境条件下的测试方案。

6. 风险分析分析硬件单板设计中的潜在风险,并提供相应的风险缓解措施。

7. 设计验证描述硬件单板设计的验证方法和步骤,包括实验室测试、原型验证等。

8. 结论总结硬件单板的详细设计文档,并强调设计的主要亮点和创新之处。

通过以上的详细设计文档模板,可以清晰地呈现硬件单板的设计思路、规格和验证计划。

这样的设计文档能够为硬件开发人员提供一个明确的指导,确保设计的正确性和完整性。

同时,该文档也可作为后续项目的参考和文档基础,便于团队成员之间的沟通与合作。

电子产品拆机检查checklist

壳体上固定无松动

5

插拔件在插拔过程中是否有干涉到壳体?

6

按键是否有误触设置?是否有手感弱,行程不够 问题?

7

装配件之间间隙合理?

8

是否有防小部件进入措施?

9

输入&输出线在组装,使用过程中不可以是受力状 态

10

PCB板固定方式是否合理?

11

装配类 密封件密封方式是否合理?

12

导电触片可靠,稳定?

13

装配方向是否有导引设计?

项目号: 序号 类别

仪器产品拆装评审checklist

检查者:

日 期:

描述Βιβλιοθήκη 是否适用 检查结果 备注1

产品是否存在尖角、利边?

2

结构件柱位/卡扣/等结构是否设计合理?强度是 否足够?

3

螺丝柱的设计是否符合规范(参考表格2)

结构类 输入&输出线在壳体上作必要的护线设计以避免接

4

触金属锐边,且要求直接焊板的输入、输出线在

14

插头是否有接触不良?是否容易松脱?(是否有 打胶)

15

五金件不能用自攻螺丝

16

所选材料是否耐高温?是否可以过环测?

17

螺丝柱选配螺丝是否符合要求,扭力是否符合要 选材类 求?(参考表格2)

18

有无做到防呆设计?

19

所选材料是否符合国家标准?(电池,电机等)

20

电池/电机/PCB上是否有丝印规格版本号?

硬件审查表checklist

Pass Failed NG Pass Failed NG

结论 Pass Failed NG Pass Failed NG Pass Failed NG Pass Failed NG

说明

说明 说明 说明 说明 说明

5. EMC/EMI设计

评审项

评审内容

结论

高速时钟线是否有匹配电路?波形是否单调?

NGPass Failed

1.1.8

高频变压器次级输出端是否有+/-之分,+端输出焊盘是否为方焊盘,-端 NGPass Failed

输出焊盘是否为圆焊盘,且丝印清晰

NG

1.1.9 1.1.10 1.1.11 1.1.12 1.1.13

1.1.14

高压侧和低压侧之间是否有PCB挖槽,且高压侧和低压侧电距离最小应大 Pass Failed

1.2 DC-DC设计

评审项

评审内容

结论

1.2.1 是否有防接反电路

Pass Failed

1.2.2 输入电容的耐压是否满足要求

Pass Failed

1.2.3 异步Buck结构需要续流二极管,同步Buck结构不需要续流二极管

Pass Failed

1.2.4 是否需要防输出端电流倒灌二极管

有源晶振的精度是否满足设计需求

Pass Failed NG

有源晶振的波形(正弦波/方波,电压)是否满足设计要求

Pass Failed NG

有源晶振(TCXO/OCXO)的散热设计是否足够。

Pass Failed NG

2.3 时钟线设计

评审项

评审内容

结论

时钟线实际长度和波长相比拟时(大于1/10波长),源端和终端阻抗是否 Pass Failed NG

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

变更记录 2014.01.03 V1.0首次整合发布 2014.07.15 V1.1精简优化,同时合入最新的checklist条目 2014.11.13 V1.2各条目有内容增减,同时加入《NFC设计checklist》;专业组人员重新调整;大功率掉卡 checklist改名为:冲突checklist,包含大功率掉卡。 2015.2.28 V1.3更新内容:1)各条目均有增删;2)增加《WP项目设计checlklist》 2015.4.14 V1.4更新内容:1)各条目均有增删 2015.11.21 V1.5更新内容: 1)专业组取消; 2)音频及TDD改名为音频,FM合并入音频部分; 3)新增开关机checklistV1.1、可靠性设计checklistV1.1; 4)其余各模块 条目均有修改,热设计部分部分修改较大; 5) ESD负责人改为乔洋,NFC负责人改为王欢; 2016.2.22 V1.6更新内容(主要吸取QL1900项目经验): 1)通用化部分变更为checklistV1.4; 2)可靠性部分变更为checklistV1.2; 3)EMC设计要求从通用化提取到冲突部分中。

1)引导该领域的技术研究、设计方案、器件选型; 2)在其它项目出现相关问题时,必要时介入,给出方案意见; 3)专业负责人职称评定中作为考评纬度之一,有优先权; 4)其它专业在必要时引入,增加负责人。

调整;大功率掉卡

论不满足项是否可以 核放在走线评审会前

负责人 王锋 乔洋 周培杰 贾庆辉 张鹏 高帅 孙钦利 梁晓帧 张萌 王欢

硬件设计checklist执行总则 1.该checklist执行的检查的第一责任人为对应项目开发经理。 2.要求以项目原理图和走线评审为检查点,评审时需要提交checklist自查结果,会上讨论不满足项是否可以 放行。原理图评审时重点检查原理图和布局的相关checklist,走线部分的checklist审核放在走线评审会前 完成。 3.各个checklist维护的任务为各专业专家,要求各专业至少每季度更新一次。 4.项目投板后三天内要求完成归档,归档地址为PDS系统。 专业划分 1 2 3 4 5 6 7 8 9 10 音频----音频checklistV1.4 ESD----ESD_checklistV1.4 热设计、热仿真---硬件热设计checklistV1.2、WP项目设计checklistV1.2 光电类---硬件通用化checklistV1.2 冲突---冲突checklistV1.2 可靠性---可靠性设计checklistV1.1 开关机---开关机checklistV1.1 EMCP---硬件通用化checklistV1.3 其它暂未化分的专业---硬件通用化checklistV1.3 NFC---NFC(BCM)设计