第3章 CMOS基本单元电路

《CMOS集成电路基础》课件

NMOS

当输入为0时,导通;当输入为1时,截止。

输出

输出反相的输入信号。

CMOS电路组成:CMOS传输门

1 输入端

接收多个输入信号。

3 PMOS

通过开关和截止的方式传递输入信号。

2 NMOS

通过开关和导通的方式传递输入信号。

4 输出端

输出根据输入信号进行逻辑运算的结果。

晶圆切割

将完成的硅片切割成晶圆,以便后续封 装和测试。

CMOS电路组成:MOS管

N沟道MOS管(NMOS)

由N型沟道和P型沟道构成,可以实现电流的传输和 放大。

P沟道MOS管(PMOS)

由P型沟道和N型沟道构成,用于控制电流的开关。

CMOS电路组成:CMOS反相器

输入

接收输入信号(0或1)。

PMOS

CMOS电路组成:CMOS与门

1

输入A

接收输入信号A。

输入B

2

接收输入信号B。

3

NMOS

当输入A为1且输入B为1时,导通。

PMOS

4

Байду номын сангаас

当输入A为0且输入B为0时,导通。

CMOS电路组成:CMOS或门

1

输入A

接收输入信号A。

输入B

2

接收输入信号B。

3

NMOS

当输入A为1且输入B为1时,截止。

PMOS

CMOS的基本工艺流程

1

清洗和蚀刻

2

对硅片进行清洗和蚀刻,去除杂质和氧

化物,并形成特定的表面。

3

沉积

4

在硅片上沉积各种材料,如金属、氧化

物和多晶硅等,用于构建电路的不同部

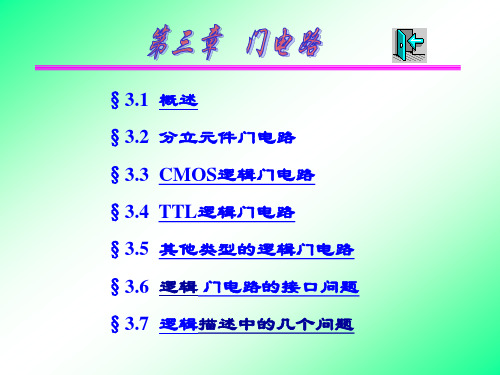

数字逻辑第3章 门电路

逻辑式:Y=A + B

逻辑符号: A 1

B

Y

电压关系表

uA uB uY

0V 0V 0V 0V 3V 2.3V 3V 0V 2.3V 3V 3V 2.3V

真值表

ABY

0

0

0

0

1

1

1

0

1

1

1

1

三、三极管非门

5V

利用二极管的压降为0.7V, 保证输入电压在1V以下时,

电路可靠地截止。

A(V) Y(V) <0.8 5 >2 0.2

II H &

II L &

… …

NOH

I OH (max) I IH

N MIN ( NOH , NOL )

NOL

IOL(max) I IL

六、CMOS漏极开路门(OD)门电路(Open Drain)

1 . 问题的提出

普通门电路

在工程实践中,往往需要将两个门的输出端 能否“线与”?

并联以实现“与”逻辑功能,称为“ 线与 。

输入 0 10% tr tf

tPHL

输出

tPLH

tr:上升时间

tf:下降时间 tw:脉冲宽度 tPHL:导通传输时间

tPLH:截止传输时间

平均传输延迟时间 (Propagation delay)

tpd= tpHL+ tpLH 2

5、功耗: 静态功耗:电路的输出没有状态转换时的功耗。 动态功耗:电路在输出发生状态转换时的功耗。

PMOS

NMOS

3、增强型MOSFET的开关特性

iD管可变子类型恒

VGS1 击开/关的条(件1)N沟道增强开型/M关O的S等FE效T电:路

CMOS电路基础原理

CMOS电路基础原理CMOS(互补金属氧化物半导体)电路是现代电子领域中常用的集成电路设计技术。

它在数字逻辑电路和模拟电路中广泛应用,并且具有低功耗、高集成度以及较强的抗干扰能力等优点。

本文将介绍CMOS电路的基础原理。

一、CMOS电路结构CMOS电路由N沟道金属氧化物半导体场效应管和P沟道金属氧化物半导体场效应管构成。

N沟道和P沟道管具有互补的传输特性,能够有效降低功耗。

CMOS电路结构包括传输门、组合逻辑电路和时钟电路等。

1. 传输门传输门是CMOS电路的基本单元,常见的有与门、或门以及非门等。

与门由一对并联的P沟道和N沟道管组成,当且仅当两个输入信号同时为高电平时,输出为高电平。

或门由一对串联的P沟道和N沟道管组成,当且仅当两个输入信号中至少一个为高电平时,输出为高电平。

非门由两个逆并联的P沟道和N沟道管组成,当输入信号为高电平时,输出为低电平。

2. 组合逻辑电路CMOS电路中的组合逻辑电路包括与非门、异或门等。

与非门由与门和非门级联而成,输入信号经过与门进行与操作,然后再经过非门进行取反操作。

异或门由与非门和异或非门级联而成,输入信号经过与非门进行与非操作,然后再经过异或非门进行异或操作。

3. 时钟电路CMOS电路中的时钟电路包括振荡电路和触发器等。

振荡电路用于产生稳定的时钟信号,常见的电路有RC振荡电路和LC振荡电路等。

触发器用于存储和传输信息,常见的触发器有RS触发器、D触发器以及JK触发器等。

二、CMOS电路工作原理CMOS电路的工作原理基于PN结和MOSFET的特性。

当控制电压施加于PN结时,PN结正向偏置导通,反向偏置截止。

同时,对于MOSFET来说,当栅极电压低于阈值电压时,沟道断开;当栅极电压高于阈值电压时,沟道导通。

CMOS电路中,P沟道MOSFET和N沟道MOSFET的栅极交替连接,形成互补对。

当输入信号为低电平时,P沟道MOSFET导通,N 沟道MOSFET截止;当输入信号为高电平时,P沟道MOSFET截止,N沟道MOSFET导通。

数字电子技术基础 第三章(1)11-优质课件

图3.1.2 正逻辑与负逻辑

一些概念

1、片上系统(SoC) 2、双极型TTL电路 3、CMOS

1961年美国TI公司,第一片数字集成电路 (Integrated Circuits, IC)。

VLSI(Very Large Scale Integration)

3.2 半导体二极管门电路

3.2.1 半导体二极管 的开关特性

图3.2.1 二极管开关电路

可近似用PN结方程和下图所 示的伏安特性曲线来描述。

i Is ev/VT 1

其中:i为流过二极管的电流。 v为加到二极管两端的电压。

nkT VT q

图3.2.2 二极管的伏安特性

图3.2.3 二极管伏安特性的几种近似方法

三、电源的动态尖峰电流

图3.5.23 TTL反相器电源电流的计算 (a)vO=VOL 的情况 (b) vO=VOH的情况

图3.5.24 TTL反相器的电源动态尖峰电流

图3.5.25 TTL反相器电源尖峰电流的计算

图3.5.26 电源尖峰电流的近似波形

例3.5.4 计算f=5MHz下电源电流的平均值

图3.3.xx CMOS三态门电路结构之二 (a)用或非门控制 (b)用与非门控制

图3.3.xx CMOS三态门电路结构之三 可连接成总线结构。还能实现数据的双向传输。

3.3.6 CMOS电路的正确使用

一、输入电路的静电防护

1、在存储和运输CMOS器件时最好采用金属屏蔽层 作包装材料,避免产生静电。

tPHL:输出由高电平跳变为低电 平的传输延迟时间。

tPLH:输出由低电平跳变为高电 平的传输延迟时间。

tPD: 经常用平均传输延迟时间tPD

来表示tPHL和tPLH(通常相等)

成都理工大学 数字电子基础第三章TTL和CMOS电路

电源VCC(+5V)

外形

地GND

管脚

74LS00内含4个2输入与非门, 74LS20内含2个4输入与非门。

2.或非门

有1出0,全0出1

T2与T2'形成或 逻辑关系 ABA为为 、高高B都电电为平平低时时电,,

T通 输 T通 输 平 同 截22、 ′, 出 , 出 时 止时、T截 ,TYTY,T544为 为5同截 截止TT同42低 低时止 止、 导,时电 电导, ,T通T导25平 平′,。 。

vo

t pd 2 (t pdLH t pdHL )

原因

结电容(D和T)的存在 o

分布电容的影响

50% t

tpdHL

50% t tpdLH

§3.5.5 其他类型的TTL门电路

一. 其他逻辑功能的门电路

1. 与 非 门

Y (A B)

输入端改成多发 射极三极管

TTL集成门电路的封装:

双列直插式

如:TTL门电路芯片(四2输入与非门,型号74LS00 )

相当于断开的开关,vO≈vDD.

当vI>VGS(th)且vI继续升高时,MOS管工作在可变 电阻区。MOS管导通内阻RON很小,D-S间相当于闭合

的开关,vO≈0。

四、MOS管的四种基本类型

D

D

G

S N沟道增强型

G

S N 沟道耗尽型

D

G S

P 沟道增强型

D

G S

P 沟道耗尽型

在数字电路中,多采用增强型。

一、TTL反相器的电路结构和工作原理

输入级 倒相级 输出级

称为推拉式 电路或图腾 柱输出电路

二、电压传输特性

1.3V 0.6V

华中科技大学CMOS拉扎维第三章课后作业中文答案

3.1分析:对于PMOS 和NMOS 管二极管连接形式的CS 放大电路,最大的区别在于PMOS 做负载无体效应,所以这里应该考虑g mb 的影响。

同时,由于L=0.5,沟道长度比较短,所以,沟长调制效应也应该考虑进去。

2441401034.11099.31085.8350μμ2V A t C OX sio nOX n ---⨯=⨯⨯⨯⨯=∙=εε 同理 25p 10835.3μV A C OX -⨯=∵ 5.0501=⎪⎪⎭⎫⎝⎛L W 5.0102=⎪⎪⎭⎫ ⎝⎛L W A I I D D m 5.021== ∴ K I r DN o o 201r 21===λ()()22222n 2121DS N TH GS ox D V V V L W C I λμ+-⎪⎪⎭⎫ ⎝⎛= V O = 1.46V V A I LWC D OX m /106.32g 31-⨯==μ VA m /1063.1g 32-⨯=V A V g SBF m m /1038.222g 422b -⨯=+=φγ输出电阻:Ω=++=-508//g 1R 11222o o mb m OUT r r g∴增益 85.1g A 1-=-=OUT m V RM2换为PMOS 管,则可忽略M2的体效应,同理可得Ω=+=-974//g 1R 1122o o m OUT r r∴增益 85.0g A 1-=-=OUT m V R3.2 (a )∵ 5.0501=⎪⎪⎭⎫⎝⎛L W 2502=⎪⎪⎭⎫ ⎝⎛L W A I I D D m 5.021== ∴ K I DN o 201r 1==λ K I DP o 101r 2==λ又 2401034.1μμ2V A t C OXsion OX n -⨯=∙=εε∴ V A I LWC D OX m /106.32g 31-⨯==μ∴增益 ()4.24//r g A 211-=-=o o m V r(b )求输出电压的最大摆幅及求输出电压最大值与最小值之差 分析可知,当M1管处于临界三极管区时输出电压有最小值V omin ,此时有:11TH GS DS OUT V V V V -==()()DS N TH GS ox D V V V L W C I λμ+-⎪⎪⎭⎫ ⎝⎛=121211n 有以上两式可推得 V omin =0.27当M2管处于临界三极管区是输出电压有最大值V omax ,同理有:()()SDP TH GS ox D V V V L W C I λμ+-⎪⎪⎭⎫ ⎝⎛=121222pV SDMIN = 0.99 ∴ V omax = V DD -V SDMIN = 2V ∴输出电压的最大摆幅为V omax - V omin = 1.73V3.3 (a )∵5.050=⎪⎪⎭⎫⎝⎛L W A I D m 11= Ω=K R D 2∴K I DN o 101r ==λK R D o O U T 66.1//r R 1==V A I LWC D OX m /1018.52g 31-⨯==μ∴ 增益 86.0g A 1-=-=OUT m V R (b )∵M1工作在线性区边缘 ∴ TH GS DS OUT V V V V -==1()DO U TDD THGS ox D R V V V V L W C I -=-⎪⎪⎭⎫ ⎝⎛=21n 21μ由以上两式可得 V V GS 13.1= , A I D 3-1028.1⨯= ∴K I DN o 8.71r ==λ∴ 增益 ()34.9//r g A 1-=-=Do m V R(c )各区域主要由DS V 决定,进入线性区50mV 即三极管临界区的DS V 减小50mV ∵ 临界区的V R I V V D D DD DS 44.0=-= 所以进入线性区50mV 时的DS V =0.39V∴A R V V I DDSDD D 3103.1-⨯=-==∴ ()()V V V V V V L W C I GS DS DS TH GS ox D 14.122121n =⇒--⎪⎪⎭⎫ ⎝⎛=μ又∵ 三极管区 19.5g 1n =⎪⎪⎭⎫⎝⎛=DS ox m V L W C μ()K R V V V L W C V I R O DS TH GS ox DS D O28.111n 1=⇒--⎪⎪⎭⎫⎝⎛=∂∂=-μ ∴增益 ()4//R g A -=-=Do m V R3.12分析:已知各支路电流及M1宽长比,可求得M1过驱动电压即out V ,从而由M2的gsV 及电流可求得其宽长比。

cmos电路和器件基本结构

cmos电路和器件基本结构CMOS电路和器件基本结构一、引言CMOS(亦称为互补金属-氧化物-半导体)电路是一种常用的逻辑电路,它由NMOS(N型金属-氧化物-半导体)和PMOS(P型金属-氧化物-半导体)两种互补型的MOSFET(金属-氧化物-半导体场效应晶体管)组成。

CMOS电路以其低功耗、高集成度和低电压操作等特点,在现代集成电路设计中得到广泛应用。

本文将介绍CMOS电路和器件的基本结构。

二、CMOS电路的基本结构1. NMOS器件NMOS器件由P型衬底上生长的N型沟道和两个掺入P型源极和漏极的P型扩散区组成。

沟道区域上方由一层薄的氧化硅(SiO2)作为绝缘层,上面再覆盖一层金属(通常为铝)作为电极。

当沟道区没有电压施加时,NMOS处于截止状态,导通状态需要在沟道区施加正电压。

2. PMOS器件PMOS器件与NMOS器件相反,由N型衬底上生长的P型沟道和两个掺入N型源极和漏极的N型扩散区组成。

沟道区域上方同样有一层氧化硅和金属电极。

当沟道区施加负电压时,PMOS处于导通状态,截止状态需要在沟道区施加正电压。

3. CMOS电路CMOS电路是通过将NMOS和PMOS器件相互串联或并联而构成的。

在CMOS电路中,NMOS器件的漏极与PMOS器件的源极相连,共同组成电路的输出端;NMOS器件的源极与PMOS器件的漏极相连,共同组成电路的输入端。

当输入信号施加到NMOS和PMOS器件上时,根据不同的输入信号电平,其中一个器件处于导通状态,另一个器件处于截止状态,从而实现电路的逻辑功能。

三、CMOS电路的工作原理CMOS电路的工作原理是基于MOSFET的三个重要特性:沟道截止、沟道饱和和门极电势控制。

当输入信号为低电平时,NMOS处于导通状态,PMOS处于截止状态,此时电路输出为高电平;当输入信号为高电平时,NMOS处于截止状态,PMOS处于导通状态,此时电路输出为低电平。

由于CMOS电路的输出仅在输入发生变化时才会改变,且输出信号的上升和下降均经过一个NMOS和一个PMOS器件,因此CMOS电路具有较低的功耗和较高的抗噪声能力。

第三章-CMOS门电路

3.3.1 MOS管的开关特性 第一页 上一页 下一页

最后 一页

结束 放映

BJT是一种电流控制元件(iB~ iC),工作时,多数 载流子和少数载流子都参与运行,所以被称为双极型 器件。

MOS管是一种电压控制器件(uGS~ iD) ,工作时, 只有一种载流子参与导电,因此它是单极型器件。

MOS管因其制造工艺简单,功耗小,温度特性好, 输入电阻极高等优点,得到了广泛应用。

3.3.3 其它类型的CMOS门电路

第一页 上一页 下一页

最后 一页

结束 放映

1. 其他逻辑功能的CMOS门电路(P91~93)

在CMOS门电路的系列产品中,除了反相器外常用的还 有与门、或门、与非门、或非门、与或非门、异或门等 。 2. 漏极开路的门电路(OD门)

如同TTL电路中的OC门那样,CMOS门的输出电路结 构也可做成漏极开路(OD)的形式。其使用方法与TTL的 OC门类似。

强。

原因:TTL的输出电阻小。5mA内 变化很小IOH

实际只有0.4mA

21

3.3.4 CMOS反相器的动态特性(门电第路一页状上态一页切下一换页 时最一后页

结束 放映

所呈现的特性)

tPLH:输出由低电平变为高电平的传输延迟时间 tPHL:输出由高电平变为低电平的传输延迟时间

22

CMOS反相器传输延迟的原因:

24

第一页 上一页 下一页

最后 一页

结束 放映

漏极开路的门电路(OD门)(Open-Drain)

VDD1

内部逻辑 A B

VDD2 使用时必须外接上拉电阻

D vO

G

TN•

S

RL

Y=(AB)'

第 3 章 逻辑门电路总结

EXIT

逻辑门电路

一、三极管的开关作用及其条件

iC 临界饱和线 M T IC(sat) S

放大区

IB(sat)

uI=UIL

三极管为什么能用作开关? 饱 Q + 怎样控制它的开和关? uBE 和 区

O UCE(sat) B uBE < Uth

负载线

A N C

截止区

uCE

三极管关断的条件和等效电路

当输入 uI 为低电平,使 uBE < Uth时,三极管截止。

逻辑门电路

第3章

逻辑门电路

概 述 三极管的开关特性

TTL 集成逻辑门 CMOS 集成逻辑门 集成逻辑门的应用

本章小结

EXIT

逻辑门电路

3.1

主要要求:

概 述

了解逻辑门电路的作用和常用类型。 理解高电平信号和低电平信号的含义。

EXIT

逻辑门电路

一、门电路的作用和常用类型

按逻辑功能不同分 指用以实现基本逻辑关系和 门电路 (Gate Circuit) 常用复合逻辑关系的电子电路。 与门 或门 非门 异或门 与非门 或非门 与或非门 按电路结构不同分

上例中三极管反相 器的工作波形是理想波 形,实际波形为 :

t

UCE(sat) O

EXIT

逻辑门电路

二、三极管的动态开关特性

uI

UIH

UIL O iC 0.9IC(sat) IC(sat) 0.1IC(sat) O uO VCC ton toff t

uI 正跳变到 iC 上升到 0.9IC(sat) 所需的时间 ton 称 为三极管开通时间。

逻辑门电路

(2) 对应输入波形画出输出波形 三极管截止时, iC 0,uO +5 V 三极管饱和时, uO UCE(sat) 0.3 V

拉扎维模拟CMOS集成电路设计第三章作业答案详解完整版教程解析

拉扎维模拟CMOS集成电路设计第三章作业答案详解完整版教程解析1. 引言在拉扎维模拟CMOS集成电路设计第三章的作业中,涉及了多个内容,包括放大电路、反馈放大电路、功率放大电路等。

本文将对这些内容进行详细的解析和讲解,并给出相应的答案。

2. 放大电路放大电路是电子电路中非常常见且重要的一种电路结构。

在本章的作业中,我们需要设计一个放大电路,并回答一些相关问题。

2.1 放大电路设计根据作业要求,我们需要设计一个放大电路,输入信号为正弦波,放大倍数为10倍。

我们可以选择使用CMOS集成电路来实现这个放大电路。

首先,我们需要根据放大倍数和输入信号的幅度来确定CMOS放大电路的电路参数。

在设计过程中,我们需要考虑一些关键因素,包括电流源、负反馈电阻等。

其次,我们可以选择合适的电路拓扑结构,例如共源共栅放大电路、共源共漏放大电路等。

根据实际情况,我们可以选择合适的电路结构。

最后,我们需要进行电路参数的计算和电路的仿真。

通过计算和仿真,我们可以得到放大电路的性能指标,例如增益、截止频率等。

2.2 放大电路问题解答在作业中,还需要回答一些问题,例如输入电阻、输出电阻、频率响应等。

针对这些问题,我们需要根据放大电路的拓扑结构和电路参数做相应的计算和分析。

例如,输入电阻可以通过计算输入端的电流和电压之比得到;输出电阻可以通过计算输出端的电流和电压之比得到;频率响应可以通过对放大电路进行交流分析得到。

总的来说,放大电路的设计和问题解答需要综合考虑多个因素,包括电路参数、电路结构、输入信号的幅度、负载等。

需要进行一系列的计算和仿真,以得到满足要求的电路性能。

3. 反馈放大电路反馈放大电路是一种常见的电路结构,它可以通过引入反馈回路来改善电路性能,例如增益稳定性、线性度等。

在作业中,我们需要设计一个反馈放大电路,并回答一些相关问题。

3.1 反馈放大电路设计根据作业要求,我们需要设计一个反馈放大电路,输入信号为正弦波,放大倍数为20倍。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

W 1/L 1 M1

W 2/L 2 M2

M1 W 1/L 1

M2 W 2/L 2

IREF

Rout

Iout

NMOS

ห้องสมุดไป่ตู้

PMOS

W2 / L2 W2 L1 I out I I REF W1 / L1 REF W1 L2

(理想情况)

Iout与IREF的比值由M1与M2的尺寸比率决定,不受电源电压、工艺

和温度的影响(理想情况)

M1工作在饱和区(Vds=Vgs,Vgd=0),同时为M2提供偏置电压。

4

基本电流镜的误差(沟道长度调制引起)

I

REF

C

n

OX

2

W ( )(V V ) (1 V ) L

1 2 gs th ds 1 1

I

C

n

OX

OUT

2

W ( )(V V ) (1 V ) L

线性区

静态偏置电压不同,放大管 工作在不同的区域,应保证工 作在饱和区。

12

电压放大原理(在饱和区,电阻负载)

ut

13

电阻负载放大器的优缺点

电阻负载(直流电阻与交流电阻相同)的缺点:

电压放大倍数Av= -gm(RL//rds1) ,

为了增大Av → 增大RL → 限制输出电压的摆幅;

CMOS工艺条件下制作大电阻(数百KΩ)会占用较大芯

片面积;

增加静态(直流)功耗(Ids2 ×RL)。

电阻负载的优点: 产生较小的寄生电容和噪声电压,适应于低增益高频 放大器(RF电路中)。

14

共源极放大器(电流镜作为有源负载)

NMOS放大管

Vdd M3 Vin M1

S

PMOS放大管

Vdd Vdd

S

Active load M2 Vout

Ibias

M2 Vout

Ibias

2)当Vin>Vth1时,M1和M2都进入饱和区, 漏极电流基本保持恒定(电流镜的作 用),Vout开始减小 3)当Vin> Vout +Vth1 (或Vout< Vin -Vth1) 时,M1进入线性区

输出电压Vout的下限是M1的过驱动电压( Vin -Vth1),而输出电压 的上限是Vdd减去M2的过驱动电压(|VGS2 –Vth2|),因此,输出电压 的摆幅是电源电压减去两个过驱动电压,即

小信号特性与二极管 等效,故称为二极管连 接的MOS管。

10

3.2 共源极放大器(电阻负载)

Vdd 负载线 Vout = Vdd - RLIds Ids RL

Vin0

Vout Vin

Vin0

Vin

vin VDD Vds

Source端交流接地

11

共源极放大器的输入-输出特性(大信号特性)

截止区

饱和区

7

多路输出电流镜(输出电流导向)

VDD

VDD IREF M0 W0/L0

Sink current

I1

M3 W3/L3 I3 I2

M4 W4/L4 I4

M1 W1/L1

M2 W2/L2

Source current

I1

W1 / L1 I REF W0 / L0

I 2 I3

W2 / L2 I REF W0 / L0

第3章 CMOS基本单元电路

魏廷存/2008年

1

单级放大器的特性

直流或低频增益(DC Gain) 频率特性(带宽) 动态响应速度(Slewing rate,Settling time) 功耗、电源电压 输入电压范围 最大电压摆幅(无失真放大范围) 输入/输出电阻 信噪比(S/N) 以上特性大部分互相制约,要根据实际应用 场合进行折衷选择或优化设计。

2 2 gs th ds 2 2 2 2 ds 2

I I

OUT

REF

W /L 1 V ( )( ) W /L 1 V

1 1 ds 1

由于Vds2一般不等于Vds1,输出电流出现偏差。且λ愈大,电流误差愈

大。因此为了提高电流源的精度,通常使用L尺寸较大的管子形成电流

镜(λ∝1/L)。为了进一步减小沟道长度调制的影响,可采用后面介绍 的共源共栅电流镜。

2)较大的Rs将占用较大的芯片面积及功耗。

26

源极跟随器的大信号特性

VDD D M1 VDD

Vout

VDD-VTH1

Ibias

Vin

S

Vout

Vin

M3

M2

0

VTH1

VDD

1) 当Vin<VTH1时,M1处于截止区,ID1=0,M2处于深度线性区,Vout=0。 2) 当Vin>VTH1时,M1和M2都进入饱和区,由于电流镜的作用,漏极电流基本保 持恒定。如果忽略M1的沟道长度调制效应和体效应(VTH1随Vout变化),则 M1的漏极电流可表示为 1 W 2 I D1 nCox 1 Vin Vout VTH 1 2 L1 Vout随Vin线性增加,但其差值始终保持为VTH1+Veff1。因此,源极跟随器的输 入和输出电压之间产生直流电平位移,其位移幅度为VTH1 +Veff1。由于 Vin<VDD(最大工作电压),M1始终工作在饱和区,不会进入线性区。

25

3.3 共漏极放大器(源极跟随器/Source follower)

Drain端交流接地

VDD

VDD D M1 S

VDD

M1

I bias

V in

Vin Vout Rs

NMOS放大管

电阻负载的缺点:

M3 M2

V out A ctive L oad

1)M1的漏极电流受输入直流电平的强烈影响→导致AMP的输入-输 出特性严重非线性;

VDD

0

VDD/2

Vin

M1和M2均工作在饱和区时的电压放大倍数(NMOS与PMOS同时 起放大作用): 较单级NMOS或PMOS共源放大器增益大

A ( g g )( r // r )

v m1 m2 ds 1 ds 2

如果将放大器的静态工作点设置在Vin=Vdd/2,则可获得最大电压 增益和输出动态范围。例如用在A/D变换的比较器中(将输入和输出 瞬间短路使Vin=Vdd/2)。

负载电阻: r L2 , ds 2

ID

L2 rds 2 Av

| Vds 2 |min 输出电压摆幅

(在偏置电流ID和W2不变的情况下,L2 ↑→|Vgs2-Vth2| ↑→ |Vds2| min↑) 结论: 在ID确定的情况下,适当增加管子的尺寸(保持宽长比不 变),可提高电压增益。缺点是寄生电容增大,频率特性变差。

21

电压放大倍数(工作在饱和区)

本征增益: A g .r 2u c W1 I ( 1 ) W1L1 v m1 ds1 n ox D

0

L1

1I D

ID

W1 L1 ID

Av0

但是,W1L1↑→Cgs1 ↑→频率特性变差。为了提高放大倍数,可适当 减小偏置电流ID(受到放大器的速度和噪声要求的限制)。

19

电流镜作为有源负载时的放大原理

Id

有源负载为恒流源 Rds2=∞

ID

∆Vin

∆Vout

Q

∆Vout

Vds

有源负载的输出 电阻不为无穷大 Rds2≠∞

有源负载的输出电阻不为无穷大时,电压放大倍数减小。

20

电压放大倍数(工作在饱和区)

rin Vout + _ + Vgs1 _

Vin

gm1Vgs1

I d n C OX

W (Vgs Vth )Vds L

17

输出电压的摆幅

Vout 截止区(M1) VDD 饱和区(M1)

线性区(M1)

0

VTH1 Vout+VTH1

Vin

为了保证M1与M2均工作在饱和区,输出电压被限制在以下范围: (Vin-Vth1)<Vout<VDD-|Vds2|min

22

电阻负载与电流镜有源负载的比较

Id

电阻的负载线

饱和区

Vin Active load的负载线

线性区

Vdd*

Vdd

电流镜有源负载的等效电阻随Vin变化:

Vds

Vdd * RL I ds 500k 100uA 50V

线性区(小电阻)

饱和区(大电阻)

23

反相器放大器(推挽放大器)

线性放大区域

5

基本电流镜的误差(其它原因引起)

M1与M2的Vth不同(例如栅氧化膜的厚度不同)

M1与M2的尺寸误差(几何失配)

提高电流源精度的措施:

1)在电流镜的版图设计中,M1与M2的结构应尽可能保持对称且紧靠在一起 配置,保证较小的Vth偏差。 2)可将管子的W和L取大一些,以减小尺寸失配误差的影响。 3)在CMOS制造过程中存在源/漏区的横向扩散现象,即 Leff =Ldrawn-2LD,由于源/漏区的横向扩散长度LD是与工艺相关的某一常 数,与栅长Ldrawn无关,因此,如果将Ldrawn加倍,但Leff并不能相应加

9

基本电流镜的小信号等效电路(NMOS)

M1 M2

ix

+

1/gm1

Vgs2

_

+

gm2vgs2

rds2

_

Vx

rout = rds2

V1

i1

i1 1/gm1

+

Vgs1

_

rds1 gm1vgs1