数字电路题库--周静

数字电路技术考试题

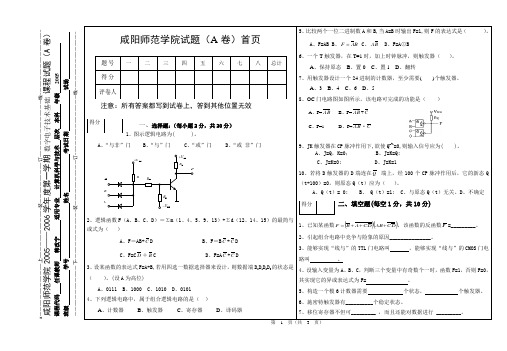

a ----------------------上---------------------装-----------------订------------------------线--------------------------咸阳师范学院2005——2006学年度第一学期 数字电子技术基础 课程试题(A 卷)课程代码 任课教师 韩改宁 适用专业 计算机科学与技术 层次 本科 年级 2005班级 学号 姓名 考试日期 试场---------------------下---------------------装-------------------订-------------------------线------------------------第 1 页(共 3 页)----------------------上---------------------装-----------------订------------------------线---------------------------咸阳师范学院2005——2006学年度第一学期 数字电子技术基础 课程试题(A 卷)课程代码 任课教师 韩改宁 适用专业 计算机科学与技术 层次 本科 年级 2005班级 学号姓名 考试日期 试场---------------------下---------------------装-------------------订-------------------------线------------------------第 2 页(共 3 页)----------------------上---------------------装-----------------订------------------------线---------------------------咸阳师范学院2005——2006学年度第一学期 数字电子技术基础 课程试题(A 卷课程代码 任课教师 韩改宁 适用专业 计算机科学与技术 层次 本科 年级 2005班级 学号 姓名 考试日期 试场---------------------下---------------------装-------------------订-------------------------线------------------------第 3 页(共 3 页)咸阳师范学院2005—2006 学年度第二学期计算机科学与技术专业(本)2005 级数字电子技术基础课程试题参考答案及评分标准第 1 页(共 3 页)第 2 页(共 3 页)第 3 页(共 3 页)。

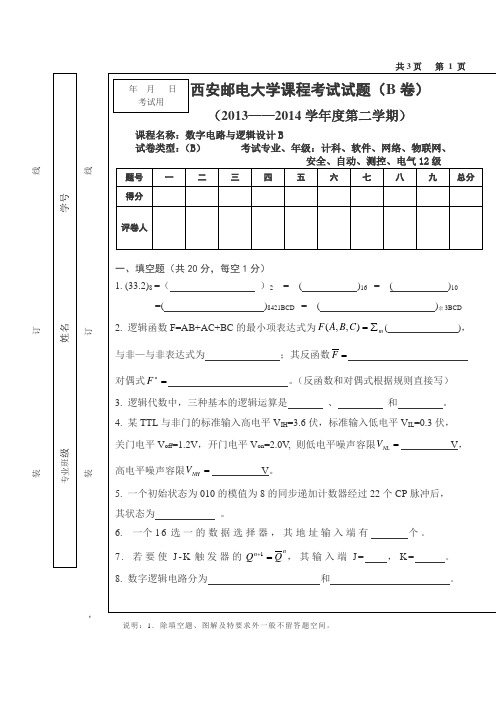

数字电路与逻辑设计B试题B卷

A. 4

B. 8

C. 32

D. 12

4. 电路如图 2 所示,74283 为四位二进制全加器,管脚 A4A3 A2 A1、B4B3 B2 B1 B0

分别为被加数、加数,管脚 SUM4 SUM3 SUM2 SUM1 为本位和,管脚 CIN 为低位

向本位的进位,管脚 COUT 为本位向高位的进位,外接信号 M。分析电路,下列

------------------------------------------------装----------------------------------------------订----------------------------------------------------线---------------------------- -----

Y5

1 0 000 11111110

Y4

1 0 001 11111101

1 0 010 11111011

Y3

1 0 011 1 1 11 0 1 1 1

Y2

1 0 100 11101111

Y1

1 0 101 11011111

Y0

1 0 110 10111111

1 0 111 01111111

四选一数据选择器逻辑符号及功能表

B. 不可以自启动的环形计数器

C. 可以自启动的扭环形计数器

D. 不可以自启动的扭环形计数器

1 0

CP

CLR S1 S0 SR A B C D SL CLK

QA 1

QB QC QD

74194功能表

输入

输出

CLR S1 S0 SR SL CLK QA QB QC QD 0 XXXX X 0 0 0 0

数字电子技术基础_青岛大学中国大学mooc课后章节答案期末考试题库2023年

数字电子技术基础_青岛大学中国大学mooc课后章节答案期末考试题库2023年1.555定时器可以搭成任意频率的多谐振荡电路。

答案:错误2.D/A转换器的位数越多,能够分辨的最小输出电压变化量就越小。

答案:正确3.D/A转换器是将模拟量转换成数字量。

答案:错误4.在verilogHDL语言中,关键字全是小写。

答案:正确5.保险库有一把锁,A、B两位经理各有一把钥匙,必须两位经理同时在才能打开锁,用F表示代开保险库锁的状态,则F=(A+B)'。

答案:错误6.TTL与非门多余的输入端应接高电平。

答案:正确7.驱动共阳极七段数码管的译码器的输出电平为高电平有效。

答案:错误8.消除竞争冒险现象的方法有多种,其中最易操作的是修改电路的逻辑表达式。

答案:错误9.逻辑函数通常有真值表、逻辑表达式、逻辑电路图、卡诺图等描述形式,这些形式之间不能相互转换。

答案:错误10.D/A转换器产生转换误差的原因有()。

答案:运算放大器的零点漂移_电阻网络中电阻阻值的偏差_参考电压的波动_模拟开关导通内阻和导通压降的差异11.函数F=AB+BC,使F=1的输入ABC的取值组合为()。

答案:11012.逻辑函数Y = AC + BC'的最小项和的形式是()。

答案:Y=∑m(2 ,5 ,6 ,7)13.逻辑函数Y(A,B,C)=∑m(1,5,7)的的最大项积的形式是()。

答案:Y=∏M(0,2,3,4,6)14.逻辑代数中常量 0 和 1 是互反的。

答案:正确15.摩根定理又称反演律,常用的两个变形公式是:(AB)'=A'+B',(A+B)'=A'B'。

答案:正确16.若两个函数具有不同的逻辑表达式,则两个逻辑函数必然不相等。

答案:错误17.已知逻辑表达式AB+C=AB+D,则可得C=D。

答案:错误18.一个两输入端的门电路,当输入为0和1时,输出不是1的门是()。

答案:与门19.时序逻辑电路的特点是:电路任一时刻的输出状态与同一时刻的输入信号有关,与原有状态没有任何的联系。

浙江大学2003级数字电路期末考试卷

浙江大学2005–2006学年秋冬季学期《数字系统设计基础》课程期末考试试卷开课学院: 信息学院 ,考试形式:闭卷,允许带___________入场 考试时间:_2006_年_1_月_14_日,所需时间: 120 分钟考生姓名: _____学号: 专业: ________一、(10分)把下列逻辑表达式化简为最简形式(不考虑冒险)。

(1) ,,,1Y (A B C D)=A B CD+A(B+C )(B+D )+A+C+D(2))10,8,4,0(d )13,12,7,5,3,2(M )D ,C ,B ,A (Y 2∏•∏= 其中d 表示任意项。

二、(本题共15分,其中第1、2小题6分,其中第3小题3分)设计一个一位8421BCD码乘以5的电路,要求输出也为8421BCD码,写出设计过程,画出电路。

1.用4线-16线译码器及门电路实现此电路(只画出十位的BCD码电路即可);2.只用四位全加器实现此电路;果也可用二进制表示。

3.不用任何器件设计此电路,请写出设计过程,画出电路。

三、(7分)P(P2P1P0)、Q(Q2Q1Q0)为二个三位无符号二进制数,试用一个3线-8线译码器74138和一个8选1数据选择器74151和尽可能少的门电路设计如下组合电路:当P=Q时,电路输出Y=1;否则,Y=0。

四、(12 分)以一个计数器74161为核心器件和少量门电路,设计一个带同步清0功能的5421BCD码计数器:电路有清0输入控制端R,当R=0时,同步清0;当R=1时,按5421BCD码规则同步计数,注意不能有过渡态。

5421BCD码编码规则:0~9分别为:0000、0001、0010、0011、0100、1000、1001、1010、1011、1100。

请写出设计过程。

五、(15分)试用JK触发器及与非门设计一个具有异步清零功能的2421BCD码十进制同步计数器,不要求自启动分析。

2421BCD码如下表所示:六、分析题(本题共16分,每小题8分)1、分析由移位计数器74194组成的时序,画出电路状态图?(排列次序:Q0Q1Q2Q3,另外S1 S0=00,保持;S1 S0=01,右移;S1 S0=10,左移;S1 S0=11,置数。

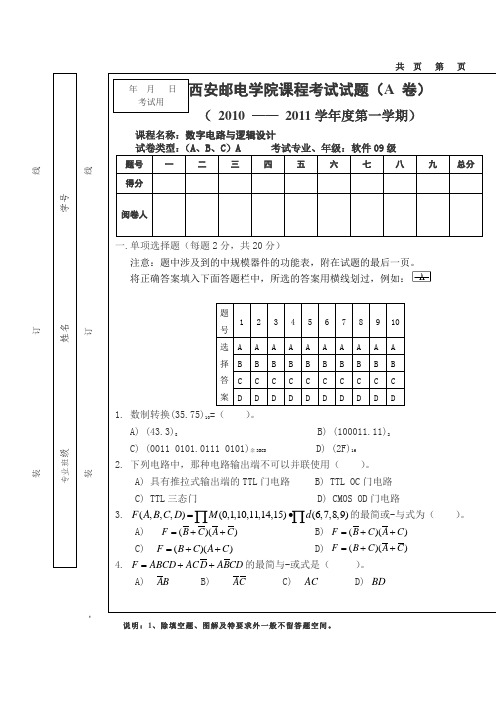

2010数字电路与逻辑设计(48学时)A卷及答案

共 页 第 页说明:1、除填空题、图解及特要求外一般不留答题空间。

------------------------------------------------装----------------------------------------------订----------------------------------------------------线---------------------------- ----- -------------------------------------------------装----------------------------------------------订----------------------------------------------------线---------------------------- -----注意:题中涉及到的中规模器件的功能表,附在试题的最后一页。

将正确答案填入下面答题栏中,所选的答案用横线划过,例如:图1.1图1.22.装订试卷,考生答卷时不得拆开或在框外留写标记,否则按零分计共 页 第 页说明:1、除填空题、图解及特要求外一般不留答题空间。

------------------------------------------------装----------------------------------------------订----------------------------------------------------线---------------------------- ----- -------------------------------------------------装----------------------------------------------订----------------------------------------------------线---------------------------- -----图2.22.装订试卷,考生答卷时不得拆开或在框外留写标记,否则安零分计。

数字电子技术模拟试题

泰山学院课程考试专用泰山学院物理与电子科学系XXXX 级电子信息科学与技术本科专业《数字电子技术》模拟试题试卷共8页,答题时间120分钟题号一二三四五总分统分人复核人得分一、选择填空(共 30 分,每题 3 分,把答案填在下面的表格里1. 引起组合逻辑电路中竟争与冒险的原因是(A 、逻辑关系错;B 、干扰信号;C 、电路延时;D 、电源不稳定。

2. 组合逻辑电路通常由( 组合而成。

A. 门电路B. 触发器C. 计数器D. 寄存器 3. 指出下列各式中哪个是四变量A、B、C、D的最小项(A 、ABC ;B 、A+B+C+D ;C 、ABCD ; D 、A+B+D 4. 8—3线优先编码器(74LS148中,8条输入线0I ~7I同时有效时,优先级最高为I 7线,则2Y 1Y 0Y 输出线的性质是(A. 000B. 010C. 101D. 111 5. 七段显示译码器是指( 的电路。

A. 将二进制代码转换成0~9数字B. 将BCD 码转换成七段显示字形信号得分阅卷人题号 1 2 3 4 5 6 7 8 9 10 答案C. 将0~9数字转换成BCD 码D. 将七段显示字形信号转换成BCD 码 6. 逻辑数F=A C +A B +BC ,当变量的取值为( 时,将出现冒险现象。

A. B=C=1 B. B=C=0 C. A=1,C=0 D. A=0,B=0 7. 时序逻辑电路中一定是含(A. 触发器B. 组合逻辑电路C. 移位寄存器D. 译码器 8. 为实现将D 触发器转换为T 触发器,图1的虚框内应是(A. 或非门B. 与非门C. 异或门D. 同或门9.用几个触发器构成计数器,可得到最大计数长度是(A. nB. 2n C . 2n D. 2n-1 10. 用55S 定时器构成单稳态触发器其输出脉宽为( A 、0.7RC ;B 、1.1RC ; C 、1.4RC ;D 、1.8RC ;二、填空题(本大题共15 分,每空 1 分1、若各门电路的输入均为A和B ,且A=0,B=1;则与门的输出为_________,或门的输出为 ,异或门的输出为。

数模、模数转换电路的综合实验研究

2010年8月第16卷第3期安庆师范学院学报(自然科学版)J o urnal of A nqi ng T each er s C ol lege(N at u r al Sci ence Edi ti on)A ug.2010V oI.16№.3数模、模数转换电路的综合实验研究周静,刘杰(阜阳师范学院物理与电子科学学院,安徽阜阳236041)摘要:针对高校普遍单独开设A/D转换实验和D/A转换实验的现象,提出了一个集数模转换和模数转换为一体的综合数字电路实验。

实际操作,实验结果分析,以及实验效果表明该方案改变了传统单一实验的验证性,不仅可以巩固学生的基础知识,还能够提高学生的学习兴趣和综合应用能力,达到了解知识体系和学以致用的目的。

关键词:数字电路;数模转换器;模数转换器中圈分类号:TN79+2文献标识码:A文章编号:1007--4260(2010)03--0115--040引言随着数字技术,特别是计算机技术的飞速发展与普及,在现代控制、通信及检测等领域中,为提高系统的性能指标,对信号的处理已广泛采用了数字计算机技术。

由于实际处理对象往往都是一些模拟量(如温度、压力、位移、图素等),要使计算机或数字仪表能够识别、处理这些信号,必须首先将这些模拟信号转换成数字信号,而后经过分析、处理,最后再将这些数字量的结果转换成模拟量,以便驱动执行机构。

因此,在模拟信号和数字信号之间就需要一种能起桥梁作用的电路——模数转换器和数模转换器。

这两种转换器是数字电路的基础知识[1’2],也是计算机接口技术的主要章节[3],因此这两种转换器实验也就成为一门重要的实验内容。

然而,由于传统的因事就简和就事论事的观念,电路实验总是以特定的目的、孤立的功能单元而开设,致使很多学生在完成了电路实验后感到知识不连贯,理论与实践脱节,实验如同验证,不能综合理解和运用数字电路的知识体系,以至于很难达到融会贯通,学以致用的目的。

针对传统电路实验中存在的这种问题,一种综合性数字电路实验设计成为了理想的研究课题,并成为了当前的研究热点l-4_9]。

最新07自考模拟电路与数字电路试题合集

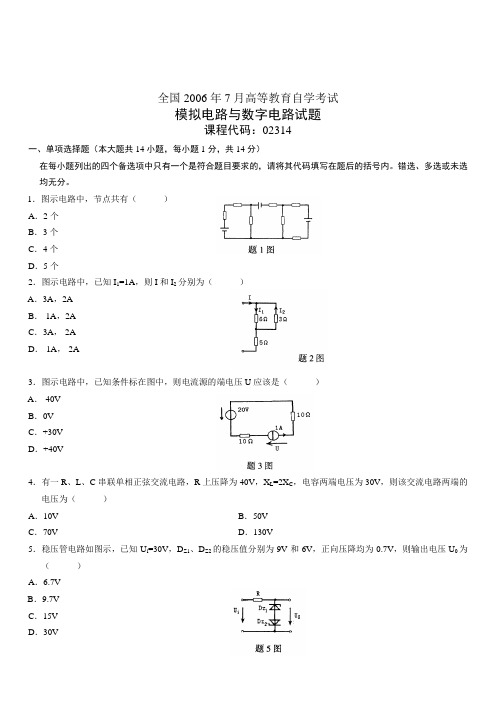

全国2006年7月高等教育自学考试模拟电路与数字电路试题课程代码:02314一、单项选择题(本大题共14小题,每小题1分,共14分)在每小题列出的四个备选项中只有一个是符合题目要求的,请将其代码填写在题后的括号内。

错选、多选或未选均无分。

1.图示电路中,节点共有()A.2个B.3个C.4个D.5个2.图示电路中,已知I1=1A,则I和I2分别为()A.3A,2AB.-1A,2AC.3A,-2AD.-1A,-2A3.图示电路中,已知条件标在图中,则电流源的端电压U应该是()A.-40VB.0VC.+30VD.+40V4.有一R、L、C串联单相正弦交流电路,R上压降为40V,X L=2X C,电容两端电压为30V,则该交流电路两端的电压为()A.10V B.50VC.70V D.130V5.稳压管电路如图示,已知U i=30V,D Z1、D Z2的稳压值分别为9V和6V,正向压降均为0.7V,则输出电压U0为()A.6.7VB.9.7VC.15VD.30V6.设计一个输入电阻高、输出电阻低、放大倍数大于1的三级放大器,满足上述要求的连接框图应选( )7.已知信号源为高内阻的电流源,为了充分发挥放大器的负反馈作用,且要求提高放大器输出电压的稳定性,宜采用的负反馈措施为( ) A .电压串联负反馈 B .电流串联负反馈 C .电流并联负反馈D .电压并联负反馈8.在桥式全波整流电路中,变压器副边电压为U 2,负载电阻R L ,则输出的直流电压U 0和每个二极管的平均电流I D分别为( ) A .U 0=0.45U 2,I D =0.45L2R U B .U 0=0.45U 2,I D =0.9L 2R U C .U 0=0.9U 2,I D =0.45L2R U D .U 0=0.9U 2,I D =0.9L2R U 9.将十六进制数(4E.C )16转换成十进制数是( ) A .(54.12)10 B .(54.75)10 C .(78.12)10D .(78.75)1010.正逻辑的或非门电路,也等效于负逻辑的( ) A .或门电路 B .与门电路 C .或非门电路D .与非门电路11.图示TTL 门电路中,能完成F=A 的是图( )12.对于RS 触发器,希望每来一个CP 脉冲翻转一次,即特征方程为Q n+1=n Q ,正确的接法是( ) A .S=Q n R= Q nB .S=n Q R= Q nC.S=Q n R=nQ R=nQQ D.S=n13.容量为8K×8位的RAM芯片,其地址线和数据线各为()A.8和8根B.10和8根C.13和8根D.8和13根14.单稳态触发器有()A.两个稳定状态B.一个稳定状态,一个暂稳态C.两个暂稳态D.记忆二进制数的功能二、填空题(本大题共14小题,每小题1分,共14分)请在每小题的空格中填上正确答案。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第一章 数字逻辑电路基础一、填空题1、模拟信号的特点是在 和 上都是 变化的。

2、数字信号的特点是在 和 上都是 变化的。

3、数字电路主要研究 与 信号之间的对应 关系。

4、用二进制数表示文字、符号等信息的过程称为_____________。

5、()11011(2= 10),()1110110(2= 8),()21(10= 2)。

6、()101010(2= 10),()74(8= 2),()7(16=D 2)。

7、最基本的三种逻辑运算是 、 、 。

8、逻辑等式三个规则分别是 、 、 。

9、逻辑函数化简的方法主要有 化简法和 化简法。

10、逻辑函数常用的表示方法有 、 和 。

11、任何一个逻辑函数的 是唯一的,但是它的 可有不同的形式,逻辑函数的各种表示方法在本质上是 的,可以互换。

12、写出下面逻辑图所表示的逻辑函数Y= 。

13、写出下面逻辑图所表示的逻辑函数Y= 。

14、半导体二极管具有 性,可作为开关元件。

15、半导体二极管 时,相当于短路; 时,相当于开路。

16、半导体三极管作为开关元件时工作在 状态和 状态。

17、在逻辑门电路中,最基本的逻辑门是 、 和 。

18、与门电路和或门电路具有 个输入端和 个输出端。

19、非门电路是 端输入、 端输出的电路。

20、三态门除了高电平、低电平两个状态外,还有第三个状态,这第三个状态常称为 。

21、根据逻辑功能的不同特点,逻辑电路可分为两大类: 和 。

22、组合逻辑电路主要是由 、 和 三种基本逻辑门电路构成的。

23、触发器具有 个稳定状态,在输入信号消失后,它能保持 。

24、同步D 触发器的特性方程为 。

25、主从触发器是一种能防止 现象的触发器。

26、在CP 脉冲和输入信号作用下,JK 触发器能够具有 、 、 、和 的逻辑功能。

27、在CP 脉冲有效期间,D 触发器的次态方程1+n Q = ,JK 触发器的次态方程1+n Q = 。

28、对于JK 触发器,当CP 脉冲有效期间,若J=K=0时,触发器状态 ;若K J =时,触发器 或 ;若J=K=1时,触发器状态 。

29、同步触发器属 触发的触发器;主从触发器属 触发的触发器。

30、边沿触发器是一种能防止 现象的触发器。

31、与主从触发器相比, 触发器的抗干扰能力较强。

32、对于JK 触发器,若J=K ,则可完成 触发器的逻辑功能。

33、对于JK 触发器,若K J =,则可完成 触发器的逻辑功能。

34、将D 触发器的D 端与Q 端直接相连时,D 触发器可转换成 触发器。

35、时序逻辑电路任何时刻的输出信号不仅取决于 ,而且还取决于 。

36、时序逻辑电路逻辑功能的表示方法有 、 、 、和 四种。

37、进行时序逻辑电路的分析时,需要列出逻辑电路的一些方程式,这些方程式包括 、 、 和 。

38、用来记忆和统计输入CP 脉冲个数的电路,称为 。

39、用以存放二进制代码的电路称为 。

40、具有存放数码和使数码逐位右移或左移的电路称为 。

二、判断题1、十进制数74转换为8421BCD 码应当是BCD 8421)01110100(。

()2、二进制只可以用来表示数字,不可以用来表示文字和符号等。

()3、十进制转换为二进制的时候,整数部分和小数部分都要采用除2取余法。

()4、若两个函数相等,则它们的真值表一定相同;反之,若两个函数的真值表完全相同,则这两个函数未必相等。

()5、证明两个函数是否相等,只要比较它们的真值表是否相同即可。

()6、在逻辑函数表达式中,如果一个乘积项包含的输入变量最少,那么该乘积项叫做最小项。

()7、当决定一件事情的所有条件全部具备时,这件事情才发生,这样的逻辑关系称为非。

()8、在全部输入是“0”的情况下,函数B A Y +=运算的结果是逻辑“0”。

( )9、逻辑变量取值的0和1表示事物相互独立而又联系的两个方面。

()10、在变量A 、B 取值相异时,其逻辑函数值为1,相同时为0,称为异或运算。

()11、与门、或门和非门都具有多个输入端和一个输出端。

()12、在与门电路后面加上非门,就构成了与非门电路。

()13、时序逻辑电路的特点是在任何时刻的输出不仅和输入有关,而且还取决于电路原来的状态。

()14、时序逻辑电路由存储电路和触发器两部分组成。

()15、为了记忆电路的状态,时序电路必须包含存储电路,存储电路通常以触发器为基本单元电路组成。

()三、选择题1、下列哪些信号属于数字信号()。

A 、正弦波信号B 、时钟脉冲信号C 、音频信号D 、视频图像信号2、数字电路中的三极管工作在()。

A 、饱和区B 、截止区C 、饱和区或截止区D 、放大区3、十进制整数转换为二进制数一般采用()A 、除2取余法B 、除2取整法C 、除10取余法D 、除10取整法4、将十进制小数转换为二进制数一般采用()A 、乘2取余法B 、乘2取整法C 、乘10取余法D 、乘10取整法5、在()的情况下,函数B A Y +=运算的结果是逻辑“0”A 、全部输入是“0”B 、任一输入是“0”C 、任一输入是“1”D 、全部输入是“1”6、在()的情况下,函数AB Y =运算的结果是逻辑“1”A 、全部输入是“0”B 、任一输入是“0”C 、任一输入是“1”D 、全部输入是“1”7、在()的情况下,函数AB Y =运算的结果是逻辑“1”A 、全部输入是“0”B 、任一输入是“0”C 、任一输入是“1”D 、全部输入是“1”8、逻辑表达式=+BC A ()A 、AB B 、C A + C 、))((C A B A ++D 、C B +9、逻辑表达式ABC =()A 、CB A ++ B 、C B A ++ C 、C B A ++D 、C B A ∙∙10、下列逻辑式中,正确的是()A 、A A A =+B 、0=+A AC 、1=+A AD 、1=∙A A11、下列逻辑式中,正确的是()A 、0=∙A AB 、1=∙A AC 、0=∙A AD 、0=+A A12、逻辑函数式AB B A B A ++,化简后结果是()A 、AB B 、B A B A +C 、B A +D 、AB B A +13、全部的最小项之和恒为()A 、0B 、1C 、0或1D 、非0非114、对于四变量逻辑函数,最小项有()个A 、0B 、1C 、4D 、1615、正逻辑是指()A 、高电平用“1”表示B 、低电平用“0”表示C 、高电平用“1”表示,低电平用“0”表示D 、高电平用“0”表示,低电平用“1”表示16、对于触发器和组合逻辑电路,以下()的说法是正确的。

A 、两者都有记忆能力B 、两者都无记忆能力C 、只有组合逻辑电路有记忆能力D 、只有触发器有记忆能力17、为避免一次翻转现象,应采用()触发器。

A 、高电平B 、低电平C 、主从D 、边沿器18、仅具有“保持”“翻转”功能的触发器叫()。

A 、JK 触发器B 、RS 触发器C 、D 触发器 D 、T 触发19、时序逻辑电路中一定包含()A 、触发器B 、编码器C 、移位寄存器D 、译码器20、时序电路某一时刻的输出状态,与该时刻之前的输入信号()A 、有关B 、无关C 、有时有关,有时无关D 、以上都不对21、用n 个触发器构成计数器,可得到的最大计数长度为()A 、nB 、n 2C 、2nD 、n 222、同步时序逻辑电路和异步时序逻辑电路比较,其差异在于后者()A 、没有触发器B 、没有统一的时钟脉冲控制C 、没有稳定状态D 、输出只与内部状态有关四、简答题1、数制转换(要求写出必要的计算过程)2(10011011)(= 8)(= 16)2、数制转换(要求写出必要的计算过程)16()(AE = 2)(= 8)3、数制转换(要求写出必要的计算过程)(1)()125(10= 2) (2)()375.13(10= 2)4、应用逻辑代数运算法则证明下列各式:(1)AB B A B A AB +=+ (2)B B C B B B A A =++++)()(5、化简逻辑表达式:(1))(A BC AB Y += (2)))()((C C B C B B C B A Y ++++++=6、把下面各逻辑函数写成最小项表达式。

(1)AC C B B A Y ++= (2)B C B A Y +=7、画出逻辑函数B A B A L ⋅+⋅=的逻辑图。

8、¡Ý1LC BA L 写出如图所示逻辑图的函数表达式。

9、已知主从JK 触发器J 、K 的波形如图所示,画出输出Q 的波形图(设初始状态为0)。

10、画出用JK 触发器实现n n Q Q =+1的逻辑图。

五、分析计算题1、分别采用公式法及卡诺图法化简下列逻辑表达式,并列出真值表。

BC A C B A C B A C B A C B A Y ++++= 2、组合电路如图所示,分析该电路的逻辑功能。

CP J K 1234563、分析如图所示的组合逻辑电路的功能。

4、设计一个楼上、楼下开关的控制逻辑电路来控制楼梯上的路灯,要求:使之在上楼前,用楼下开关打开电灯,上楼后,用楼上开关关灭电灯;或者在下楼前,用楼上开关打开电灯,下楼后,用楼下开关关灭电灯。

5、用与非门设计一个举重裁判表决电路,要求:(1)设举重比赛有3个裁判,一个主裁判和两个副裁判。

(2)杠铃完全举上的裁决由每一个裁判按一下自己面前的按钮来确定。

(3)只有当两个或两个以上裁判判明成功,并且其中有一个为主裁判时,表明成功的灯才亮。

6、某设备有开关A 、B 、C ,要求:只有开关A 接通的条件下,开关B 才能接通;开关C 只有在开关 B 接通的条件下才能接通。

违反这一规程,则发出报警信号。

设计一个由与非门组成的能实现这一功能的报警控制电路。

7、设有甲乙丙三人进行表决,若有两人以上(包括两人)同意,则通过表决,用ABC 代表甲乙丙,用L 表示表决结果。

试写出真值表,逻辑表达式,并画出用与非门构成的逻辑图。

8、用74LS138实现逻辑函数F=∑(1,2,4,7)。

9、用全译码器74LS138实现逻辑函数ABC C B A C B A C B A f +++=10、用八选一数据选择器74LS151实现下列逻辑函数:ABC C AB C B A BC A L +++=11、分析图示时序逻辑电路。

12、用JK触发器设计一个4位二进制异步加法计数器13、用74LS161构成十进制计数器。