无线通信与网络实验报告

无线传感网络实验报告

《无线传感网络技术与应用》实验报告目录一、研究背景 (1)二、研究内容 (1)三、传感器原理介绍 (1)(一)MQ-2 气体传感器简介 (1)(二)声音检测传感器简介 (2)(三)声光报警器原理 (3)(一)烟雾传感器模块 (4)(二)声音检测传感器模块 (5)(三)声光报警器模块 (7)(四)协调器与终端模块 (8)五、实验分析 (9)(一)烟雾传感器数据分析 (9)(二)声音检测传感器模块数据分析 (9)(三)声光报警检测传感器模块数据分析 (10)六、实验中出现的问题 (11)(一)打开文件存在缺失 (11)(二)串口无法识别 (11)(三)安装stm8或stem32时无法打开文件 (11)(四)做数据透传模型实验时无法通信 (11)七、实验总结 (11)一、研究背景近几年,随着我国经济的不断发展和构建和谐社会理念的提出,特别是重大工程对安防行业的刺激和需求,安防行业面临着前所未有的发展机遇。

结合当前先进技术提高安全防范系统性能,成为当前安防发展的一个重要课题。

在分析了无线传感网络在国内外安防系统应用现状的基础上,针对安防系统存在的问题,提出一种基于无线传感网络的智能安防系统设计方案。

与传统安防系统相比,具有免布线、费用低、布置方便等优点。

在综合考虑了当前流行的无线通信技术后,选择具有数据吞吐量小、低功耗、网络容量大等优点的ZigBee 技术作为构建智能安防无线通信网络的关键技术。

可以预计,ZigBee 技术将在家庭智能化、安防行业、工业控制等领域获得广泛应用。

二、研究内容本次课题研究涉及到三个传感器,分别是烟雾传感器、声音检测传感器、声光报警传感器,通过相关程序的烧写到实验板上,根据每个传感器的特点对每个传感器进行测试,通过观察串口终端的数字变化,检查外部环境的变化是否有数据变化。

最后根据实验现象进行总结分析。

三、传感器原理介绍(一)MQ-2 气体传感器简介MQ-2 气体传感器所使用的气敏材料是在清洁空气中电导率较低的二氧化锡(SnO2)。

北京理工大学微波实验报告——无线通信系统

实验一无线通信系统(图像传输)实验一、实验目的1、掌握无线通信(图像传输)收发系统的工作原理;2、了解各电路模块在系统中的作用。

二、实验内容a)测试发射机的工作状态;b)测试接收机的工作状态;c)测试图像传输系统的工作状态;d)通过改变系统内部连接方式造成对图像信号质量的影响来了解各电路模块的作用。

三、无线图像传输系统的基本工作原理发射设备和接收设备是通信设备的重要组成部分。

其作用是将已调波经过某些处理(如放大、变频)之后,送给天馈系统,发向对方或转发中继站;接收系统再将空间传播的信号通过天线接收进来,经过某些处理(如放大、变频)之后,送到后级进行解调、编码等。

还原出基带信息送给用户终端。

为了使发射系统和接收系统同时工作,并且了解各电路模块在系统中的作用,通过实验箱中的天线模块和摄像头及显示器,使得发射和接收系统自闭环,通过图像质量来验证通信系统的工作状态,及各个电路模块的作用和连接变化时对通信或图像质量的影响。

以原理框图为例,简单介绍一下各部分的功能与作用。

摄像头采集的信号送入调制器进频率调制,再经过一次变频后、滤波(滤去变频产生的谐波、杂波等)、放大、通过天线发射出去。

经过空间传播,接收天线将信号接收进来,再经过低噪声放大、滤波(滤去空间同时接收到的其它杂波)、下变频到480MHz,再经中频滤波,滤去谐波和杂波、经视频解调器,解调后输出到显示器还原图像信号。

四、实验仪器信号源、频谱分析仪等。

五.测试方法与实验步骤(一)发射机测试图1原理框图基带信号送入调制器,进行调制(调幅或调频等调制),调制后根据频率要求进行上变频,变换到所需微波频率,并应有一定带宽,然后功率放大,通过天线发射或其它方式传播。

每次变频后,会相应产生谐波和杂波,一般变频后加响应频段的滤波器,以滤除谐波和杂波。

保证发射信号的质量或频率稳定度。

另外调制器或变频器本振信号的稳定度也直接影响发射信号的好坏,因而,对本振信号的质量也有严格的要求。

无线局域网的实验报告

无线局域网的实验报告无线局域网的实验报告引言:无线局域网(Wireless Local Area Network,简称WLAN)是一种无线通信技术,通过无线信号传输数据,实现终端设备之间的互联和互通。

本实验旨在研究无线局域网的性能和应用,并通过实际操作和数据收集来评估其效果和可行性。

一、实验设备和环境本实验使用的设备包括一台无线路由器和多台无线终端设备。

实验环境为一个室内空间,包括有障碍物和无障碍物的区域,以模拟真实的使用场景。

二、实验步骤1. 设备设置将无线路由器连接到电源,并通过网线将其与宽带接入设备(如光纤猫)连接。

根据实验需要,设置无线网络名称(SSID)和密码,并选择适当的加密方式(如WPA2)。

2. 终端连接打开多台无线终端设备,搜索并选择目标无线网络。

输入正确的密码后,终端设备将成功连接到无线局域网。

3. 信号强度测试在不同位置放置终端设备,使用信号强度测试工具(如无线网络分析仪)测量信号强度。

记录不同位置的信号强度值,并分析其变化规律。

4. 速度测试使用速度测试工具(如Speedtest)测量无线局域网的上传和下载速度。

在不同位置和时间进行多次测试,并记录测试结果。

根据数据分析,评估无线局域网的传输速度和稳定性。

5. 干扰测试在实验环境中引入干扰源(如其他无线设备或电磁干扰源),观察无线局域网的表现。

记录干扰对信号强度和传输速度的影响,并提出改进方案。

6. 安全性测试使用网络安全工具(如Wireshark)监控无线局域网中的数据传输,分析是否存在未授权的访问或数据泄露风险。

根据测试结果,提出加强网络安全的建议。

三、实验结果与讨论1. 信号强度测试结果显示,在无障碍物的开放区域,信号强度较高且稳定。

而在有障碍物的区域,如墙壁或家具的遮挡下,信号强度明显下降。

因此,在设计无线局域网时,应合理规划设备的放置位置,避免信号受阻。

2. 速度测试结果显示,无线局域网的传输速度与终端设备的距离和网络负载有关。

通信LTE专业实训报告

成绩重庆邮电大学通信与信息工程学院移动通信综合实验报告专业通信工程班级学号姓名实习时间:年月重庆邮电大学通信与信息工程学院通信技术与网络实验中心制一、实验题目LTE无线侧综合实验二、实验目的1.熟悉LTE网络结构2.了解和学习华为eNodeB设备DBS3900系统功能3.掌握华为TDD-LTE的eNodeB数据配置方法4.获得通信网络工程的实际应用技能三、实验内容TD-LTE配置练习一:1、组网拓扑图2、MML命令脚本2.1基本数据2.1.1全局数据MOD ENODEB:ENODEBID=101, NAME="CYTX", ENBTYPE=DBS3900_LTE,LOCATION="CYYF", PROTOCOL=CPRI;ADD CNOPERATOR: CnOperatorId=1, CnOperatorName="CMCC", CnOperatorType=CNOPERATOR_PRIMARY, Mcc="460", Mnc="02";ADD CNOPERATORTA: TrackingAreaId=1, CnOperatorId=1, Tac=100;2.1.2设备数据ADD BRD: CN=0, SRN=0, SN=6, BT=UMPT;ADD BRD: CN=0, SRN=0, SN=2, BT=LBBP, WM=TDD;ADD BRD: CN=0, SRN=0, SN=16, BT=FAN;ADD BRD: CN=0, SRN=0, SN=18, BT=UPEU;ADD BRD: CN=0, SRN=0, SN=19, BT=UPEU;DSP BRD:;ADD RRUCHAIN: RCN=0, TT=CHAIN, AT=LOCALPORT, HCN=0, HSRN=0, HSN=2, HPN=0, CR=9.8;ADD RRU: CN=0, SRN=60, SN=0, TP=TRUNK, RCN=0, PS=0, RT=MRRU, RN="YFLRRU", ALMPROCSW=ON, ALMPROCTHRHLD=30, ALMTHRHLD=20, RS=TDL, RXNUM=1, TXNUM=1;2.1.3时钟数据ADD GPS: GN=0, CN=0, SRN=0, SN=6, CABLETYPE=COAXIAL, CABLE_LEN=20, MODE=GPS, PRI=4;SET CLKMODE: MODE=AUTO;SET CLKSYNCMODE: CLKSYNCMODE=TIME;频率同步(时钟同步,基本要求);时间同步(要求高,时间同步,频率一定同步)2.2传输数据2.2.1底层数据A、物理层ADD ETHPORT: CN=0, SRN=0, SN=6, SBT=BASE_BOARD, PN=0, PA=COPPER, MTU=1500, SPEED=100M, ARPPROXY=DISABLE, FC=CLOSE, FERAT=10, FERDT=8, DUPLEX=FULL;B、传输层ADD DEVIP: CN=0, SRN=0, SN=6, SBT=BASE_BOARD, PT=ETH, PN=0, IP="110.110.110.3", MASK="255.255.255.0";C、网络层ADD IPRT: CN=0, SRN=0, SN=6, SBT=BASE_BOARD, DSTIP="134.134.134.10", DSTMASK="255.255.255.0", RTTYPE=NEXTHOP, NEXTHOP="110.110.110.1", PREF=60, DESCRI="TO MME";ADD IPRT: CN=0, SRN=0, SN=6, SBT=BASE_BOARD, DSTIP="172.100.100.16", DSTMASK="255.255.255.0", RTTYPE=NEXTHOP, NEXTHOP="110.110.110.1", PREF=60, DESCRI="TO OMC";ADD IPRT: CN=0, SRN=0, SN=6, SBT=BASE_BOARD, DSTIP="135.135.135.10", DSTMASK="255.255.255.0", RTTYPE=NEXTHOP, NEXTHOP="110.110.110.1", PREF=60, DESCRI="TO SGW";D、数据链路层ADD VLANMAP: NEXTHOPIP="110.110.110.1", MASK="255.255.255.0", VLANMODE=SINGLEVLAN, VLANID=100, SETPRIO=DISABLE;2.2.2控制面ADD S1SIGIP: CN=0, SRN=0, SN=6, S1SIGIPID="TO MME", LOCIP="110.110.110.3", LOCIPSECFLAG=DISABLE, SECLOCIP="0.0.0.0", SECLOCIPSECFLAG=DISABLE, LOCPORT=3000, RTOMIN=1000, RTOMAX=3000, RTOINIT=1000, RTOALPHA=12, RTOBETA=25, HBINTER=5000, MAXASSOCRETR=10, MAXPATHRETR=5, CHKSUMTX=DISABLE, CHKSUMRX=DISABLE, CHKSUMTYPE=CRC32, SWITCHBACKFLAG=ENABLE, SWITCHBACKHBNUM=10, TSACK=200, CNOPERATORID=1;ADD MME: MMEID=0, FIRSTSIGIP="134.134.134.10", FIRSTIPSECFLAG=DISABLE, SECSIGIP="0.0.0.0", SECIPSECFLAG=DISABLE, LOCPORT=3000, CNOPERATORID=1, MMERELEASE=Release_R8;2.2.3用户面ADD S1SERVIP: CN=0, SRN=0, SN=6, S1SERVIPID="TO SGW", S1SERVIP="110.110.110.3", IPSECFLAG=DISABLE, PATHCHK=DISABLE, CNOPERATORID=1;ADD SGW: SGWID=0, SERVIP1="135.135.135.10", SERVIP1IPSECFLAG=DISABLE, SERVIP2="0.0.0.0", SERVIP2IPSECFLAG=DISABLE, SERVIP3="0.0.0.0", SERVIP3IPSECFLAG=DISABLE, SERVIP4="0.0.0.0", SERVIP4IPSECFLAG=DISABLE, CNOPERATORID=1;2.2.4维护面ADD OMCH: FLAG=MASTER, IP="110.110.110.3", MASK="255.255.255.0", PEERIP="172.100.100.16", PEERMASK="255.255.255.0", BEAR=IPV4, CN=0, SRN=0, SN=6, SBT=BASE_BOARD, BRT=NO;2.2.5无线数据ADD SECTOR: SECN=0, GCDF=DEG, LONGITUDE=0, LATITUDE=0, SECM=NormalMIMO, ANTM=1T1R, COMBM=COMBTYPE_SINGLE_RRU, SECTORNAME="SEC1", ALTITUDE=25, UNCERTSEMIMAJOR=3, UNCERTSEMIMINOR=3, ORIENTOFMAJORAXIS=0, UNCERTALTITUDE=3, CONFIDENCE=0, OMNIFLAG=FALSE, CN1=0, SRN1=60, SN1=0, PN1=R0A;ADD CELL: LocalCellId=0, CellName="CYTX_1", SectorId=0, CsgInd=BOOLEAN_FALSE, UlCyclicPrefix=NORMAL_CP, DlCyclicPrefix=NORMAL_CP, FreqBand=39, UlEarfcnCfgInd=NOT_CFG, DlEarfcn=38250, UlBandWidth=CELL_BW_N100, DlBandWidth=CELL_BW_N100, CellId=0, PhyCellId=99, AdditionalSpectrumEmission=1, FddTddInd=CELL_TDD, SubframeAssignment=SA2, SpecialSubframePatterns=SSP5, CellSpecificOffset=dB0, QoffsetFreq=dB0, RootSequenceIdx=1, HighSpeedFlag=LOW_SPEED, PreambleFmt=0, CellRadius=10000, CustomizedBandWidthCfgInd=NOT_CFG, EmergencyAreaIdCfgInd=NOT_CFG, UePowerMaxCfgInd=NOT_CFG, MultiRruCellFlag=BOOLEAN_FALSE, CPRICompression=NO_COMPRESSION;ADD CELLOP: LocalCellId=0, TrackingAreaId=1, CellReservedForOp=CELL_NOT_RESERVED_FOR_OP, OpUlRbUsedRatio=25, OpDlRbUsedRatio=25;ACT CELL: LocalCellId=0;TD-LTE配置练习二:1、组网拓扑图2、MML命令脚本2.1基本数据2.1.1全局数据MOD ENODEB:ENODEBID=101, NAME="CYZW", ENBTYPE=DBS3900_LTE, LOCATION="YF3L", PROTOCOL=CPRI;ADD CNOPERATOR: CnOperatorId=1, CnOperatorName="CYTX",CnOperatorType=CNOPERATOR_PRIMARY, Mcc="460", Mnc="04";ADD CNOPERATORTA: TrackingAreaId=0, CnOperatorId=1, Tac=123;2.1.2设备数据ADD BRD: CN=0, SRN=0, SN=6, BT=UMPT;ADD BRD: CN=0, SRN=0, SN=2, BT=LBBP, WM=TDD;ADD BRD: CN=0, SRN=0, SN=16, BT=FAN;ADD BRD: CN=0, SRN=0, SN=18, BT=UPEU;ADD BRD: CN=0, SRN=0, SN=19, BT=UPEU;DSP BRD:;ADD RRUCHAIN: RCN=0, TT=CHAIN, AT=LOCALPORT, HCN=0, HSRN=0, HSN=2, HPN=0, CR=9.8;ADD RRU: CN=0, SRN=60, SN=0, TP=TRUNK, RCN=0, PS=0, RT=MRRU, RN="YFLRRU", ALMPROCSW=ON, ALMPROCTHRHLD=30, ALMTHRHLD=20, RS=TDL, RXNUM=8, TXNUM=8;2.1.3时钟数据ADD GPS: GN=0, CN=0, SRN=0, SN=6, CABLETYPE=COAXIAL, CABLE_LEN=20, MODE=GPS, PRI=4;SET CLKMODE: MODE=AUTO;SET CLKSYNCMODE: CLKSYNCMODE=TIME;频率同步(时钟同步,基本要求);时间同步(要求高,时间同步,频率一定同步)2.2传输数据2.2.1底层数据A、物理层ADD ETHPORT: CN=0, SRN=0, SN=6, SBT=BASE_BOARD, PN=1, PA=FIBER, MTU=1500, SPEED=1000M,ARPPROXY=DISABLE, FC=CLOSE, FERAT=10, FERDT=8, DUPLEX=FULL;B、传输层ADD DEVIP: CN=0, SRN=0, SN=6, SBT=BASE_BOARD, PT=ETH, PN=1, IP="110.110.110.3", MASK="255.255.255.0";C、网络层ADD IPRT: CN=0, SRN=0, SN=6, SBT=BASE_BOARD, DSTIP="134.134.134.10", DSTMASK="255.255.255.0", RTTYPE=NEXTHOP, NEXTHOP="110.110.110.1", PREF=60, DESCRI="TO MME";ADD IPRT: CN=0, SRN=0, SN=6, SBT=BASE_BOARD, DSTIP="135.135.135.10", DSTMASK="255.255.255.0", RTTYPE=NEXTHOP, NEXTHOP="110.110.110.1", PREF=60, DESCRI="TO SGW";ADD IPRT: CN=0, SRN=0, SN=6, SBT=BASE_BOARD, DSTIP="172.100.100.16", DSTMASK="255.255.255.0", RTTYPE=NEXTHOP, NEXTHOP="110.110.110.1", PREF=60, DESCRI="TO OME";D、数据链路层ADD VLANMAP: NEXTHOPIP="110.110.110.1", MASK="255.255.255.0", VLANMODE=SINGLEVLAN, VLANID=1011, SETPRIO=DISABLE;2.2.2控制面ADD S1SIGIP: CN=0, SRN=0, SN=6, S1SIGIPID="TO MME", LOCIP="110.110.110.3", LOCIPSECFLAG=DISABLE, SECLOCIP="0.0.0.0", SECLOCIPSECFLAG=DISABLE, LOCPORT=2900,RTOMIN=1000, RTOMAX=3000, RTOINIT=1000, RTOALPHA=12, RTOBETA=25, HBINTER=5000, MAXASSOCRETR=10, MAXPATHRETR=5, CHKSUMTX=DISABLE, CHKSUMRX=DISABLE,CHKSUMTYPE=CRC32, SWITCHBACKFLAG=ENABLE, SWITCHBACKHBNUM=10, TSACK=200, CNOPERATORID=1;ADD MME: MMEID=0, FIRSTSIGIP="134.134.134.10", FIRSTIPSECFLAG=DISABLE, SECSIGIP="0.0.0.0", SECIPSECFLAG=DISABLE, LOCPORT=2900, CNOPERATORID=1, MMERELEASE=Release_R8;2.2.3用户面ADD S1SERVIP: CN=0, SRN=0, SN=6, S1SERVIPID="TO SGW", S1SERVIP="110.110.110.3", IPSECFLAG=DISABLE, PATHCHK=DISABLE, CNOPERATORID=1;ADD SGW: SGWID=0, SERVIP1="135.135.135.10", SERVIP1IPSECFLAG=DISABLE, SERVIP2="0.0.0.0", SERVIP2IPSECFLAG=DISABLE, SERVIP3="0.0.0.0", SERVIP3IPSECFLAG=DISABLE, SERVIP4="0.0.0.0", SERVIP4IPSECFLAG=DISABLE, CNOPERATORID=1;2.2.4维护面ADD OMCH: FLAG=MASTER, IP="110.110.110.3", MASK="255.255.255.0", PEERIP="172.100.100.16", PEERMASK="255.255.255.0", BEAR=IPV4, CN=0, SRN=0, SN=6, SBT=BASE_BOARD, BRT=NO;2.2.5无线数据ADD SECTOR: SECN=0, GCDF=DEG, LONGITUDE=0, LATITUDE=0, SECM=NormalMIMO, ANTM=8T8R, COMBM=COMBTYPE_SINGLE_RRU,SECTORNAME="SEC1",ALTITUDE=25,UNCERTSEMIMAJOR=3,NCERTSEMIMINOR=3, ORIENTOFMAJORAXIS=0, UNCERTALTITUDE=3, CONFIDENCE=0, OMNIFLAG=FALSE, CN1=0, SRN1=60, SN1=0, PN1=R0A, CN2=0, SRN2=60, SN2=0, PN2=R0B, CN3=0, SRN3=60, SN3=0, PN3=R0C, CN4=0, SRN4=60, SN4=0, PN4=R0D, CN5=0, SRN5=60, SN5=0, PN5=R0E, CN6=0, SRN6=60, SN6=0, PN6=R0F, CN7=0, SRN7=60, SN7=0, PN7=R0G, CN8=0, SRN8=60, SN8=0, PN8=R0H;ADD CELL: LocalCellId=0, CellName="CYTX_TEST_1",SectorId=0, CsgInd=BOOLEAN_FALSE, UlCyclicPrefix=NORMAL_CP, DlCyclicPrefix=NORMAL_CP, FreqBand=39, UlEarfcnCfgInd=NOT_CFG, DlEarfcn=38350, UlBandWidth=CELL_BW_N100, DlBandWidth=CELL_BW_N100, CellId=0, PhyCellId=112, AdditionalSpectrumEmission=1,FddTddInd=CELL_TDD,SubframeAssignment=SA2, SpecialSubframePatterns=SSP5, CellSpecificOffset=dB0, QoffsetFreq=dB0, RootSequenceIdx=156, HighSpeedFlag=LOW_SPEED,PreambleFmt=0,CellRadius=10000, CustomizedBandWidthCfgInd=NOT_CFG, EmergencyAreaIdCfgInd=NOT_CFG, UePowerMaxCfgInd=NOT_CFG, MultiRruCellFlag=BOOLEAN_FALSE, CPRICompression=NO_COMPRESSION;ADD CELLOP: LocalCellId=0, TrackingAreaId=0, CellReservedForOp=CELL_NOT_RESERVED_FOR_OP, OpUlRbUsedRatio=25, OpDlRbUsedRatio=25;ACT CELL: LocalCellId=0四、实习收获与体会A、问题及解决方法1.练习一,配置路由表时,将目的地址写成了135.135.135.16,而在逻辑规划拓扑图中配置的135.135.135.10,导致路由不可达。

通信网络实验报告

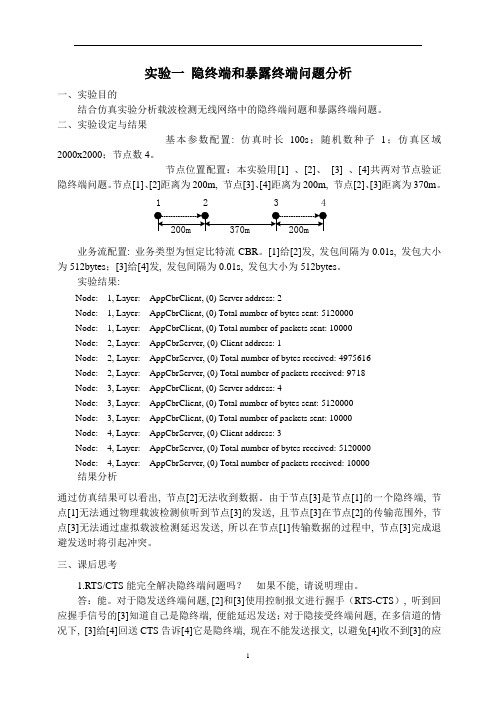

实验一隐终端和暴露终端问题分析一、实验目的结合仿真实验分析载波检测无线网络中的隐终端问题和暴露终端问题。

二、实验设定与结果基本参数配置: 仿真时长100s;随机数种子1;仿真区域2000x2000;节点数4。

节点位置配置:本实验用[1] 、[2]、[3] 、[4]共两对节点验证隐终端问题。

节点[1]、[2]距离为200m, 节点[3]、[4]距离为200m, 节点[2]、[3]距离为370m。

1234业务流配置: 业务类型为恒定比特流CBR。

[1]给[2]发, 发包间隔为0.01s, 发包大小为512bytes;[3]给[4]发, 发包间隔为0.01s, 发包大小为512bytes。

实验结果:Node: 1, Layer: AppCbrClient, (0) Server address: 2Node: 1, Layer: AppCbrClient, (0) Total number of bytes sent: 5120000Node: 1, Layer: AppCbrClient, (0) Total number of packets sent: 10000Node: 2, Layer: AppCbrServer, (0) Client address: 1Node: 2, Layer: AppCbrServer, (0) Total number of bytes received: 4975616Node: 2, Layer: AppCbrServer, (0) Total number of packets received: 9718Node: 3, Layer: AppCbrClient, (0) Server address: 4Node: 3, Layer: AppCbrClient, (0) Total number of bytes sent: 5120000Node: 3, Layer: AppCbrClient, (0) Total number of packets sent: 10000Node: 4, Layer: AppCbrServer, (0) Client address: 3Node: 4, Layer: AppCbrServer, (0) Total number of bytes received: 5120000Node: 4, Layer: AppCbrServer, (0) Total number of packets received: 10000结果分析通过仿真结果可以看出, 节点[2]无法收到数据。

无线通信实验报告

篇一:无线通信实验报告无线通信实验报告院系名称:信息科学与工程学院专业班级:电子信息工程10级1班学生姓名:学号:授课教师:杨静2013 年 10 月 24 日实验一qpsk信号的误码率仿真1. 实验分析四相相移调制是利用载波的四种不同相位差来表征输入的数字信息,是四进制移相键控。

它规定了四种载波相位,分别为45°,135°,225°,275°,调制器输入的数据是二进制数字序列,为了能和四进制的载波相位配合起来,需要把二进制数字序列中每两个比特分成一组,共有四种组合,即00,01,10,11,其中每一组称为双比特码元。

每一个双比特码元是由两位二进制信息比特组成,它们分别代表四进制四个符号中的一个符号。

2. 源代码:close all;clc;clear all;snr_db=[0:1:12];sum=10000;data= randsrc(sum,2,[0 1]);[a1,b1]=find(data(:,1)==0&data(:,2)==0);message(a1)=-1-j;[a2,b2]=find(data(:,1)==0&data(:,2)==1);message(a2)=-1+j;[a3,b3]=find(data(:,1)==1&data(:,2)==0);message(a3)=1-j;[a4,b4]=find(data(:,1)==1&data(:,2)==1);message(a4)=1+j;a=1;tb=1;eb=a*a*tb;p_signal=eb/tb;no=eb./(10.^(snr_db/10));p_noise=p_signal*no;sigma=sqrt(p_noise);for eb_no_id=1:length(sigma)noise1=sigma(eb_no_id)*randn(1,sum);noise2=sigma(eb_no_id)*randn(1,sum);receive=message+noise1+noise2*j;resum=0;total=0;m1=find(angle(receive)<=pi/2&angle(receive)>0);remessage(1,m1)=1+j;redata(m1,1)=1;redata(m1,2)=1;m2= find( angle(receive)>pi/2&angle(receive)<=pi);remessage(1,m2)=-1+j;redata(m2,1)=0;redata(m2,2)=1;m3=find( angle(receive)>-pi&angle(receive)<=-pi/2);remessage(1,m3)=-1-j;redata(m3,1)=0;redata(m3,2)=0;m4=find( angle(receive)>-pi/2&angle(receive)<=0);remessage(1,m4)=1-j;redata(m4,1)=1;redata(m4,2)=0;[resum,ratio1]=symerr(data,redata);pbit(eb_no_id)=resum/(sum*2);[total,ratio2]=symerr(message,remessage);pe(eb_no_id)=total/sum;endsemilogy(snr_db,pe,:s,snr_db,pbit,-o);legend(qpsk仿真误码率,qpsk仿真误比特率);xlabel(信噪比/db);ylabel(概率p);grid on;3. 仿真结果实验二am调幅波的仿真1. 实验分析 am调制方式,属于基带调制,原理是使高频载波的频率随信号幅度改变而改变的调制,我们使用的载波的是正弦波,将信号作为振幅加到载波上,即可实现。

无线通信实验

《无线通信实验报告》姓名:陈犇学号:152210704111专业:通信工程学院:计算机学院2018年11月目录背景:无线信道模型概述 (3)第一章多径和多普勒效应 (3)一. 实验目的 (3)二. 实验原理 (3)三. 实验步骤 (4)背景:无线信道模型概述当设计一个无线通信链路的时候,我们需要问以下三个重要的问题:1.衰落和功率损耗2.信号失真3.时变一个完整的信道模型应该提供SINR的量数,信号散射和时变参数。

为了清楚这三个问题,把无线信道模型分为三个部分:1.传输损耗:信号频率,时变环境2.频率相关信道冲击响应或者传输函数:多个频率,时变环境3.时变信道冲击响应或传输函数第一章多径和多普勒效应一. 实验目的1)理解时域和频域中的多径信道效应2)理解时域和频域的多普勒效应3)理解时域和频域中的多径和多普勒效应二. 实验原理多径效应(multipath effect):指电磁波经不同路径传播后,各分量场到达接收端时间不同,按各自相位相互叠加而造成干扰,使得原来的信号失真,或者产生错误。

比如电磁波沿不同的两条路径传播,而两条路径的长度正好相差半个波长,那么两路信号到达终点时正好相互抵消了(波峰与波谷重合)。

多普勒效应Doppler effect是为纪念奥地利物理学家及数学家克里斯琴·约翰·多普勒(Christian Johann Doppler)而命名的,他于1842年首先提出了这一理论。

主要内容为物体辐射的波长因为波源和观测者的相对运动而产生变化。

在运动的波源前面,波被压缩,波长变得较短,频率变得较高(蓝移blue shift );在运动的波源后面时,会产生相反的效应。

波长变得较长,频率变得较低(红移red shift );波源的速度越高,所产生的效应越大。

根据波红(蓝)移的程度,可以计算出波源循着观测方向运动的速度.三. 实验步骤(一) 多径信道效应:时变(无多普勒效应)在无线通信中,一个从发送端的信号经过多条路径到达接收端。

无线通信实验报告

无线通信实验报告《无线通信实验报告》无线通信技术是当今社会中不可或缺的一部分,它的发展不仅改变了人们的生活方式,也推动了整个社会的进步。

为了更好地理解和掌握无线通信技术,我们进行了一次无线通信实验,以下是实验报告。

实验目的:通过实验,了解无线通信技术的基本原理和应用,掌握无线通信系统的搭建和调试方法,提高对无线通信技术的理论和实践操作能力。

实验内容:1. 了解无线通信技术的基本原理和应用;2. 学习无线通信系统的搭建和调试方法;3. 进行无线通信系统的实际操作,观察和记录实验现象;4. 分析实验结果,总结无线通信技术的特点和应用场景。

实验步骤:1. 阅读相关无线通信技术的理论知识,了解无线通信系统的基本原理和应用;2. 按照实验指导书的要求,搭建无线通信系统实验平台;3. 进行无线通信系统的调试和操作,观察和记录实验现象;4. 分析实验结果,总结无线通信技术的特点和应用场景。

实验结果:通过实验,我们深入了解了无线通信技术的基本原理和应用,掌握了无线通信系统的搭建和调试方法,提高了对无线通信技术的理论和实践操作能力。

同时,我们也发现无线通信技术具有广泛的应用场景,可以在移动通信、物联网、航空航天等领域发挥重要作用。

结论:无线通信技术是一项重要的技术,它的发展不仅改变了人们的生活方式,也推动了整个社会的进步。

通过本次实验,我们更加深入地了解了无线通信技术的基本原理和应用,掌握了无线通信系统的搭建和调试方法,提高了对无线通信技术的理论和实践操作能力。

希望通过不断的学习和实践,我们能够更好地应用无线通信技术,为社会的发展做出更大的贡献。

通信系统综合实验报告

通信系统综合实验报告实验一无线多点组网一、实验步骤1、组建树型网络组建5个节点的树形网络,阐述组建的过程。

2、进行数据传输节点之间进行通信,并记录路由信息,最后,进行组播和广播,观察其特点。

二、实验过程1、组建树型网络(1).网络1A、首先在配置中寻找到其他4个节点的地址信息。

自身地址:00:37:16:00:A5:46B、查找设备C、建立连接组网假设参加组网的共有5个BT设备,称为a、b、c、d、e。

首先由一个设备(例如b)发起查询,如果找到多个设备,则任选其二(例如d、e)主动与其建链。

在这个阶段,b、d、e构成一个微微网,b为主设备(M),d、e为从设备(S)。

注意在微微网中对处于激活状态的从设备的个数限制为2;而某个设备一旦成为从设备(即d、e),它就不能再被其它设备发现,也不能查询其它设备或与其它设备建链。

再由另外一个设备(a)发起查询,查询到设备b和设备c,再主动链接。

(1).网络1组建的网络图(1)(2)网络2同理,首先,在配置中寻找到其他4个节点的地址信息。

然后查找设备,再建立连接。

由地址为00:37:16:00:A5:42的节点连接00:37:16:00:A5:46和00:37:16:00:A5:43,再由00:37:16:00:A5:47连接00:37:16:00:A5:42和00:37:16:00:A5:45,最后组成网络。

组建的网络图(2)2.进行数据传输(1)点对点发送信息例如,对于组建的网络2.图中显示的是:00:37:16:00:A5:4A对00:37:16:00:A5:43的路由,途中经过了00:37:16:00:A5:47,00:37:16:00:A5:42由此可见,简单拓扑结构,路由具有唯一性。

(2)组播与广播1. 广播:由任何一个节点设备向网络内的所有其他节点发送同一消息,观察其发送的目标地址以及数据交换过程。

在这种情况下的路由过程与两个节点间数据单播的过程有何不同。

无线移动实验报告

一、实验目的1. 了解无线移动通信的基本原理和关键技术。

2. 掌握无线移动通信设备的配置和调试方法。

3. 熟悉无线移动通信网络的组建和优化。

4. 培养实际操作能力和团队合作精神。

二、实验环境1. 实验设备:无线移动通信设备、电脑、测试仪器等。

2. 实验软件:无线移动通信仿真软件、网络配置软件等。

3. 实验场地:无线移动通信实验室。

三、实验内容1. 无线移动通信原理(1)无线移动通信的基本概念无线移动通信是指通过无线电波在移动终端和基站之间进行信息传输的一种通信方式。

其主要特点是不受地理位置限制,可以实现随时随地通信。

(2)无线移动通信的关键技术1)调制解调技术:将数字信号转换为模拟信号,再通过无线信道传输,接收端再将模拟信号还原为数字信号。

2)编码技术:将原始信息进行编码,提高传输效率和抗干扰能力。

3)多址技术:在无线信道中,多个用户共享同一信道,实现多用户通信。

4)同步技术:确保移动终端和基站之间的时间同步,提高通信质量。

5)功率控制技术:根据信道质量调整发射功率,降低干扰和功耗。

2. 无线移动通信设备配置(1)无线移动通信设备的连接将无线移动通信设备与电脑连接,确保设备正常工作。

(2)无线移动通信设备的参数配置1)设置无线移动通信设备的IP地址、子网掩码、网关等网络参数。

2)配置无线移动通信设备的信道、频率、功率等无线参数。

3)设置无线移动通信设备的QoS(服务质量)参数。

3. 无线移动通信网络组建(1)组建无线移动通信网络拓扑根据实验需求,设计无线移动通信网络拓扑结构。

(2)配置无线移动通信网络设备1)配置无线接入点(AP)和基站(BS)的IP地址、子网掩码、网关等网络参数。

2)配置AP和BS的无线参数,如信道、频率、功率等。

3)配置AP和BS之间的互联,确保网络互联互通。

4. 无线移动通信网络优化(1)信道优化根据信道质量,调整AP和BS的信道、频率、功率等参数,提高通信质量。

(2)功率控制优化根据信道质量,动态调整AP和BS的发射功率,降低干扰和功耗。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验报告课程名称:无线通信与网络实验项目:matlab仿真实验实验地点:专业班级:学号:学生姓名:指导教师:2013年4月12日实验1 卷积编码和译码的matlab仿真实现一、实验目的了解掌握如何使用matlab来进行卷积编码和译码的仿真。

二、实验内容1、SIMULINK仿真模块的参数设置以及重要参数的意义2、不同回溯长度对卷积码性能的影响3、不同码率对卷积码误码性能的影响4、不同约束长度对卷积码的误码性能影响三、基本原理本实验分为卷积编码和卷积译码两部分:卷积编码的最佳译码准则为:在给定已知编码结构、信道特性和接收序列的情况下,译码器将把与已经发送的序列最相似的序列作为传送的码字序列的估值。

对于二进制对称信道,最相似传送序列就是在汉明距离上与接收序列最近的序列。

卷积码的译码方法有两大类:一类是大数逻辑译码,又称门限译码(硬判决);另一种是概率译码(软判决),概率译码又分为维特比译码和序列译码两种。

门限译码方法是以分组码理论为基础的,其译码设备简单,速度快,但其误码性能要比概率译码法差[2]。

当卷积码的约束长度不太大时,与序列译码相比,维特比译码器比较简单,计算速度快。

维特比译码算法是1967年由Viterbi提出,近年来有大的发展。

目前在数字通信的前向纠错系统中用的较多,而且在卫星深空通信中应用更多,该算法在卫星通信中已被采用作为标准技术。

采用概率译码的基本思想是:把已接收序列与所有可能的发送序列做比较,选择其中码距最小的一个序列作为发送序列。

如果发送L组信息比特,那么对于(n,k)卷积码来说,可能发送的序列有2kL个,计算机或译码器需存储这些序列并进行比较,以找到码距最小的那个序列。

当传信率和信息组数L较大时,使得译码器难以实现。

维特比算法则对上述概率译码做了简化,以至成为了一种实用化的概率算法。

它并不是在网格图上一次比较所有可能的2kL 条路径(序列),而是接收一段,计算和比较一段,选择一段最大似然可能的码段,从而达到整个码序列是一个最大似然值得序列。

下面以图2.1的(2,1,3)卷积码编码器所编出的码为例,来说明维特比解码的方法和运作过程。

为了能说明解码过程,这里给出该码的状态图,如图2.2所图2.1 (2,1,3)卷积码编码器图2.2 (2,1,3)卷积码状态图示。

维特比译码需要利用图来说明移码过程。

根据卷积码画网格的方法,我们可以画出该码的网格图,如图2.3所示。

该图设输入信息数目L=5,所以画L+N=8个时间单位,图中分别标以0至7。

这里设编码器从a 状态开始运作。

该网格图的每一条路径都对应着不同的输入信息序列。

由于所有可能输入信息序列共有2kL 个,因而网格图中所有可能的路径也为2kL 条。

这里节点a=00,b=01,c=10,d=11。

ba bc d节点号1234567图2.3 (2,1,3)卷积码网格图设输入编码器的信息序列为(11011000),则由编码器对应输出的序列为Y=(1101010001011100),编码器的状态转移路线为abdcbdca 。

若收到的序列R=(0101011001011100),对照网格图来说明维特比译码的方法。

由于该卷积码的约束长度为6位,因此先选择接收序列的前6位序列R 1=(010101)同到达第3时刻的可能的8个码序列(即8条路径)进行比较,并计算出码距。

该例中到达第3时刻a 点的路径序列是(000000)和(111011),他们与R 1的距离分别为3和4;到达第3时刻b 点的路径序列是(000011)和(111000),他们与R 1的距离分别为3和4;到达第3时刻b 点的路径序列是(000011)和(111000),他们与R 1的距离分别为3和4;到达第3时刻c 点的路径序列是(001110)和(110101),他们与R 1的距离分别为4和1;到达第3时刻d 点的路径序列是(001101)和(110110),他们与R 1的距离分别为2和3。

上述每个节点都保留码距较小的路径作为幸存路径,所以幸存路径码序列是(000000)、(000011)、(1101001)和(001101),如图2.4所示。

用于上面类似的方法可以得到第4、5、6、7时刻的幸存路径。

需要指出的是,对于某个节点,如果比较两条路径与接收序列的累计码距值相等时,则可以任意选者一条路径作为幸存路径,吃时不会影响最终的译码结果。

在码的终了时刻a 状态,得到一条幸存路径。

如果2.5所示。

由此可看到译码器a b c d节点号123图2.4 维特比译码第3时刻幸存路径输出是R ’=(1101010001011100),即可变换成序列(11011000),恢复了发端原始信息。

比较R ’和R 序列,可以看到在译码过程中已纠正了在码序列第1和第7位上的差错。

当然如果差错出现太频繁,以致超出卷积码的纠错能力,还是会发生纠误的。

四、实验步骤4.1 卷积码的仿真本文通过MATLAB 下的SIMULINK 仿真。

首先建立卷积码的仿真模块并组合起来。

图4-1卷积码的编码译码框图如上图4-1的信号流程可以表示为先由Bernoulli Binary Generator (贝努利二进制序列产生器)产生一个0,1等概序列,经过Convolutional Encoder (卷积编码器)对输入的二进制序列进行卷积编码,并用BPSK 调制方式调制信号。

加入信道噪声(高斯白噪声)后再经过BPSK 解调制后送入Viterbi Decoder (Viterbia b c d节点号 01 2 34 5 6 7 8图2.5 第8时刻幸存路径译码器)进行硬判决译码。

最后经过Error Rate Calculation(误码统计)后由Display (显示)输出。

然后通过Selector(数据选通器)将结果输出到To workspace(工作区间)。

4.1.1 SIMULINK仿真模块的参数设置以及重要参数的意义在建立如图4-1的仿真模块后,对各个模块分别一一进行设置后并运行仿真。

图4-2贝努利二进制序列产生器模块的设置框图如上图4-2是贝努利二进制序列产生器模块的设置框图,其中参数有三项:第一项probability of a zero取值为0.5,表示0和1出现的概率相等。

Initial seed 表示随机种子数。

不同的随机种子数将产生不同的二进制序列,特定的随机种子数可以产生一个特定的二进制序列。

Sample time=0.0001表示抽样时间,也就是说输出序列中每个二进制符号的持续时间是0.0001秒。

Samples per frame 表示每帧的抽样数用来确定每帧的抽样点的数目。

Frame-based outputs 是用来确定帧的输出格式。

图4-3 BPSK调制器模块的设置框图如上图4-3是BPSK调制器模块的设置框图中有二项,第一项是Phase offset(rad)(相位偏移),这里设置为0。

第二项是Samples per symbol(输出信号采样数)这里设置为1。

图4-4卷积编码器模块的设置框图如上图4-4是卷积编码器模块的设置框图。

其中Trellis structure(Trellis结构)中通过poly2trellis()函数把卷积码的约束长度,生成多项式以及反馈多项式转换成Trellis结构的形式。

图4-5误比特统计模块的设置框图如上图4-5是误比特统计模块的设置框图。

其中Receive delay表示接收延迟,意思是在通信接收端口需要对接收到的信号进行解调,解码或解交织而带来一定的延迟,使得到达误码统计模块接收端的信号滞后于发送端的信号。

为了补偿这种延迟这里设置为0。

Computation delay表示计算延迟,在仿真过程中,有时间需要忽略最初的若干个输入数据就通过计算延迟来实现。

这里设置为0。

Computation mode表示计算模式,帧的计算模式(Entire frame),误码统计模块对发送端和接收端的所有输入数据进行统计。

output data是输出数据,这里设置为Port的意思是表示把统计数据从端口中输出。

workspace表示把统计数据输出到工作区。

图4-6 数据选通器模块的设置框图如上图4-6是数据选通器模块的设置框图。

对应图4-1看Elements是指输出端口的个数为1。

Input port width表示输入端口的个数为3。

图4-7卷积码译码器模块的设置框图如上图4-7是卷积码译码器模块的设置框图。

Trellis structure: Trellis结构(前面已说明)。

Decision type是指判决类型,有3种:(1)Unquantized(非量化)(2)Hard Decision(硬判决),(3)Soft Decision(软判决)Traceback depth表示反馈深度。

它的值会影响译码精度和解码延迟。

Operation mode是指操作模式。

在Truncated模式下,解码器在每帧数据结束的时候总能恢复到全0状态,它与卷积编码器的on each frame复位方式相对应。

4.2 改变卷积码的参数仿真以及结论4.2.1 不同回溯长度对卷积码性能的影响下面将以(2,1,7)卷积码来建立模块仿真。

将译码模块中的Traceback depth 分别设置为20,35,45并在一个图中画出这三种方式下的误码性能曲线得到下图4-8。

从上到下的三条曲线分别是Traceback depth为20,35,45。

可以看出:回溯长度是在Viterbi 译码过程中一个很重要的参数,他决定了译码延迟,随着他的不断变化,误码性能也随误比特率曲线可以清楚地看到,当回溯长度一定时,随着信道噪声的逐渐减小,系统的误比特率逐渐降低;当回溯长度逐渐增加,系统的误比特率随之逐渐降低,但是当回溯程度τ增加到τ≥5 N 时( N 为编码的约束长度) ,误比特率数值趋于稳定,因此,在确定回溯长度时既要考虑到随着τ的增加误比特率随之降低的趋势,也要考虑到译码延迟会变大,在选取回溯长度时,通常取τ= 5 N。

图4-8 不同回溯长度对误码性能的影响分析不同回溯长度对卷积码误码性能的影响时用到的程序如下:x=-10:5;y=x;fori=1:length(x)SNR=x(i);sim('yima');y(i)=mean(BitErrorRate);endsemilogy(x,y);hold on;fori=1:length(x)SNR=x(i);sim('yima1');y(i)=mean(BitErrorRate);endsemilogy(x,y);hold on;fori=1:length(x)SNR=x(i);sim('yima2');y(i)=mean(BitErrorRate);endsemilogy(x,y);4.2.2 不同码率对卷积码误码性能的响下面图4-9是通过改变卷积码的码率为1/2和1/3而得到的二条对比曲线。