集成电路课程设计模板及参考资 [1]...

集成电路应用课程设计

集成电路应用课程设计一、课程目标知识目标:1. 让学生掌握集成电路的基本概念,了解集成电路的种类及特点。

2. 使学生理解集成电路的工作原理,掌握集成电路的引脚排列及功能。

3. 培养学生运用集成电路进行电路设计的能力,熟悉常见的集成电路应用电路。

技能目标:1. 培养学生独立查阅集成电路数据手册,提取关键信息的能力。

2. 提高学生动手实践能力,学会使用面包板进行集成电路的搭建和测试。

3. 培养学生运用所学知识解决实际问题的能力,设计具有实际应用的集成电路电路。

情感态度价值观目标:1. 培养学生对电子技术的兴趣,激发学生探索集成电路内部奥秘的欲望。

2. 培养学生团队协作意识,学会与他人共同解决问题,培养良好的沟通能力。

3. 增强学生的环保意识,认识到电子产品废弃物的处理和回收的重要性。

课程性质:本课程为电子技术领域的一门实践性较强的课程,旨在培养学生的电路设计能力和动手实践能力。

学生特点:学生已具备一定的电子技术基础知识,对集成电路有一定了解,但对实际应用尚不熟悉。

教学要求:结合课程特点和学生实际情况,注重理论与实践相结合,充分调动学生的主观能动性,提高学生的实践操作能力。

在教学过程中,关注学生的个体差异,因材施教,使学生在课程学习中取得良好的成果。

通过课程学习,使学生能够独立设计并搭建具有实际应用的集成电路电路。

二、教学内容1. 集成电路基本概念:包括集成电路的定义、分类、特点及应用领域。

2. 集成电路工作原理:介绍集成电路内部结构,重点讲解晶体管、MOS管等基本元件的工作原理。

3. 集成电路引脚排列及功能:以常用集成电路为例,分析其引脚排列及各引脚的功能。

4. 集成电路数据手册查阅:教授学生如何查阅集成电路数据手册,提取关键信息。

5. 集成电路应用电路设计:结合教材,讲解并设计具有实际应用的集成电路电路。

6. 面包板搭建与测试:培养学生动手实践能力,学会使用面包板搭建集成电路电路并进行测试。

教学内容安排与进度:第一周:集成电路基本概念及分类第二周:集成电路工作原理第三周:集成电路引脚排列及功能第四周:集成电路数据手册查阅第五周:集成电路应用电路设计第六周:面包板搭建与测试教材章节关联:第一章:电子元件概述第二章:晶体管及MOS管第三章:集成电路第四章:集成电路应用第五章:电路设计与实践教学内容确保科学性和系统性,结合课程目标,使学生能够循序渐进地掌握集成电路的相关知识,为后续课程学习打下坚实基础。

集成电路课程设计(CMOS二输入与门).

课程设计任务书学生姓名:王伟专业班级:电子1001班指导教师:刘金根工作单位:信息工程学院题目: 基于CMOS的二输入与门电路初始条件:计算机、Cadence软件、L-Edit软件要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求)1、课程设计工作量:2周2、技术要求:(1)学习Cadence IC软件和L-Edit软件。

(2)设计一个基于CMOS的二输入的与门电路。

(3)利用Cadence和L-Edit软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。

3、查阅至少5篇参考文献。

按《武汉理工大学课程设计工作规范》要求撰写设计报告书。

全文用A4纸打印,图纸应符合绘图规范。

时间安排:2013.11.22布置课程设计任务、选题;讲解课程设计具体实施计划与课程设计报告格式的要求;课程设计答疑事项。

2013.11.25-11.27学习Cadence IC和L-Edit软件,查阅相关资料,复习所设计内容的基本理论知识。

2013.11.28-12.5对二输入与门电路进行设计仿真工作,完成课设报告的撰写。

2013.12.6 提交课程设计报告,进行答辩。

指导教师签名:年月日系主任(或责任教师)签名:年月日目录摘要 (2)绪论 (3)一、设计要求 (4)二、设计原理 (4)三、设计思路 (4)3.1、非门电路 (4)3.2、二输入与非门电路 (6)3.3、二输入与门电路 (8)四、二输入与门电路设计 (9)4.1、原理图设计 (9)4.2、仿真分析 (10)4.3、生成网络表 (13)五、版图设计................................................... (20)5.1、PMOS管版图设计 (20)5.2、NMOS管版图设计 (22)5.3、与门版图设计 (23)5.4、总版图DRC检查及SPC文件的生成 (25)六、心得体会 (28)七、参考文献 (29)八、附录 (30)摘要本文从设计到仿真以及后面的版图制作等主要用到了Cadence IC软件和L-Edit软件等。

(整理)集成电路课设

课程设计任务书学生姓名:*** 专业班级:电子1002班指导教师:葛华工作单位:信息工程学院题目: 基于TANNER软件的或非门设计初始条件:计算机、TANNER软件要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求)1、课程设计工作量:2周2、技术要求:(1)学习TANNER软件。

(2)设计一个或非门电路。

(3)利用TANNER软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。

3、查阅至少5篇参考文献。

按《武汉理工大学课程设计工作规范》要求撰写设计报告书。

全文用A4纸打印,图纸应符合绘图规范。

时间安排:2013.11.22布置课程设计任务、选题;讲解课程设计具体实施计划与课程设计报告格式的要求;课程设计答疑事项。

2013.11.25-11.27学习TANNER软件,查阅相关资料,复习所设计内容的基本理论知识。

2013.11.28-12.5对或非门电路进行设计仿真工作,完成课设报告的撰写。

2013.12.6 提交课程设计报告,进行答辩。

指导教师签名:年月日系主任(或责任教师)签名:年月日摘要 (3)Abstract (4)1绪论 (5)1.1 版图设计的基本知识 (5)1.1.1 版图设计流程 (5)1.1.2版图设计步骤 (6)1.1.3 版图设计规则及验证 (6)1.2 标准单元版图设计 (7)1.2.1 标准单元库的定义 (7)1.2.2 标准单元库设计流程 (7)1.3 0.35um工艺的设计规则 (7)2 或非门简要介绍 (9)3 0.35um或非门设计 (10)3.1 或非门电路设计及电路图 (10)3.2 或非门版图设计 (11)3.3 DRC验证 (12)3.4 或非门电路的TSPICE仿真 (14)4 课程设计总结 (16)参考文献 (17)或非门是一种非常常用的数字门电路,本文详细介绍了基于MOS管的TANNER环境下的或非门电路设计仿真及版图布局设计验证。

《集成电路》教案

《集成电路》教案集成电路教案一、教学目标本课程的教学目标主要包括:1. 了解集成电路的定义和发展历程;2. 掌握集成电路的分类和特点;3. 理解集成电路的制作原理和工艺流程;4. 熟悉集成电路在电子设备中的应用;5. 培养学生对集成电路的设计和应用能力。

二、教学内容1. 集成电路的定义和发展历程- 集成电路的概念和基本原理- 集成电路的发展历程及其对电子技术的影响2. 集成电路的分类和特点- 按功能分类:逻辑集成电路、模拟集成电路、混合集成电路- 按制造工艺分类:SSI、MSI、LSI、VLSI、ULSI- 集成电路的特点和优势3. 集成电路的制作原理和工艺流程- MOSFET和BJT的基本原理- NMOS和PMOS工艺流程- CMOS工艺流程4. 集成电路在电子设备中的应用- 数字电路中的集成电路应用- 模拟电路中的集成电路应用- 通信和嵌入式系统中的集成电路应用5. 集成电路的设计和应用能力培养- 理解集成电路的设计流程和方法- 使用专业软件进行集成电路设计- 实践项目:设计简单的集成电路电路板三、教学方法本课程采用以下教学方法:1. 讲授法:通过讲解集成电路的基本概念、分类和制作原理,帮助学生建立起相关知识的框架。

2. 实验法:通过实验,让学生亲自操作、观察和验证集成电路的工作原理和应用。

3. 讨论法:通过小组讨论、案例分析等互动方式,加深学生的理解和应用能力。

四、教学评估本课程的评估方式包括:1. 作业:布置相关理论和实践作业,考察学生对集成电路的理解和应用能力。

2. 实验报告:要求学生完成相应的实验报告,对实验结果进行分析和总结。

3. 期末考试:考核学生对课程内容的掌握情况。

五、教学资源本课程所需的教学资源包括:1. 教材:《集成电路导论》2. 实验设备和器材:集成电路开发板、示波器、信号发生器等3. 计算机和软件:EDA软件、仿真软件等六、参考文献1. 陈明. 集成电路[M]. 电子工业出版社, 2018.2. 邓家舜. 集成电路原理与应用[M]. 电子工业出版社, 2017.3. 朱义伟, 等. 集成电路设计与实例分析[M]. 机械工业出版社, 2019.以上是《集成电路》教案的大纲和内容介绍,希望能够帮助学生全面理解和掌握集成电路的基本知识和应用。

集成电路课程设计方案电科

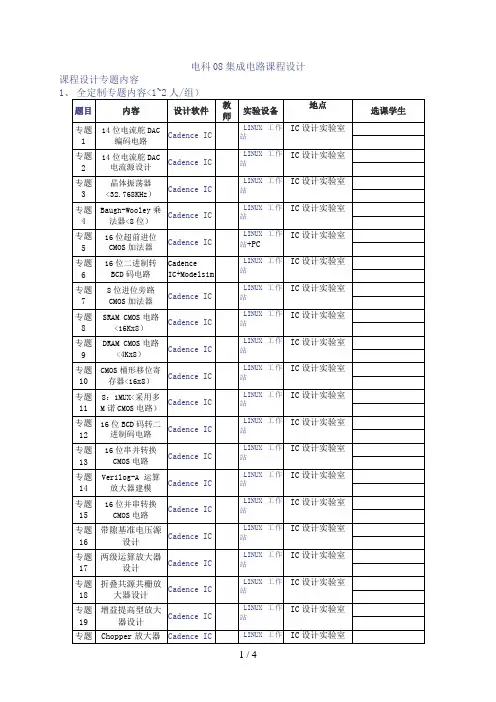

电科08集成电路课程设计课程设计专题内容

1

课程设计专题内容

1. 课程设计总学时:一周<20学时)。

2. 每位学生可根据自己的能力选择难易程度不同的题目,但每个题目的选择人数不得超过2人,合作者必须有明确的分工,并在报告明确注明,报告中除系统设计的描述可类似,其余必须不同。

3. 要求花费课外时间自行理解消化题目、查阅资料、学习语法、熟悉设计流程,希望在上机编写代码以及调试之前能完全理解设计题目,根据自己的能力最终确定详细的任务与指标,鼓励课题中的创新设计<如功能的扩展、指标的提高)。

4. 报告要求解题过程、仿真代码、以及仿真波形、对波形的适当解释、硬件的调试等以及个人心得体会。

每人提交一份报告<书面和电子版)。

报告雷同者直接做不及格处理,报告格式参考附录。

5. 设计成功后,必须让教师现场检查源代码、波形、版图、硬件等,并回答教师的提问,创新设计部分需特别指出,详细说明。

6. 报告提交截止时间:课程设计结束后3天。

7. 评价标准如下所示,考核成绩将会考虑实际完成课题难度。

集成电路设计课程设计课程教学大纲

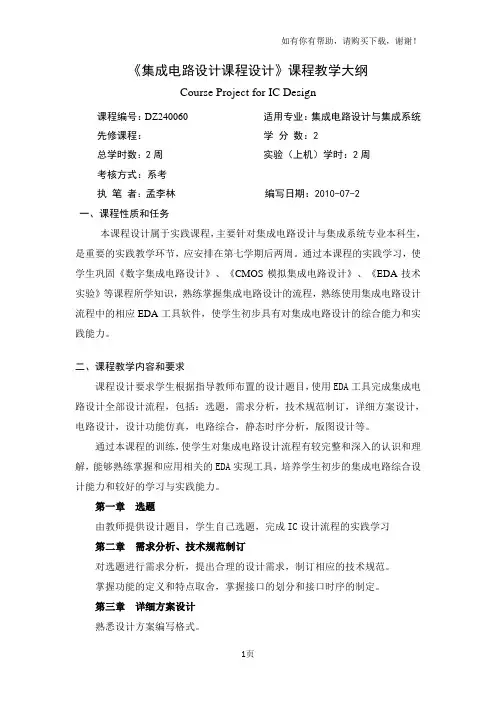

《集成电路设计课程设计》课程教学大纲Course Project for IC Design课程编号:DZ240060 适用专业:集成电路设计与集成系统先修课程:学分数:2总学时数:2周实验(上机)学时:2周考核方式:系考执笔者:孟李林编写日期:2010-07-2一、课程性质和任务本课程设计属于实践课程,主要针对集成电路设计与集成系统专业本科生,是重要的实践教学环节,应安排在第七学期后两周。

通过本课程的实践学习,使学生巩固《数字集成电路设计》、《CMOS模拟集成电路设计》、《EDA技术实验》等课程所学知识,熟练掌握集成电路设计的流程,熟练使用集成电路设计流程中的相应EDA工具软件,使学生初步具有对集成电路设计的综合能力和实践能力。

二、课程教学内容和要求课程设计要求学生根据指导教师布置的设计题目,使用EDA工具完成集成电路设计全部设计流程,包括:选题,需求分析,技术规范制订,详细方案设计,电路设计,设计功能仿真,电路综合,静态时序分析,版图设计等。

通过本课程的训练,使学生对集成电路设计流程有较完整和深入的认识和理解,能够熟练掌握和应用相关的EDA实现工具,培养学生初步的集成电路综合设计能力和较好的学习与实践能力。

第一章选题由教师提供设计题目,学生自己选题,完成IC设计流程的实践学习第二章需求分析、技术规范制订对选题进行需求分析,提出合理的设计需求,制订相应的技术规范。

掌握功能的定义和特点取舍,掌握接口的划分和接口时序的制定。

第三章详细方案设计熟悉设计方案编写格式。

针对所选题目,编写出详细设计方案。

第四章电路设计熟练掌握HDL,针对设计需求,采用HDL进行电路设计。

第五章设计功能仿真熟悉仿真工具的使用。

熟练应用EDA仿真工具进行设计功能仿真验证。

第六章电路综合理解电路综合的概念。

理解Tcl语言,掌握综合约束脚本的写法。

熟悉电路综合工具,完成设计电路的综合。

第七章时序分析理解静态时序分析中基本概念。

掌握PT工具的基本使用方法。

数字集成电路课程设计

数字集成电路课程设计一、课程目标知识目标:1. 让学生理解数字集成电路的基本概念,掌握常用数字逻辑电路的组成、工作原理及应用。

2. 使学生了解数字集成电路的设计流程,掌握使用硬件描述语言(如Verilog HDL)进行数字电路设计的基本方法。

3. 帮助学生掌握数字电路的仿真、测试与优化方法。

技能目标:1. 培养学生运用所学知识,独立完成简单的数字集成电路设计任务。

2. 培养学生运用硬件描述语言进行数字电路编程的能力。

3. 培养学生分析问题、解决问题的能力,提高创新意识和团队协作能力。

情感态度价值观目标:1. 激发学生对数字集成电路的兴趣,培养其探索精神。

2. 培养学生严谨、踏实的科学态度,养成良好的学习习惯。

3. 增强学生的环保意识,使其关注数字集成电路对环境的影响。

分析课程性质、学生特点和教学要求,本课程目标旨在使学生在掌握数字集成电路基本知识的基础上,提高实际设计能力,培养创新思维和团队协作能力。

通过课程学习,使学生能够具备以下具体学习成果:1. 能够正确描述常用数字逻辑电路的组成、工作原理及应用。

2. 能够运用硬件描述语言进行简单数字电路设计。

3. 能够分析并解决数字电路设计过程中遇到的问题。

4. 能够参与团队协作,完成具有一定难度的数字集成电路设计项目。

二、教学内容本章节教学内容依据课程目标,紧密围绕数字集成电路的设计原理和实践操作,确保科学性和系统性。

具体教学内容安排如下:1. 数字集成电路基础知识- 数字逻辑电路的基本概念与分类- 常用数字逻辑电路(如与门、或门、非门等)的组成、工作原理及应用2. 硬件描述语言(Verilog HDL)基础- Verilog HDL的基本语法和结构- 常用Verilog HDL语句及其功能描述3. 数字集成电路设计流程- 设计需求分析- 电路设计、编码、仿真与测试- 优化与调试4. 常用数字集成电路设计实例- 简单组合逻辑电路设计- 时序逻辑电路设计- 数字信号处理电路设计5. 数字电路设计工具与平台- 硬件描述语言编译器(如ModelSim)- 电路设计与仿真软件(如Quartus II)教学内容参照教材相关章节进行安排,确保与课程目标紧密结合。

集成电路课程设计报告

课程设计班级:姓名:学号:成绩:电子与信息工程学院电子科学系CMOS二输入与非门的设计一、概要随着微电子技术的快速发展,人们生活水平不断提高,使得科学技术已融入到社会生活中每一个方面。

而对于现代信息产业和信息社会的基础来讲,集成电路是改造和提升传统产业的核心技术。

随着全球信息化、网络化和知识经济浪潮的到来,集成电路产业的地位越来越重要,它已成为事关国民经济、国防建设、人民生活和信息安全的基础性、战略性产业。

集成电路有两种。

一种是模拟集成电路。

另一种是数字集成电路。

本论文讲的是数字集成电路版图设计的基本知识。

然而在数字集成电路中CMOS与非门的制作是非常重要的。

二、CMOS二输入与非门的设计准备工作1.CMOS二输入与非门的基本构成电路使用S-Edit绘制的CMOS与非门电路如图1。

图1 基本的CMOS二输入与非门电路2.计算相关参数所谓与非门的等效反相器设计,实际上就是根据晶体管的串并联关系,再根据等效反相器中的相应晶体管的尺寸,直接获得与非门中各晶体管的尺寸的设计方法。

具体方法是:将与非门中的VT3和VT4的串联结构等效为反相器中的NMOS 晶体管,将并联的VT 1、VT 2等效PMOS 的宽长比(W/L)n 和(W/L)p 以后,考虑到VT3和VT4是串联结构,为保持下降时间不变,VT 3和VT 4的等线电阻必须减小为一半,即他们的宽长比必须为反相器中的NMOS 的宽长比增加一倍,由此得到(W/L)VT3,VT4=2(W/L)N 。

因为考虑到二输入与非门的输入端IN A 和IN B 只要有一个为低电平,与非门输出就为高电平的实际情况,为保证在这种情况下仍能获得所需的上升时间,要求VT 1和VT 2的宽长比与反相其中的PMOS 相同,即(W/L)VT1,VT2=(W/L)P 。

至此,根据得到的等效反向器的晶体管尺寸,就可以直接获得与非门中各晶体管的尺寸。

如下图所示为t PHL 和t PLH ,分别为从高到低和从低到高的传输延时,通过反相器的输入和输出电压波形如图所示。

集成电路工程课程设置方案

集成电路工程课程设置方案一、课程背景随着科技的不断发展,集成电路技术作为电子信息领域的重要分支,正在迅速发展和广泛应用。

因此,对集成电路工程专业的学生进行系统、全面的培养,不仅符合社会需求,也为学生未来的发展奠定了坚实的基础。

本方案是针对集成电路工程专业的课程设置方案,致力于为学生提供一种系统、全面的学习方式,使他们能够全面地掌握集成电路工程技术,并在未来的工作中能够胜任相关的工作。

二、课程目标集成电路工程课程设置的目标是培养具备扎实的电子信息专业知识和技能、掌握集成电路设计及制造的基本理论和方法、具备较强的工程实践能力、适应信息技术领域不断发展和变化的能力、具备研究和解决专业问题的能力和创新意识的专业化高级工程技术人才。

三、课程内容(一)基础课程1、数字电路与逻辑设计2、模拟电路原理3、电磁场与电磁波4、信号与系统5、微电子学6、半导体物理基础课程主要是为了为学生打下坚实的理论基础,使学生能够全面地掌握电子信息领域的基本知识,为进一步的集成电路工程学习打下坚实的基础。

(二)专业课程1、集成电路原理与设计2、模拟集成电路设计3、数字集成电路设计4、射频集成电路设计5、混合信号集成电路设计6、片上系统设计专业课程主要是针对集成电路工程的具体技术进行学习,结合实际案例和工程项目进行探讨和练习,使学生能够全面地掌握集成电路工程的核心知识和技能。

(三)实践课程1、电子设计竞赛2、电子电路仿真与实验3、电子产品设计与制作4、集成电路设计与制作实验5、电子信息项目实训实践课程的设置能够让学生在实际操作中更好地理解和掌握所学的知识,培养学生的动手操作能力和实际项目管理能力,为学生以后从事相关工作提供宝贵的实践经验。

四、教学方法采用理论教学、实验教学、实习与实训和综合设计教学相结合的教学方法。

1、理论教学在传授集成电路工程相关理论知识的同时,注重培养学生的独立分析和解决问题的能力,提高其专业技能。

2、实验教学通过实验教学使学生对所学理论知识有更深刻的理解和掌握,并培养其动手能力及实际操作能力。

集成电路综合课程设计

课程设计开课学期:2013-2014学年第一学期课程名称:集成电路综合课程设计学院:专业:班级:学号:姓名:任课教师:2013 年9 月11 日一、课程设计目的 (3)二、设计要求 (3) (3)三、设计基本原理 (3)四、设计设计分析 (4)五,设计实现过程 (5)A.电路设计 (5)B.综合过程 ................................ 错误!未定义书签。

C.结果 ........................................ 错误!未定义书签。

五.总结及感想............................... 错误!未定义书签。

附件: ........................................................ 错误!未定义书签。

设计目的利用verilogHDL设计数字电路异步FIFO,通过对verilogHDL的学习,掌握一些基本的知识,本次课程设计的安排旨在提升学生的动手能力,加强大家对专业理论知识的理解和实际运用,加强大家的自学能力,为大家做毕业设计做很好的铺垫。

设计要求遵循RTL设计规则,利用VerilogHDL 设计数字电路异步FIFO.异步FIFO具有读写两个时钟,读时钟100MHz,写时钟50MHz。

RTL为可综合设计,需要考虑不同时钟领域的同步设计,具有空满标志产生逻辑,并且根据空满标志进行读写数据及读写使能等逻辑控制。

根据RTL设计,编写验证环境,即testbench,在testbench中测试异步FIFO 的读写功能是否正确。

异步FIFO写数据由testbench产生。

编写一定的测试向量,来测试覆盖所设计的异步FIFO各项功能及指标。

将异步FIFO RTL在DC环境中进行综合,编写约束文件,给出最终的综合结果,包括面积报告,网表及时序报告。

约束文件中,读写时钟要求见上,输入延迟为写时钟周期的一半,输出延迟为读时钟周期的1/3,其他约束要求根据RTL设计自己确定。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

集成电路课程设计报告设计课题: 数字电子钟的设计姓名:专业: 电子信息工程学号:日期 20 年月日——20 年月日指导教师:国立华侨大学信息科学与工程学院目录1.设计的任务与要求 (1)2.方案论证与选择 (1)3.单元电路的设计和元器件的选择 (5)3.1 六进制电路的设计 (6)3.2 十进制计数电路的设计 (6)3.3 六十进制计数电路的设计 (6)3.4双六十进制计数电路的设计 (7)3.5时间计数电路的设计 (8)3.6 校正电路的设计 (8)3.7 时钟电路的设计 (8)3.8 整点报时电路的设计 (9)3.9 主要元器件的选择 (10)4.系统电路总图及原理 (10)5.经验体会 (10)参考文献 (11)附录A:系统电路原理图 (12)数字电子钟的设计1. 设计的任务与要求数字钟是一种…。

此次设计数字钟就是为了了解数字钟的原理,从而学会制作数字钟。

而且通过数字钟的制作进一步了解…。

1.1设计指标1. 时间以12小时为一个周期;2. 显示时、分、秒;3. 具有校时功能,可以分别对时及分进行单独校时,使其校正到标准时间;4. 计时过程具有报时功能,当时间到达整点前10秒进行蜂鸣报时;5. 为了保证计时的稳定及准确须由晶体振荡器提供表针时间基准信号。

1.2 设计要求1. 画出电路原理图(或仿真电路图);2. 元器件及参数选择(或开发板的考虑);3. 编写设计报告,写出设计的全过程,附上有关资料和图纸(也可直接写在相关章节中),有心得体会。

2. 方案论证与选择2.1 数字钟的系统方案数字钟实际上是…图1 数字电子钟方案框图2.2 晶体振荡器电路晶体振荡器电路给数字钟提供一个频率稳定准确的32768H Z的方波信号,可保证数字钟的走时准确及稳定。

…2.3 时间计数电路一般采用…2.4 译码驱动及显示单元电路选择CD4511作为显示译码电路…2.5 校时电路…3. 单元电路的设计与元器件选择数字钟从原理上讲是一种典型的数字电路,可以由许多中小规模集成电路组成,所以可以分成许多独立的电路。

3.1 六进制电路的设计由…组成,电路如图8。

图8 六进制电路3.2 十进制电路的设计…3.3 六十进制电路的设计…3.9主要元器件的选择1.共阴八段数码管6个;2.…4. 系统电路总图及原理将设计的各个单元电路进行级联,得到数字电子钟系统电路原理图如下(或见附录A)。

5.经验体会通过这次对数字电子钟的设计制作,让我…参考文献:[1] 赵建领. 51系列单片机开发宝典[M]. 北京: 电子工业出版社, 2007.[2] 边春元等. C51单片机典型模块设计及应用[M]. 北京: 机械工业出版社,2008.[3] 彭为等. 单片机典型系统设计实例精讲[M]. 北京: 电子工业出版社, 2006.[4] 徐爱钧等. Keil C51 V7.0单片机高级语言编程与μVision2应用实践[M].北京:电子工业出版社,2008.[5] 李朝青. 单片机&DSP外围数字IC技术手册(第2版)[M]. 北京:北京航空航天大学出版社,2005.[6] 中国电子网. .[7] 51单片机学习网. http://www.51bs51 .com.[8] 电子电路图网..[9] 周志敏等. 集成稳压电源电路图集[M]. 北京: 中国电力出版社, 2008.[10] 楼然苗等.单片机课程设计指导[M].北京:北京航空航天大学出版社,2007[11] 高吉祥.全国大学生电子设计竞赛培训系列教程——数字系统与自动控制系统设计[M].北京:电子工业出版社,2007.[12] 全国大学生电子设计竞赛委员会.全国大学生电子设计竞赛获奖作品选编(2005)[M].北京:北京理工大学出版社,2007[13] 黄智伟等.全国大学生电子设计竞赛系统设计[M].北京.北京航空航天大学出版社,2008.[14] 闻新等. MCS-51/52单片机原理与应用[M].北京.科学出版社,2008.附录A:系统电路原理总图全定制课程设计部分参考文献:---------------------------------Digital部分-----------------------------★专题1和专题2 :14位电流舵DAC解码电路AND 14位电流舵DAC电流源设计【1】Hiroyuki Kohno, Y asuyuki Nakamura, Atsuhito Kondo, "A350-MSh 3.34 8-bit CMOS D/A Converter Using a Delayed Driving Scheme",IEEE CUSTOM INTEGRA TED CIRCUITS CONFERENCE,pp 211-214,1995【2】Jose Bastos, Augusto M. Marques, Michel S. J. Steyaert,"A12-Bit Intrinsic Accuracy High-Speed CMOS DAC", IEEE JOURNAL OF SOLID-STA TE CIRCUITS, pp 1959-1969,VOL. 33, NO. 12, DECEMBER 1998【3】Geert A. M. V an der Plas,Jan V andenbussche,Willy Sansen etc,"A 14-bit Intrinsic Accuracy Q^2 Random Walk CMOS DAC",IEEE JOURNAL OF SOLID-STA TE CIRCUITS, pp 1708-1718,VOL. 34, NO. 12, DECEMBER 1999【4】John Hyde,Todd Humes,Chris Diorio,Mike Thomas,Miguel Figueroa,"A 300-MS/s 14-bit Digital-to-Analog Converter in Logic CMOS",IEEE JOURNAL OF SOLID-STA TE CIRCUITS,pp 734-740, VOL. 38, NO. 5, MAY 2003【5】K. Ola Andersson,J. Jacob Wikner,Dept. of E.E,"Characterization of a CMOS Current-SteeringDAC using State-Space Models", IEEE JOURNAL OF SOLID-STA TE CIRCUITS,pp 100-104. 【6】Miquel Albiol, José Luis González,Eduard Alarcón,"Mismatch and Dynamic Modeling of Current Sources in Current Steering CMOS DA Converters An Extended Design Procedure", IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: REGULAR PAPERS,pp 159-169,VOL. 51, NO. 1, JANUARY 2004【7】Brandon Greenley, Raymond V eith, Dong-Y oung Chang, and Un-Ku Moon,"A Low-V oltage 10-Bit CMOS DAC in 0.01-mm2 Die Area",IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—II: EXPRESS BRIEFS,pp 246-250, VOL. 52, NO. 5, MAY 2005.【8】王日炎, CMOS电流舵数模转换器的研究与设计, 硕士毕业论文,2009-07★专题3 :晶体振荡器(32.768KHz)【1】雷金,监铭,邹雪城,付先成, 高精度高性能晶体振荡器电路, 华中科技大学学报(自然科学版),2006,34 (5):56-58【2】陈曙,刘三清,张奇,陈晓飞, CMOS 石英晶体振荡器的设计与实现,电子工程师,2004,30(1):30-33★专题4 :Baugh-Wooley乘法器(8位)1】姚若河,欧秀平,数字阵列乘法器的算法及结构分析,计算机应用研究,2006.26(2):107-112 【2】王田,陈健,付宇卓,一种32位全定制高速乘法器设计,小型微型计算机系统,2005.26(2):307-【3】应征,吴金,常昌远,魏同立,高速乘法器的性能比较,电子器件,2006.26(1):42-45. 3★专题5 16位超前进位CMOS加法器【1】李嘉,蒋林,性能改进的16位超前进位加法器,现代电子技术,2007,22(4):172-175 【2】杨银堂,徐阳扬,周端,弥晓华, 西安电子科技大学学报(自然科学版),2009,36(1):30-38★专题6 :16位二进制转BCD码电路【1】邬杨波,胡建平,李宏, 一种BIN 码与BCD 码转换电路的设计与实现,信息技术,2005,28(8):33-35【2】王迎春,吉利久, 一种基于简单移位的二—十进制相互转换算法[J],电子学报,2003,31(2):40-44【3】邓勇,刘琪,智能仪表多字节二进制数转换BCD码,电子产品世界, 1999,23(12):20-24 【4】陈龙,樊晓桠,BCD码和二进制码转换的硬件实现,微电子学与计算机,2005,12(4):110-115★专题7 :8位进位旁路CMOS加法器【1】靳战鹏,高速浮点加法运算单元的研究与实现,西北工业大学,2006【2】何伟,设计高性能浮点加法器,合肥工业大学,2004★专题8 :SRAM CMOS电路(16Kx8)【1】李天阳,高速低功耗4M Bits SRAM的设计与研究,江南大学,2006【2】叶菁华,陈一辉,郭淦,洪志良.一种512Kbit同步高速SRAM的设计,固体电子学研究与进展,2004,(03)【3】Applications Note, uderstanding RAM Operation,IBM【4】良奇,通用存储器控制器VLSI设计关键技术的研究与实现,国防科学技术大学,2005★专题9 :DRAM CMOS电路(4Kx8)参考资料同专题8★专题10 :CMOS桶形移位寄存器(16x8)【1】李强,杨雪飞,杨青松,程君侠,一种高性能32位移位寄存器单元的设计,半导体技术,2003, 12(7):22-26【2】于学荣,戴紫彬,可重构移位单元的设计与实现,微计算机信息,2007, 13(6):22-28★专题11 :8:1MUX(采用多米诺CMOS电路)【1】范军,张宏,张宏庆,沈桂芬,动态CMOS多米诺逻辑电路的研究,辽宁大学学报(自然科学版),2005,3【2】汪金辉,宫娜,侯立刚,吴武臣,董利民,低功耗、高性能多米诺电路电荷自补偿技术,半导体学报,2008, 25(7)【3】汪金辉,宫娜,冯守博,段丽莹,侯立刚,吴武臣,董利民. 亚65nm工艺新型p结构多米诺与门设计,半导体学报, 2007,(11)【4】旭光,毛志刚,来逢昌,用于高速运算单元的时钟延迟动态多米诺逻辑电路的设计,微处理机,2002, 12(4)【5】小飞,王敦惠,陈迪平,单相时钟动态CMOS反相器分析与高速动态器件设计, 无线电工程,2003,(02)★专题12 :16位BCD码转二进制码电路【1】邬杨波,胡建平,李宏, 一种BIN 码与BCD 码转换电路的设计与实现,信息技术,2005,28(8):33-35【2】王迎春,吉利久, 一种基于简单移位的二—十进制相互转换算法[J],电子学报,2003,31(2):40-44【3】邓勇,刘琪,智能仪表多字节二进制数转换BCD码,电子产品世界, 1999,23(12):20-24 【4】陈龙,樊晓桠,BCD码和二进制码转换的硬件实现,微电子学与计算机,2005,12(4):110-115★专题13 :16位串并转换CMOS电路【1】张健忠,常昌远, 树型结构串并转换电路的设计,电子与封装,2007, 7(10)【2】孙玲,陈海进, 0.6μm CMOS工艺串行接口电路设计,南通大学学报(自然科学版)【3】尤扬,陈岚,一种应用于8B/10B编码串并转换电路的低功耗LVDS接收器设计,电子器件,2008,31(3):33-38【4】Rarnin Farjad-Rad.Ng Hiok-Tiaq.Edward Lee M J 0.622-8.0Gbps 150row Serial IO Macrocell with Fully Flexible Preemphasis and Equalization 2003【5】Ker Ming-Dou.Wu Chien-Hua Design on LVDSReceiver with New Delay-Selecting Technique for UXGA Flat Panel DisplayApplications 2006【6】Lee M J Edward.Dally W J.Farjad-Rad R CMOS HighSpeed I/Os-Present and Future 2003 ★专题14 :V erilog-A运算放大器建模【1】V erilogA教程【2】基于V erilogA行为描述模型的PLL系统设计★专题15 :16位并串转换CMOS电路【1】张健忠,常昌远, 树型结构串并转换电路的设计,电子与封装,2007, 7(10)【2】孙玲,陈海进, 0.6μm CMOS工艺串行接口电路设计,南通大学学报(自然科学版)【3】尤扬,陈岚,一种应用于8B/10B编码串并转换电路的低功耗LVDS接收器设计,电子器件,2008,31(3):33-38【4】Rarnin Farjad-Rad.Ng Hiok-Tiaq.Edward Lee M J 0.622-8.0Gbps 150row Serial IO Macrocell with Fully Flexible Preemphasis and Equalization 2003【5】Ker Ming-Dou.Wu Chien-Hua Design on LVDSReceiver with New Delay-Selecting Technique for UXGA Flat Panel DisplayApplications 2006【6】Lee M J Edward.Dally W J.Farjad-Rad R CMOS HighSpeed I/Os-Present and Future 2003 -----------------------------------Analog部分--------------------------------★专题16:带隙基准电压源设计【1】拉扎维著. 陈贵灿译. 模拟CMOS集成电路设计. 西安交通大学出版社. 第一版.第十一章带隙基准. PP309-327【说明】带隙基准电压源的参考文献比较多,这里限制一下我们设计的是一款工作电压范围在2.5-5.5V,带运放反馈的带隙基准电压源电路。