数字电路 第11章

数字电路知识点汇总(精华版)[2]

![数字电路知识点汇总(精华版)[2]](https://img.taocdn.com/s3/m/cdc71ee2de80d4d8d05a4f72.png)

(直打版)数字电路知识点汇总(精华版)(word版可编辑修改)编辑整理:尊敬的读者朋友们:这里是精品文档编辑中心,本文档内容是由我和我的同事精心编辑整理后发布的,发布之前我们对文中内容进行仔细校对,但是难免会有疏漏的地方,但是任然希望((直打版)数字电路知识点汇总(精华版)(word版可编辑修改))的内容能够给您的工作和学习带来便利。

同时也真诚的希望收到您的建议和反馈,这将是我们进步的源泉,前进的动力。

本文可编辑可修改,如果觉得对您有帮助请收藏以便随时查阅,最后祝您生活愉快业绩进步,以下为(直打版)数字电路知识点汇总(精华版)(word版可编辑修改)的全部内容。

数字电路知识点汇总(东南大学)第1章数字逻辑概论一、进位计数制1。

十进制与二进制数的转换2.二进制数与十进制数的转换3。

二进制数与16进制数的转换二、基本逻辑门电路第2章逻辑代数表示逻辑函数的方法,归纳起来有:真值表,函数表达式,卡诺图,逻辑图及波形图等几种。

一、逻辑代数的基本公式和常用公式1)常量与变量的关系A+0=A与A=⋅1AA+1=1与0⋅A0=A⋅=0AA+=1与A2)与普通代数相运算规律a.交换律:A+B=B+AA⋅⋅=ABBb。

结合律:(A+B)+C=A+(B+C)A⋅BC⋅⋅=⋅)A()B(Cc。

分配律:)⋅=+A⋅(CBA⋅A C⋅BA+++)B⋅=A)())(CABC3)逻辑函数的特殊规律a。

同一律:A+A+Ab.摩根定律:BA+B⋅A=ABA⋅=+,Bb。

关于否定的性质A=A二、逻辑函数的基本规则代入规则在任何一个逻辑等式中,如果将等式两边同时出现某一变量A的地方,都用一个函数L表示,则等式仍然成立,这个规则称为代入规则例如:C⋅⊕⋅A⊕+ACBB可令L=CB⊕则上式变成L⋅=C+AA⋅L=⊕⊕A⊕BAL三、逻辑函数的:——公式化简法公式化简法就是利用逻辑函数的基本公式和常用公式化简逻辑函数,通常,我们将逻辑函数化简为最简的与-或表达式1)合并项法:利用A+1=⋅=A=⋅,将二项合并为一项,合并时可消去一个变BA或ABA+A量例如:L=B A+BA=(C+)=ACABCCB2)吸收法利用公式A⋅+,消去多余的积项,根据代入规则BA⋅可以是任何一A=BA个复杂的逻辑式例如化简函数L=E B+AB+DA解:先用摩根定理展开:AB=BA+再用吸收法L=E BDAB++A=E B+A++BDA=)A+A+D+(E()BB=)AA+++DB1(B)1(E=BA+3)消去法利用BA++消去多余的因子=ABA例如,化简函数L=ABCBA++A+BEAB解:L=ABCA+++ABEABB=)BAA++B+)((ABCBAE=)BBA+++AE)((BCB=)BCBA++B+++A)(()((C)BBB=)BA++C+A()(CB=ACA++B+ABCA=C+A+BBA4)配项法利用公式C⋅+=++⋅⋅将某一项乘以(AA⋅BAABCACBA+),即乘以1,然后将其折成几项,再与其它项合并。

集成电路设计基础第11章数字集成vlsi系统设计基础

通过对时序逻辑电路的输入、输出及状态进行分析,了解其工作原理和特性。

时序逻辑电路设计

根据实际需求,选用合适的触发器和组合逻辑电路,设计出满足特定功能的时序逻辑电路。同时 需要考虑时序问题,确保电路的正确性和稳定性。

03

数字集成VLSI系统关键技术

高性能计算技术

并行处理技术

通过多核处理器、GPU加速等技术提高计算能力。

逻辑综合

将HDL代码转换为门级网表,优化电路性能并降低功 耗。

布局布线

根据电路需求和工艺要求,将门级网映射到具体的 芯片上,实现电路的物理实现。

时序分析

对布局布线后的电路进行时序分析,确保电路时序的 正确性和性能。

仿真验证与测试方法

前仿真

在电路设计阶段进行仿真验证, 检查电路功能和性能是否符合设 计要求。

THANKS

感谢观看

集成电路设计基础第11章数 字集成vlsi系统设计基础

• 数字集成VLSI系统概述 • 数字集成VLSI系统基本原理 • 数字集成VLSI系统关键技术 • 数字集成VLSI系统实现方法

• 数字集成VLSI系统应用实例 • 数字集成VLSI系统前沿研究动态

01

数字集成VLSI系统概述

定义与发展历程

柔性电子在数字集成VLSI中潜在价值

柔性电子器件

利用柔性基底和可弯曲的电 子材料制造柔性电子器件, 实现可穿戴、可折叠的数字

集成VLSI系统。

生物兼容性

柔性电子具有良好的生物兼 容性,可用于生物医学应用 中与人体紧密接触的电子设

备。

轻量化与便携性

柔性电子器件具有轻量化、 薄型化和可弯曲的特点,便 于携带和集成到各种移动设 备中。

应用领域及市场需求

第11章 数字电路综合案例

第11章数字电路综合案例内容提要前面的章节介绍了数字电路的基本知识、基本理论、常用器件,以及数字电路分析和设计的基本方法。

本章涉及到复杂数字系统的设计。

数设计对象从译码器、计数器等这些基本逻辑功能电路到了数字钟等综合的数字逻辑系统的设计;设计方法也由采用真值表到求逻辑表达式、画出电路图的方式到通过确定总体方案,采取从局部到整体,用各种中、大规模集成电路来满足要求的数字电路系统的方式。

本章结合数字钟这一实际的案例来介绍数字电路系统的设计方法,进一步提高学生的综合能力和解决实际问题的能力。

基本教学要求1.了解中小规模集成电路的作用及实用方法。

2.了解数字钟电路的原理。

3.掌握综合数字电路系统的设计流程和设计方法。

11.1概述数字系统的设计,采用从整体到局部,再从局部到整理的设计方法。

首先对系统的目标、任务、指标要求等进行分析,确定系统的总体方案;然后把系统的总体方案分成若干功能部件,绘出系统的方框图;之后运用数字电路的分析和设计方法分别进行设计,或者是直接选用集成器件去构成功能部件;最后把这些功能部件连接组合起来,便构成了完整的数字系统,通过对电路的分析和测试修改,完善与优化整个系统。

这是传统的数字系统的设计方法,也是下面要介绍的内容。

随着计算机技术的发展,电子设计自动化EDA成为了现代电子系统设计与仿真的重要手段,对于复杂系统的设计十分有效,尤其是硬件描述语言的使用,使硬件软件化,让数字系统的设计更加方便、高效。

下面以数字钟系统设计为例,介绍综合数字电路系统的设计方法。

数字钟是一种用数字电子技术实现时、分、秒计时的装置,与传统的机械式时钟相比具准确、直观、寿命长等特点。

目前广泛用于个人家庭以及车站、码头、剧场、办公室等公共场所,给人们的生活、学习、工作、娱乐带来极大的方便。

数字钟也是一种典型的数字电路,其中包括了组合逻辑电路和时序逻辑电路。

通过数字钟的设计进一步了解数字系统设计时用到的中小规模集成电路的使用方法,进一步学习与掌握各种组合逻辑电路与时序电路的原理与使用方法。

数字电路逻辑设计(第二版) 王毓银 电子科技大学

3.5.4 CMOS逻辑门电路

3.5.5 BiCMOS门电路

3.5.6 CMOS电路的正确使用方法

3.6 VHDL描述逻辑门电路

3.6.1 VHDL描述电路的基本方法

3.6.2 VHDL描述逻辑门电路

习题

第4章 组合逻辑电路

4.1 组合逻辑电路分析

6.4.1 设计给定序列信号的产生电路

6.4.2 根据序列循环长度M的要求设计发生器电路

6.5 时序逻辑电路的VHDL描述

6.5.1 移位寄存器的VHDL描述

6.5.2 计数器的VHDL描述

习题

第7章 半导体存储器

7.1 概述

7.1.1 半导体存储器的特点与应用

5.3 主从触发器

5.3.1 主从触发器基本原理

5.3.2 主从J-K触发器主触发器的一次翻转现象

5.3.3 主从J-K触发器集成单元

5.3.4 集成主从J-K触发器的脉冲工作特性

5.4 边沿触发器

5.4.1 维持一阻塞触发器

5.4.2 下降沿触发的边沿触发器

10.2.6 DAC的转换精度与转换速度

10.3 模数转换器(ADC)

10.3.1 模数转换基本原理

10.3.2 并联比较型ADC

10.3.3 逐次逼近型ADC

10.3.4 双积分型ADC

10.4 集成ADC及其应用举例

双积分型集成ADC

10.4.2 逐次逼近型集成ADC

2.1.3 真值表与逻辑函数

2.1.4 逻辑函数相等

2.1.5 三个规则

2.1.6 常用公式

2.1.7 逻辑函数的标准形式

VerilogHDL数字系统设计——原理、实例及仿真作者康磊第8-13章第11章

4

冯· 诺依曼结构的处理器使用同一个存储器,经由同一个 总线传输,具有以下特点: (1) 结构上由运算器、控制器、存储器和输入/输出设备 组成。 (2) 存储器是按地址访问的,每个地址是唯一的。 (3) 指令和数据都是以二进制形式存储的。 (4) 指令按顺序执行,即一般按照指令在存储器存放的顺 序执行,程序的分支由转移指令实现。

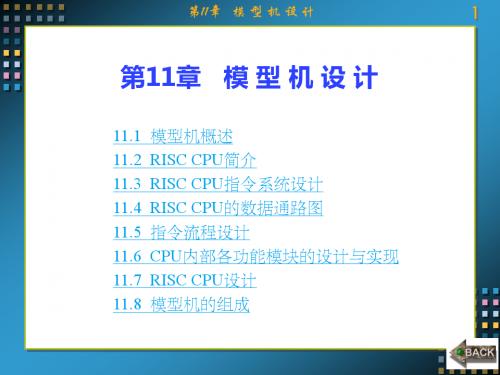

第11章 模 型 机 设 计

2

教材其余课件及动画素材请查阅在线教务辅导网 在线教务辅导网:

QQ址:

第11章 模 型 机 设 计

3

11.1 模 型 机 概 述

第11章 模 型 机 设 计

1

第11章 模 型 机 设 计

11.1 11.2 11.3 11.4 11.5 11.6 11.7 11.8 模型机概述 RISC CPU简介 RISC CPU指令系统设计 RISC CPU的数据通路图 指令流程设计 CPU内部各功能模块的设计与实现 RISC CPU设计 模型机的组成

(5) 以运算器为中心,在输入输出设备与存储器之间的数

据传送都途经运算器。运算器、存储器、输入输出设备的操 作以及它们之间的联系都由控制器集中控制。

第11章 模 型 机 设 计

5

哈佛结构使用两个独立的存储器模块,分别存储指令和 数据,并具有一条独立的地址总线和一条独立的数据总线, 具有以下特点: (1) 每个存储模块都不允许指令和数据并存,以便实现并 行处理。

CPU是计算机系统中最为重要的组成部分,它在计算机

系统中负责信息的处理和控制,因而被人们称为计算机的大 脑。CPU和外围设备构成计算机。模型机是一个简单的计算 机硬件系统,可以实现计算机的基本功能。 计算机的体系结构可分为两种类型:冯· 诺依曼结构和哈 佛结构。大多数CPU采用冯· 诺依曼结构。

《数字电路-分析与设计》1--10章习题及解答(部分)_北京理工大学出版社

6-17先分别将‘290接为8421和5421计数器,再分别用M-1=6(QDQCQBQA=0110)8421和(QAQDQCQB=1001)5421置位即可,应特别注意高低位的顺序。波形图和状态图略。

低电平噪声容限:

甲的关门电平大,所以甲在输入低电平时的

抗干扰能力强。

3-6 试说明下列各种门电路中哪些可以将输出端并联使用(输入端的状态不一定相同)。

⑴ 具有推拉式输出级的TTL电路;

⑵ TTL电路的OCபைடு நூலகம்;

⑶ TTL电路的TS门;

⑷ 普通的CMOS门;

⑸ 漏极开路输出的CMOS门;

⑹ CMOS电路的TS门。

6-24应从RCO引出,此时不管分频比为多少,分频关系都是正确的。

6-25画出状态顺序表或状态图即可。

对于图(a),只要注意QB=0时预置,并且DCBA=QD110即可。

由状态图知,这是模6计数器。

对于图(b),只要注意QC=0时预置,并且DCBA=QD100即可。

由状态图知,这是模10计数器。

该电路设计巧妙,QD均为占空比为50%的方波。

3-5 有两个相同型号的TTL“与非”门,对它们进行测试的结果如下:

⑴ 甲的开门电平为1.4V,乙的开门电平为1.5V;

⑵ 甲的关门电平为1.0V,乙的关门电平为0.9V。

试问在输入相同高电平时,哪个抗干扰能力强?在输入相同的低电平时,哪个抗干扰能力强?

解:高电平噪声容限:

甲的开门电平小,所以甲在输入高电平时的抗干扰能力强;

电工学2第11章组合逻辑电路

分析 逻辑图 设计 功能

已知函数的逻辑图如图所示, 例 : 已知函数的逻辑图如图所示,试求它的逻辑 函数式。 函数式。 从输入端A、 解: 从输入端 、 B开始逐个写出每 开始逐个写出每 个图形符号输出端 的逻辑式,即得: 的逻辑式,即得:

Y = A+ B+ A+ B

Y = A + B + A + B = ( A + B)( A + B) = ( A + B)( A + B)

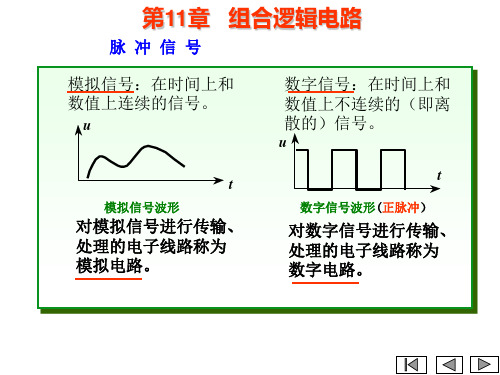

第11章 组合逻辑电路 11章

脉 冲 信 号 模拟信号:在时间上和 数值上连续的信号。

u

数字信号:在时间上和 数值上不连续的(即离 散的)信号。

u t

数字信号波形(正脉冲) 数字信号波形(正脉冲)

t

模拟信号波形

对模拟信号进行传输、 对模拟信号进行传输、 处理的电子线路称为 模拟电路。 模拟电路。

对数字信号进行传输、 对数字信号进行传输、 处理的电子线路称为 数字电路。 数字电路。

数字电路的分类

按半导体类型可分为: a、按半导体类型可分为: 双极型电路和单极型电路 按半导体类型可分为 b、按电路的集成度可分为: 按电路的集成度可分为: 按电路的集成度可分为 SSI(Small Scale Integrated )电路 数十器件 片) 电路(数十器件 电路 数十器件/片 MSI(Medium Scale Integrated)电路 数百器件 片) 电路(数百器件 电路 数百器件/片 LSI(Large Scale Integrated )电路 数千器件 片) 电路(数千器件 电路 数千器件/片 VLSI (Very Large Scale Integrated )电路 数万器件 片) 电路(数万器件 电路 数万器件/片 ASIC(Application Specific Integrated Circuit,专用集成电路) CPLD(Complex Programmable Logic Device,复杂可编程逻辑器件 ) FPGA(Filed Programmable Gate Array,现场可编程门阵列 ) IP核(Intellectual Property,知识产权) 硬件设计包 SoC(System on a Chip,单片电子系统) CPLD/FPGA—可编程专用IC,或可编程ASIC。 EDA(Electronic Design Automation,电子设计自动化)

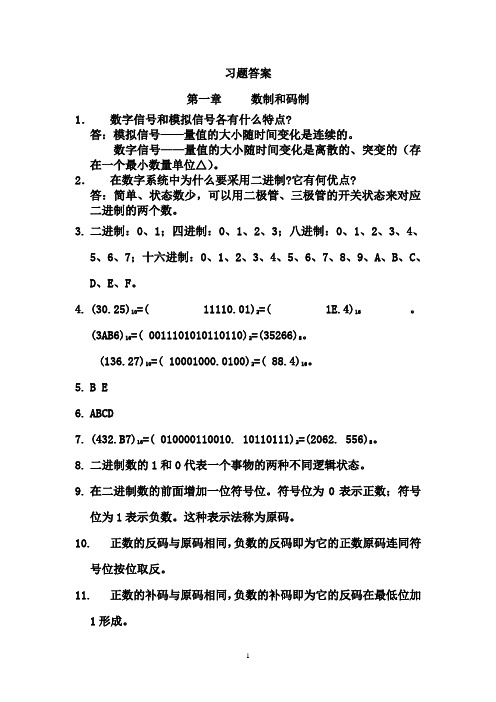

数字电子技术习题答案

习题答案第一章数制和码制1.数字信号和模拟信号各有什么特点?答:模拟信号——量值的大小随时间变化是连续的。

数字信号——量值的大小随时间变化是离散的、突变的(存在一个最小数量单位△)。

2.在数字系统中为什么要采用二进制?它有何优点?答:简单、状态数少,可以用二极管、三极管的开关状态来对应二进制的两个数。

3.二进制:0、1;四进制:0、1、2、3;八进制:0、1、2、3、4、5、6、7;十六进制:0、1、2、3、4、5、6、7、8、9、A、B、C、D、E、F。

4.(30.25)10=( 11110.01)2=( 1E.4)16。

(3AB6)16=( 0011101010110110)2=(35266)8。

(136.27)10=( 10001000.0100)2=( 88.4)16。

5.B E6.ABCD7.(432.B7)16=( 010*********. 10110111)2=(2062. 556)8。

8.二进制数的1和0代表一个事物的两种不同逻辑状态。

9.在二进制数的前面增加一位符号位。

符号位为0表示正数;符号位为1表示负数。

这种表示法称为原码。

10.正数的反码与原码相同,负数的反码即为它的正数原码连同符号位按位取反。

11.正数的补码与原码相同,负数的补码即为它的反码在最低位加1形成。

12.在二进制数的前面增加一位符号位。

符号位为0表示正数;符号位为1表示负数。

正数的反码、补码与原码相同,负数的反码即为它的正数原码连同符号位按位取反。

负数的补码即为它的反码在最低位加1形成。

补码再补是原码。

13.A:(+1011)2的反码、补码与原码均相同:01011;B: (-1101)2的原码为11101,反码为10010,补码为10011.14.A: (111011)2 的符号位为1,该数为负数,反码为100100,补码为100101. B: (001010)2 的符号位为0,该数为正,故反码、补码与原码均相同:001010.15.两个用补码表示的二进制数相加时,和的符号位是将两个加数的符号位和来自最高有效数字位的进位相加,舍弃产生的进位得到的结果就是和的符号。