DSP第二章

合集下载

DSP第二章5

其幅度谱和相位谱分别为

X (e j ) | sin 5 / 2 | , () 2 arg[ sin 5 / 2]

sin( / 2)

sin( / 2)

上午4时33分

11

其图形如下

上午4时33分

12

3 序列的傅立叶变换的性质

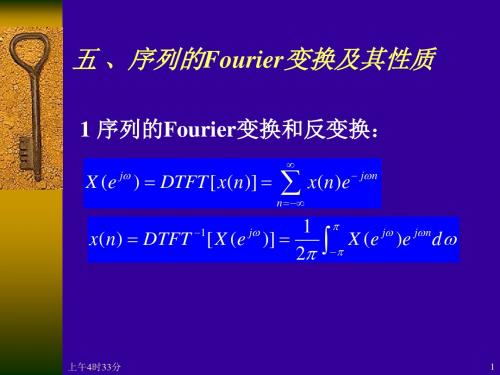

因序列的傅立叶变换是Z变换在 z 1 的单位圆上的特例,故所有Z变换的性 质对傅立叶变换都成立。

2

若序列x(n)绝对可和,即

x(n)e jn x(n)

n

n

则其Fourier变换X (e j ) 存在且连续,是 序列的z变换在单位圆上的值:

X (e j ) X (z) ze j

x(n)e jn

n

上午4时33分

3

若序列的Fourier变换 X (e j )存在且连续, 且是其z变换在单位圆上的值,则序列 x(n)一定绝对可和,将 X (e j ) 展成Fourier 级数,其系数即为x(n):

x(n)e jn

4

e jn

n

n0

1 e j5 1 e j

j 5 j 5

j 5

e

2 (e 2

j j

e 2 )

j

e 2 (e 2 e 2 )

e

j 2

sin 5

2

sin 25 Nhomakorabea 2 k

k为整数

2 k

上午4时33分

25

2-10 设 X e j 是如图所示的 x n 信号的傅 里叶变换,不必求出 X e j ,试完成下列

计算:

(1) X e j0

2-DSP原理与应用2010-第二章

浮点运算指令 汇编程序设计:

生成可执行代码过程 示例文件

DSP原理与应用 2013年8月5日 6

第2.2.1累加,算术计算和逻辑运算

DSP计算和逻辑运算

DSP原理与应用

2013年8月5日

8

第2.2.1累加,算术计算和逻辑运算

DSP原理与应用

浮点数简介(IEEE754)

IEEE754-IEEE Standard 754 for Binary Floating Point Arithmetic

单精度浮点数:1位符号位,8位指数,23位有效数 例:00111111 01100110 01100110 01100110 16进制为:0X3F666666 整形数为1063675494 单精度下:符号位0(+) 指数位E(01111110) 2=126,e=-1 尾数1100110 01100110011001102 1.799999952316284179687510

DSP原理与应用

The Technology & Applications of DSPs

北京交通大学 电气工程学院 夏明超 郝瑞祥 万庆祝 mchxia@ haorx@ qzhwan@

第二章:DSP系统开发

第2.1节 概述

第2.2节 DSP汇编语言概述及汇编程序设计 第2.3节 DSP C语言程序设计 第2.4节 DSP C与汇编混合编程 第2.5节 DSP程序烧写 习题

csmpasswds csm_rsvd

: > CSM_PWL PAGE = 0 : > CSM_RSVD PAGE = 0

/* Allocate uninitalized data sections: */ .stack : > RAMM1 PAGE = 1 .ebss : > RAML4 PAGE = 1 .esysmem : > RAMM1 PAGE = 1 …… } DSP原理与应用 2013年8月5日 32

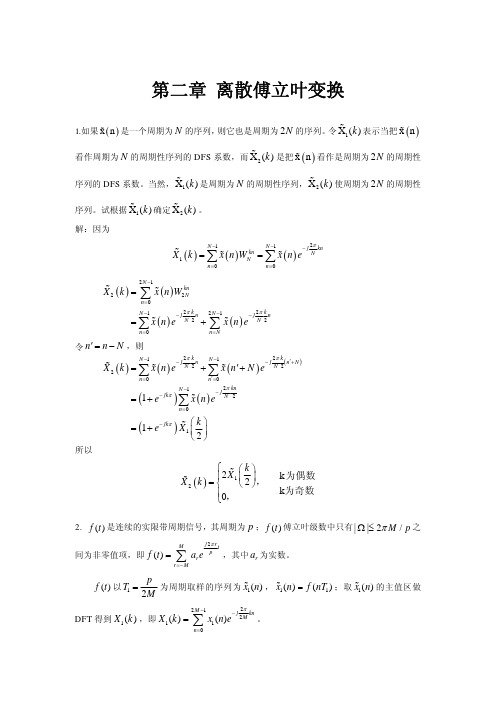

DSP第二章课后答案

k X 2

2 N 1 n 0

n W x

kn 2N 2 k n N 2 2 N 1 n N

n e x

n 0

N 1

j

n e x

j

2 k n N 2

令 n n N ,则

j k x n e N X 2 n 0 N 1 2 k n 2

k 0,1, 2 ,求 q (n) 。

y (n) x((n 4))6 4 (n 4) 3 (n 5) 2 (n) (n 1)

(b) X ( k ) 的实部是 Re X ( k )

1 X (k ) X (k ) ,又由 2

且 M r M ,所以

2 Mak X 1 (k ) 2 Mak 2 M 2 M ( a +a ) M M

而 X 2 (k )

4 M 1

n0

x2 (n)e

j

2 kn 4M

2 (n) f (nT2 ) f ( 将x

j 2 nr M np ) ar e 4 M 代入 X 2 (k ) 4M r M M 4 M 1 j 2 ( k r ) n 4M

x n r y1 n 0

n ir , i 0,..., N 1 others

求证 DFT y1 n 与X k 的关系。 (2)将长度扩大 r 倍(补 0 增长) ,得到一个长度为 rN 的有限长序列 y2 ( n)

x n 0 n N 1 y2 n N n rN 1 0

(k ) 是周期为 N 的周期性序列, X (k ) 使周期为 2 N 的周期性 序列的 DFS 系数。当然, X 1 2 (k ) 确定 X (k ) 。 序列。试根据 X 1 2

数字信号处理DSP第二章2z反变换

z1

4n

4

15 2021/4/21

j Im[z]

C

1/ 4 0

4 Re[z]

5

当n 1时 F (z)在围线c内有一阶极点z 1 和-(n 1)阶极点z 0

4 而围线c外只有一阶极点z=4,且F(z)的分母多项式 阶次高于分子多项式阶次两次以上

x(n) Re s[F (z)]z4

z

4

解:X

z

1

5 z 1 z1 6z2

z2

5z z 6

5z

z 2z 3

X

z

z

z

5

2z

3

A1 z2

A2 z3

3

j Im[z]

2

0

Re[z]

A1

Res

X

z

zБайду номын сангаас

z2

z

2

z

5

2

z

3

z2

1

A2 Res

2021/4/21

X

z

z

z3

z

3

z

5

2

z

3

z 3

1

16

X z

1

1

z z2 z3

bi zi

i0 N

1 ai zi

i 1

X (z)

M N n0

Bn zn

A M r k

k1 1 zk z1

r k 1

Ck [1 zi z1]k

用留数定理求系数:

Ak

Re

s

X (z) z zzk

k 1,2,

,M r

2021/4/21

15

例:X (z)

DSP第二章频率响应11.14

2.6 离散系统的系统函数、 系统的频率响应

LSI系统的系统函数H(z):

单位抽样响应h(n)的z变换

H (z) ZT [h(n)] h(n)zn Y (z)

n

X (z)

其中:y(n)=x(n)*h(n) Y(z)=X(z)H(z)

系统的频率响应 H (e j ) : 单位圆上的系统函数 单位抽样响应h(n)的Fourier变换

y(n) 1 H (e j ) X (e j )e jnd

2

其中: x(n) 1 X (e j )e jnd

2 微分增量(复指数): 1 X (e j )e jnd

2

4、频率响应的几何确定法

利用H(z)在z平面上的零极点分布

M

(1 cm z1)

4

8

3

其中:x(n)数,指出系统的零极点;

2)若该系统是因果稳定的,指出系统的收敛域;

3)求该因果稳定系统的单位抽样响应。

解:1)对差分方程两边取z变换:

Y (z) 3 z1Y (z) 1 z2Y (z) X (z) 1 z1X (z)

4

8

1

, a,b为常数

(z a)( z b)

若要求系统因果稳定,则a的取值域为

____和 b的取值域为_____。

0≤|a|<1, 0≤|b|<1

6、序列的傅里叶变换等于序列在( ) 上的Z变换。

A.单位圆 B.实轴 C.正虚轴 D.负虚轴

A

7、下列哪一个单位抽样响应所表示的系 统不是因果系统?( )

j

2π N

k k

0,1, 2L

,N

1

频率响应的几何确定

LSI系统的系统函数H(z):

单位抽样响应h(n)的z变换

H (z) ZT [h(n)] h(n)zn Y (z)

n

X (z)

其中:y(n)=x(n)*h(n) Y(z)=X(z)H(z)

系统的频率响应 H (e j ) : 单位圆上的系统函数 单位抽样响应h(n)的Fourier变换

y(n) 1 H (e j ) X (e j )e jnd

2

其中: x(n) 1 X (e j )e jnd

2 微分增量(复指数): 1 X (e j )e jnd

2

4、频率响应的几何确定法

利用H(z)在z平面上的零极点分布

M

(1 cm z1)

4

8

3

其中:x(n)数,指出系统的零极点;

2)若该系统是因果稳定的,指出系统的收敛域;

3)求该因果稳定系统的单位抽样响应。

解:1)对差分方程两边取z变换:

Y (z) 3 z1Y (z) 1 z2Y (z) X (z) 1 z1X (z)

4

8

1

, a,b为常数

(z a)( z b)

若要求系统因果稳定,则a的取值域为

____和 b的取值域为_____。

0≤|a|<1, 0≤|b|<1

6、序列的傅里叶变换等于序列在( ) 上的Z变换。

A.单位圆 B.实轴 C.正虚轴 D.负虚轴

A

7、下列哪一个单位抽样响应所表示的系 统不是因果系统?( )

j

2π N

k k

0,1, 2L

,N

1

频率响应的几何确定

DSP原理与应用2012-第二章 DSP系统开发

DSP原理与应用 2012年9月4日 27

第2.2.8 浮点运算指令 寄存器操作

MOV16:16位浮点数内存操作 MOV32:32位浮点数内存操作 MOVD32:32位浮点数内存操作及复制 MOVF32:32位浮点数立即数内存操作 MOVI32:32位浮点数立即数( (16进制)内存操作 MOVIZ32.MOVIZF32:浮点寄存器高16位操作 MOVXI:浮点寄存器低16位操作 MOVST0:STF内容放至ST0

5

第2.2节 DSP汇编语言概述及汇编程序设计 汇编语言:

累加,算术计算和逻辑运算 辅助寄存器和数据页操作 TREG,PREG和乘法指令 直接内存访问指令(DMA)和IO操作指令 程序空间访问指令 跳转指令、寄存器操作指令

浮点运算指令 汇编程序设计:

生成可执行代码过程 示例文件

DSP原理与应用

2012年9月4日

14

第2.2.3 TREG,PREG , 和乘法指令

DSP原理与应用

2012年9月4日

15

第2.2.4直接内存访问 接内存访问( (DMA) )和IO操作指令

DSP原理与应用

2012年9月4日

16

第2.2.5程序空间访问指令

DSP原理与应用

2012年9月4日

17

DSP原理与应用

2012年9月4日

4

第二章 第 章:DSP系统开发

第2.1节 概述 第2.2节 DSP汇编语言概述及汇编程序设计 第2.3节 DSP C语言程序设计 第2.4 2 4节 DSP C与汇编混合编程 第2.5节 DSP程序烧写 习题

DSP原理与应用

2012年9月4日

实际值0.89999997615814208984375

第2.2.8 浮点运算指令 寄存器操作

MOV16:16位浮点数内存操作 MOV32:32位浮点数内存操作 MOVD32:32位浮点数内存操作及复制 MOVF32:32位浮点数立即数内存操作 MOVI32:32位浮点数立即数( (16进制)内存操作 MOVIZ32.MOVIZF32:浮点寄存器高16位操作 MOVXI:浮点寄存器低16位操作 MOVST0:STF内容放至ST0

5

第2.2节 DSP汇编语言概述及汇编程序设计 汇编语言:

累加,算术计算和逻辑运算 辅助寄存器和数据页操作 TREG,PREG和乘法指令 直接内存访问指令(DMA)和IO操作指令 程序空间访问指令 跳转指令、寄存器操作指令

浮点运算指令 汇编程序设计:

生成可执行代码过程 示例文件

DSP原理与应用

2012年9月4日

14

第2.2.3 TREG,PREG , 和乘法指令

DSP原理与应用

2012年9月4日

15

第2.2.4直接内存访问 接内存访问( (DMA) )和IO操作指令

DSP原理与应用

2012年9月4日

16

第2.2.5程序空间访问指令

DSP原理与应用

2012年9月4日

17

DSP原理与应用

2012年9月4日

4

第二章 第 章:DSP系统开发

第2.1节 概述 第2.2节 DSP汇编语言概述及汇编程序设计 第2.3节 DSP C语言程序设计 第2.4 2 4节 DSP C与汇编混合编程 第2.5节 DSP程序烧写 习题

DSP原理与应用

2012年9月4日

实际值0.89999997615814208984375

第2章 TMS320C55X系列DSP

C55X灵活的指令Cache(高速缓冲存储器)也可以对不同类 型的代码做优化配置。改善Cache的访问率,就意味着减少片 外的访问,从而减少系统的功耗。

14

(3) 外设和片上存储器阵列的自动低功率机制。C55X的核 处理器会自动地管理片上外设和存储器阵列的功耗。这种资源 的管理完全是自动的,对用户透明。而且,这种功耗的降低, 并不影响处理器的性能。当某个片上的存储器阵列没有被使用 时,它们就自动地切换到低功率模式。当一个访问的要求到达 时,该阵列就恢复到正常的工作状态,完成存储器的访问,无 须应用程序的干预。如果没有进一步的访问,该阵列又回到低 功率状态。该处理器对片上外设也提供类似的控制。当外设没 有激活,以及CPU不需要其关注时,就进入低功率状态。外设 响应处理器的要求,退出低功率状态,也不需要程序的干预。 这种功率管理也可以在软件的外设IDLE(闲置)域控制下进行。

13

(2) 将存储器的访问减到最少。存储器的访问,无论是片 内的还是片外的,都是功率消耗的主要部分。将存储器的访问 减到最少,无疑是降低每个任务功耗所必需的。在C55X里, 指令的提取是32 bit(C54X里是16 bit)。此外,可变长度指令集 意味着,每个32 bit指令的提取可以提出一个以上的长度可变 的指令,按照所需要的信息来决定指令的长度,从而改善代码 的密度。这种指令集的设计和处理器结构的结合,就可以保证 在达到最高性能的同时,使功耗降到最小。

C55X继承了C54X的发展趋势,低功耗、低成本,在有限 的功率条件下,保持最好的性能。其工作在0.9 V下,待机功 耗低至0.12 mW,性能高达600 MIPS,并且具有业界目前最低 的待机功耗,极大地延长了电池的寿命,对数字通信等便携式 应用所提出的挑战,提供了有效的解决方案。其软件也与所有 C5000 DSP兼容。与120 MHz的C54X相比,300 MHz的C55X性 能大约提高了5倍,而功耗则降为C54X的1/6。

14

(3) 外设和片上存储器阵列的自动低功率机制。C55X的核 处理器会自动地管理片上外设和存储器阵列的功耗。这种资源 的管理完全是自动的,对用户透明。而且,这种功耗的降低, 并不影响处理器的性能。当某个片上的存储器阵列没有被使用 时,它们就自动地切换到低功率模式。当一个访问的要求到达 时,该阵列就恢复到正常的工作状态,完成存储器的访问,无 须应用程序的干预。如果没有进一步的访问,该阵列又回到低 功率状态。该处理器对片上外设也提供类似的控制。当外设没 有激活,以及CPU不需要其关注时,就进入低功率状态。外设 响应处理器的要求,退出低功率状态,也不需要程序的干预。 这种功率管理也可以在软件的外设IDLE(闲置)域控制下进行。

13

(2) 将存储器的访问减到最少。存储器的访问,无论是片 内的还是片外的,都是功率消耗的主要部分。将存储器的访问 减到最少,无疑是降低每个任务功耗所必需的。在C55X里, 指令的提取是32 bit(C54X里是16 bit)。此外,可变长度指令集 意味着,每个32 bit指令的提取可以提出一个以上的长度可变 的指令,按照所需要的信息来决定指令的长度,从而改善代码 的密度。这种指令集的设计和处理器结构的结合,就可以保证 在达到最高性能的同时,使功耗降到最小。

C55X继承了C54X的发展趋势,低功耗、低成本,在有限 的功率条件下,保持最好的性能。其工作在0.9 V下,待机功 耗低至0.12 mW,性能高达600 MIPS,并且具有业界目前最低 的待机功耗,极大地延长了电池的寿命,对数字通信等便携式 应用所提出的挑战,提供了有效的解决方案。其软件也与所有 C5000 DSP兼容。与120 MHz的C54X相比,300 MHz的C55X性 能大约提高了5倍,而功耗则降为C54X的1/6。

DSP第2章 'C54x的硬件结构2

2013年8月15日

DSP原理及应用

6

3.工作方式状态寄存器PMST

主要设定和控制处理器的工作方式和存储器的配置,反映 处理器的工作状态。

15~7 6 5 4 AVIS 3 2 1 0 SST

IPTR MP/MC OVLY

DROM CLKOFF SMUL

中 断 向 量 指 针

CPU 工 作 方 式 选 择 位

③ 暂存器SPRAM。

2013年8月15日

DSP原理及应用

14

特殊功能寄存器

功能:主要用于程序的运算处理和寻址方式的选

择和设定。地址范围:0000H~001FH。 外设寄存器 ’C5402的CPU寄存器共有27个,CPU访问这 功能:用来控制片内外设电路的状态和存放数据。 些寄存器时,不需要插入等待时间。 地址范围:0020H~005FH。 包括串行口通信控制寄存器组、定时器定时控 暂存器SPRAM 制寄存器组、时钟周期设定寄存器组等。 功能:用来暂存变量。地址范围:0060H~007FH。

中断屏蔽寄存器 10H 中断标志寄存器 11H 保留 ( 用于测试 ) 12H 保留 ( 用于测试 ) 13H 保留 ( 用于测试 ) 14H 保留 ( 用于测试 ) 15H 状态寄存器0 16H 状态寄存器1 17H 累加器A低字(15~0位) 18H 累加器A高字(31~16位) 19H 累加器A保护位(39~32位) 1AH 累加器B低字(15~0位) 1BH 累加器B高字(31~16位) 1CH 累加器B保护位(39~32位) 1DH 暂存寄存器 1EH DSP原理及应用 状态转移寄存器 1FH

2013年8月15日

存储器映像的CPU寄存器, 存储器映像的外设寄存器 特殊功能寄存器