11频率计数器设计

用verilog HDL设计的4位频率计

简单4位数字频率计设计一、 设计要求(1)、利用Verilog HDL 语言行为描述方法,设计一个简单的4位数字频率计; (2)、要求输入标准时钟信号频率为1MHz ,系统可计数频率范围为1Hz~9999Hz ; (3)、系统具有复位信号,且当计数频率发生溢出时能够给出指示信号,计数的频率通过4个共阴数码管进行显示(动态扫描显示)。

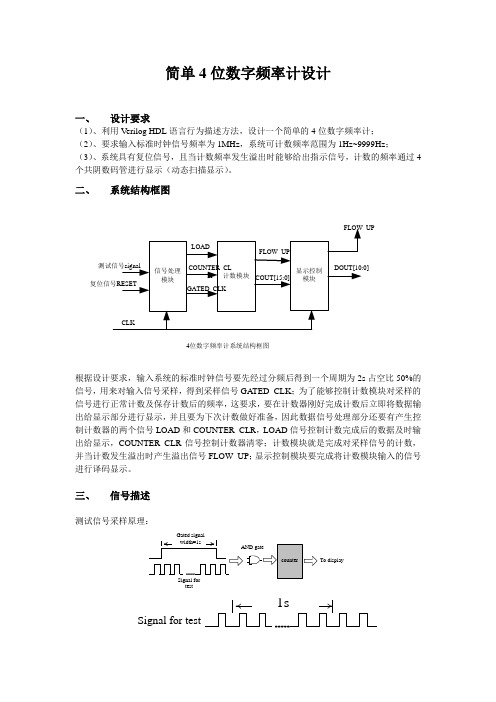

二、 系统结构框图4位数字频率计系统结构框图根据设计要求,输入系统的标准时钟信号要先经过分频后得到一个周期为2s 占空比50%的信号,用来对输入信号采样,得到采样信号GA TED_CLK ;为了能够控制计数模块对采样的信号进行正常计数及保存计数后的频率,这要求,要在计数器刚好完成计数后立即将数据输出给显示部分进行显示,并且要为下次计数做好准备,因此数据信号处理部分还要有产生控制计数器的两个信号LOAD 和COUNTER_CLR ,LOAD 信号控制计数完成后的数据及时输出给显示,COUNTER_CLR 信号控制计数器清零;计数模块就是完成对采样信号的计数,并当计数发生溢出时产生溢出信号FLOW_UP ;显示控制模块要完成将计数模块输入的信号进行译码显示。

三、 信号描述测试信号采样原理:Signal for testTo displaySignal for testGA TED_CLK 、LOAD 、COUNTER_CLR 信号的关系:COUNTER_CLRGATED_CLKLOAD四、 Verilog 程序各子模块verilog 程序:(1)信号处理模块_verilog : moduleFREQUENCY_COUNTROL_BLOCK(GATED_CLK,LOAD,COUNTER_CLR,CLK_IN,SIGNA L_TEST,RESET); output GATED_CLK; output LOAD; output COUNTER_CLR; input CLK_IN; input SIGNAL_TEST; input RESET; reg LOAD; reg COUNTER_CLR; reg DIVIDE_CLK; reg[19:0] cn; reg A1,A2;//信号分频:由CLK_IN 得到分频后的信号DIVIDE_CLK(0.5Hz) always @(posedge CLK_IN) begin if(RESET) begin DIVIDE_CLK<=0; cn<=0;endelse if(cn==1000000)begincn<=0;DIVIDE_CLK<=~DIVIDE_CLK;endelsecn<=cn+1;end//频率计数控制信号的产生:产生LOAD信号和COUNTER_CLR信号always @(posedge SIGNAL_TEST)beginA1<=~DIVIDE_CLK;endalways @(posedge SIGNAL_TEST)beginA2=A1;endalways @(A1 or A2)beginLOAD=A1&&(!A2);endalways @(posedge SIGNAL_TEST)COUNTER_CLR=LOAD;//产生驱动计数模块的信号GATED_CLK,也就是被计数模块检测的信号assign GATED_CLK=SIGNAL_TEST&DIVIDE_CLK;endmodule(2)、计数器模块:moduleFREQUENCY_COUNTER_BLOCK(COUT,FLOW_UP,CLOCK_IN,RESET,LOAD,COUNTER _CLR);output[15:0] COUT;output FLOW_UP;input CLOCK_IN;input LOAD;input COUNTER_CLR;input RESET;reg[15:0] TEMP;reg FLOW_UP;parameter B_SIZE=16; //二进制位宽,为便于移植,所有定义了成参数reg[B_SIZE+3:0] bcd; //转换后的BCD码的位数要比二进制多4位reg[B_SIZE-1:0] binary;reg[B_SIZE-1:0] bin;reg[B_SIZE+3:0] result;//计数器完成计数得到二进制表示的频率数值always @(CLOCK_IN or RESET or LOAD or COUNTER_CLR)beginif(RESET|COUNTER_CLR)beginTEMP<=0;FLOW_UP<=0;endelse if(LOAD)binary<=TEMP;else if(TEMP>9999)beginFLOW_UP<=1;binary<=9999;endelseif(CLOCK_IN)TEMP<=TEMP+1;end//将二进制表示(或十六进制表示)的数转换为BCD码的形式,便于数码管译码显示always @(binary or RESET)beginbin=binary;result=0;if(RESET)bcd<=0;elsebeginrepeat(B_SIZE-1)beginresult[0]=bin[B_SIZE-1];if(result[3:0]>4)result[3:0]=result[3:0]+4'd3;if(result[7:4]>4)result[7:4]=result[7:4]+4'd3;if(result[11:8]>4)result[11:8]=result[11:8]+4'd3;if(result[15:12]>4)result[15:12]=result[15:12]+4'd3;if(result[19:16]>4)result[19:16]=result[19:16]+4'd3;result=result<<1;bin=bin<<1;endresult[0]=bin[B_SIZE-1];bcd<=result;endendassign COUT=bcd[15:0];endmodule(3)信号显示处理:module FREQUENCY_DISPL Y_BLOCK(DOUT,DCLK_IN,RESET,CDIN);output[10:0] DOUT;input[15:0] CDIN;input DCLK_IN;input RESET;reg[10:0] DOUT;reg[3:0] Temp1;reg[1:0] cn;always @(posedge DCLK_IN) //设置成动态扫描beginif(RESET)cn<=0;elsebegincn<=cn+1;case(cn)2'b00: begin DOUT[10:7]<=4'b0001; Temp1<=CDIN[3:0];end2'b01: begin DOUT[10:7]<=4'b0010; Temp1<=CDIN[7:4];end2'b10: begin DOUT[10:7]<=4'b0100; Temp1<=CDIN[11:8];end2'b11: begin DOUT[10:7]<=4'b1000; Temp1<=CDIN[15:12];endendcaseendendalways @(Temp1) //译码显示begincase(Temp1)4'b0000: DOUT[6:0]<=7'b0111111; //3fh=04'b0001: DOUT[6:0]<=7'b0000110; //06h=14'b0010: DOUT[6:0]<=7'b1010110; //56h=24'b0011: DOUT[6:0]<=7'b1001111; //4fh=34'b0100: DOUT[6:0]<=7'b1100110; //66h=44'b0101: DOUT[6:0]<=7'b1101101; //6dh=54'b0110: DOUT[6:0]<=7'b1111101; //7dh=64'b0111: DOUT[6:0]<=7'b0000111; //07h=74'b1000: DOUT[6:0]<=7'b1111111; //7fh=84'b1001: DOUT[6:0]<=7'b1101111; //6fh=9default: DOUT[6:0]<=7'b0111111; //3fhendcaseendendmodule顶层verilog程序:moduleFREQUENCY_COUNTER_DISPL Y_BLOCK(DOUT,FLOW_UP,CLK,TEST_CLK_IN,RESET) ;output[10:0] DOUT;output FLOW_UP;input CLK;input TEST_CLK_IN;input RESET;wire gated_clk,load,counter_clr;wire[15:0] cout_cdin;FREQUENCY_COUNTROL_BLOCKu1(.GATED_CLK(gated_clk),.LOAD(load),.COUNTER_CLR(counter_clr),.CLK_IN(CLK),.SIG NAL_TEST(TEST_CLK_IN),.RESET(RESET));FREQUENCY_COUNTER_BLOCKu2(.COUT(cout_cdin),.FLOW_UP(FLOW_UP),.CLOCK_IN(gated_clk),.RESET(RESET),.LOA D(load),.COUNTER_CLR(counter_clr));FREQUENCY_DISPL Y_BLOCKu3(.DOUT(DOUT),.DCLK_IN(CLK),.RESET(RESET),.CDIN(cout_cdin));endmodule五、仿真结果分析仿真结果如图所示,输入标准时钟频率为1MHz,经过分频后变成频率为0.5Hz的信号,将其与测试信号相与得到采样信号GATED_CLK,同时利用测试信号和0.5Hz的分频信号可以产生LOAD信号和COUNTER_CLR信号,它们和采样信号的关系在图上可以清楚的看出。

【精编完整版】基于单片机的数字频率计的设计毕业论文

目录1频率计的概要和发展动态 (1)2 单片机介绍 (1)2.1单片机的简介和发展 (1)2.2 AT89C51的原理 (2)2.2.1主要特性 (3)2.2.2管脚说明 (3)2.2.3振荡器特性 (4)2.2.4芯片擦除 (4)3 仿真软件protuse的介绍 (5)4系统模块设计 (6)5硬件部分 (6)5.1整形电路 (6)5.2控制电路 (7)5.3显示电路 (8)5.3.1 LCD1602引脚 (8)5.3.2 LCD1602的指令介绍 (8)5.4总体电路图 (9)6仿真结果 (11)6.1仿真结果 (11)6.2结果分析 (11)7 结论 (11)8参考文献 (12)附录 (12)1 keil C51软件介绍 (12)2 程序流程图 (13)3系统源程序 (14)1频率计的概要和发展动态在电子技术中,频率作为基本的参数之一,它与许多电参量的测量方案、测量结果密切相关,因此,频率的测量十分的重要。

在许多情况下,要对信号的频率进行精确测量,就要用到数字频率计。

数字频率计作为一种基础测量仪器,它被用来测量信号(方波、正弦波、锯齿波等)频率,并且用十进制显示测量结果。

它具有测量精度高、测量省时、使用方便等特点。

随着微电子技术和计算机技术的不断发展,单片机被广泛应用到大规模集成电路中,使得设计具有很高的性价比和可靠性。

所以,以单片机为核心的简易数字频率计设计,改善了传统的频率计的不足,充分体现了新一代数字频率计的优越性。

2 单片机介绍2.1单片机的简介和发展单片机微型计算机是微型计算机的一个重要分支,也是颇具生命力的机种。

单片机微型计算机简称单片机,特别适用于控制领域,故又称为微控制器。

通常,单片机由单块集成电路芯片构成,内部包含有计算机的基本功能部件:中央处理器、存储器和IO接口电路等。

因此,单片机只需要和适当的软件及外部设备相结合,便可成为一个单片机控制系统。

单片机经过1、2、3、3代的发展,正朝着多功能、高性能、低电压、低功耗、低价格、大存储容量、强IO功能及较好的结构兼容性方向发展。

单片机课程设计题目及答案

题目1 智能电子钟(LCD 显示)题目2 电子时钟(LCD 显示)题目3 秒表题目4 定时闹钟题目5 音乐倒数计数器题目6 基于数字温度传感器的数字温度计题目7 基于热敏电阻的数字温度计题目8 十字路口交通灯控制题目9 波形发生器设计题目10 电容、电阻参数单片机测试系统的设计题目11 数字频率计题目12 8位竞赛抢答器的设计题目13 单词记忆测试器程序设计题目14 数字电压表设计题目15 可编程作息时间控制器设计题目16 节日彩灯控制器的设计题目17 双机之间的串行通信设计题目18 电子琴设计题目19 数字音乐盒的设计题目20 单片机控制步进电机题目21 单片机控制直流电动机题目1 智能电子钟(LCD 显示) 1. 设计要求 以AT89C51单片机为核心,制作一个LCD 显示的智能电子钟: (1) 计时:秒、分、时、天、周、月、年。

(2) 闰年自动判别。

(3) 五路定时输出,可任意关断(最大可到16路)。

(4) 时间、月、日交替显示。

(5) 自定任意时刻自动开/关屏。

(6) 计时精度:误差≤1秒/月(具有微调设置) (7) 键盘采用动态扫描方式查询。

所有的查询、设置功能均由功能键K1、K2完成。

2. 工作原理 本设计采用市场上流行的时钟芯片DS1302进行制作。

DS1302是DALLAS 公司推出的涓流充电时钟芯片,内含一个实时时钟/日历和31字节静态RAM ,可以通过串行接口与计算机进行通信,使得管脚数量减少。

实时时钟/日历电路能够计算2100年之前的秒、分、时、日、星期、月、年的,具有闰年调整的能力。

DS1302时钟芯片的主要功能特性:(1) 能计算2100年之前的年、月、日、星期、时、分、秒的信息;每月的天数和闰年的天数可自动调整;时钟可设置为24或12小时格式。

(2) 31B 的8位暂存数据存储RAM 。

(3) 串行I/O 口方式使得引脚数量最少。

(4) DS1302与单片机之间能简单地采用同步串行的方式进行通信,仅需3根线。

保证PCF8563 实时时钟精度的设计方法

4

5

从下表的数字可以得到 L= 1 (2 ∗ π ∗ f0 ) 2 ∗ C1 = 7900H Q a = 29000

这很好地解释了为什么振荡器的启动和停止要用几百毫秒 典型值 参数 f0 Δf/f C1 CIN* CIN tC C0 Rs 值 32768 100 3.0 25 +47 1.5 55 10 单位 Hz ppm fF max pF ppm/ pF max k 源 (1) (1) (1) (0) (0) (1) (1) 参数 迟滞 Δf/f 可变的 CT CT tC 值 5 4~25 300 5~30 任意 30 4~7 单位 ppm pF ppm/ pF pF ppm/ pF 源 (1) (2) (2) (3) (4) (4) (0)

-3-

广州周立功单片机发展有限公司 Tel: (020)38730976 38730977 Fax: 38730925 MuRata TZB04 微调电容 Farnell 元件 Philips Components CV05 微调电容 Farnel 元件 Philips Components 多层陶瓷电容 选择一个石英

2

比较

PCF8563 400kHz 0 有 2 个数字+1 位 无 有 有 1.8~5.5V 1.0~5.5V 250nA@ VDD=1V PCF8573 100kHz 0 无 无 无 有 无 2.5~6.0V 1.1~6.0V 3mA@1.5V 12mA@5V DIL/SO16 PCF8583 100kHz 248B 有 2位 10ms 有 无 2.5~6.0V 1.1~6.0V 2mA@1.0V 10mA@5V DIL/SO8 PCF8593 100kHz 0 有 2位 10ms 有 无 2.5~6.0V 1.1~6.0V 1mA@2.0V 4mA@5V DIL/SO8

基于单片机的数字频率计的设计与实现

基于单片机的数字频率计的设计与实现摘要随着电子信息产业的发展,信号作为其最基础的元素,其频率的测量在科技研究和实际应用中的作用日益重要,而且需要测频的范围也越来越宽。

传统的频率计通常采用组合电路和时序电路等大量的硬件电路构成,产品不但体积较大,运行速度慢,而且测量范围低,精度低。

因此,随着对频率测量的要求的提高,传统的测频的方法在实际应用中已不能满足要求。

因此我们需要寻找一种新的测频的方法。

随着单片机技术的发展和成熟,用单片机来做为一个电路系统的控制电路逐渐显示出其无与伦比的优越性。

本文阐述了以AT89C51单片机为控制器件的频率测量方法,并用汇编语言进行设计,采用单片机智能控制,结合外围电子电路,用以实现高低信号频率的测量。

本文设计的是一个简易数字频率计,被测信号可以是正弦波、三角波、方波。

首先,我们把待测信号经过放大整形;然后把信号送入单片机的定时计数器里进行计数,获得频率值;最后把测得的频率数值送入显示电路里进行显示。

本文从频率计的原理出发,介绍了基于单片机的数字频率计的设计方案,选择了实现系统得各种电路元器件,并对硬件电路进行了仿真。

关键词单片机;频率计;测量-Design and implementation of Digital FrequencyMeter Based on Single Chip MircrocomputeAbstractAlong with the development of electronic information industry, signal as the basic elements, the frequency measurement in scientificresearch and practical application is increasingly important, but also need the scope of frequency measurement is becoming more and more wide. The traditional frequency plan usually adopts combinational circuits and the sequential circuits of the hardware circuit structure, product not only large size, speed is slow, and measuring range, and low accuracy of low. Therefore, as for frequency measurement requirements, thetraditional method of frequency measurement in practical application already cannot satisfy requirements. Therefore, we need to find a new measuring method of frequency. Along with the development of technology and mature, use a singleship as a circuit system of control circuit shown its incomparable advantages.In this paper, with AT89C51 microcontroller to control the frequency of measurement devices and assembly language design, intelligent control using single chip, combined with the external electronic circuit, can be high and low frequency measurements. This paper designs a simple digital frequency, the measured signal can be sine wave , square wave. Firstly, the rectangular pulse, which the measured signal is amplified and reshaped, is used as control throttle valve. Then, the frequency counter counts the number of the periods using the internal timer/counter of signal is chip so as to gain the frequency value of measured signal. Finally, the frequency value of measured signal is displayed through static display circuits.From the analysis of theory, and introduces the digital frequency plan based on single chip design, selection of the system, and have all kinds of circuit components of hardware circuit simulaion.Keywords Micor- computer;Frequency;Measure-目录摘要...... ................................................................. (I)Abstract ........................................................... .. (II)第1章绪论 ..................................................................... .. (1)1.1 课题背景 ..................................................................... . (1)1.2 单片机的发展及特点 ..................................................................... .................1 1.3 频率计的基础知识 ..................................................................... .....................1 1.4 论文研究内容 ..................................................................... .............................2 第2章单片机简介及方案论证 ..................................................................... ...........3 2.1 AT89C51单片机简介 ..................................................................... ..................3 2.1.1 单片机及其引脚说明 ..................................................................... ...........3 2.1.2 AT89C51的定时/计数器原理 (5)2.1.3 定时/计数器的工作模式 ..................................................................... (6)2.1.4 定时,计数器的特殊功能控制寄存器 (6)2.1.5 定时,计数器(T0,T1)的控制寄存器 (7)2.2 数字频率计设计的几种方案 ..................................................................... (8)2.3 几种方案的优劣讨论 ..................................................................... .................8 2.4 本次设计采用的方案 ..................................................................... .................9 2.5 本章小结 ..................................................................... .....................................9 第3章系统硬件设计 ..................................................................... ........................ 10 3.1 数字频率计工作原理及结构框图 (10)3.1.1 一般数字式频率计的原理 ......................................................................10 3.1.2 基于单片机的数字频率计原理 .............................................................. 10 3.2 电路原理图 ..................................................................... ............................... 11 3.3 放大整形电路 ..................................................................... ........................... 11 3.3.1 放大整形电路的必要性 ..................................................................... ..... 11 3.3.2 放大整形电路的原理 ..................................................................... ......... 11 3.4 分频电路 ..................................................................... ................................... 15 3.4.1 分频电路介绍 ..................................................................... .................... 15 3.5 四选一电路 ..................................................................... ............................... 16 3.6 显示电路 ..................................................................... ................................... 17 3.6.1 显示原理 ..................................................................... ............................ 17 3.6.2 显示电路图 ..................................................................... ........................ 19 3.7 本章小结 ..................................................................... ................................... 20 第4章系统软件设计 ..................................................................... ........................ 21 4.1 软件流程图 ..................................................................... ............................... 21 4.2 测频软件实现原理 ..................................................................... . (21)-4.3 几个重要的分程序 ..................................................................... ................... 22 4.4 本章小结 ..................................................................... ................................... 23 结论 ..................................................................... ..................................................... 24 致谢 ..................................................................... ..................................................... 25 参考文献 ..................................................................... ............................................. 26 附录A ...................................................................... ................................................ 27 附录B ...................................................................... ................................................ 33 附录C ...................................................................... ................................................ 39 附录D ...................................................................... (40)第1章绪论1.1 课题背景在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关,,因此频率计在教学、科研、测量仪器、工业控制[1]等方面都有较广泛的应用。

HC-F1000L多功能频率计使用说明

HC-F1000L多功能计数器概述HC-F1000L/M多功能计数器(以下简称本仪器)是采用单片机对测量进行智能化控制和数据处理的多功能计数器,测量范围为数码管进行显示,具有四种测量功能,采用低功耗线路设计。

实现全频段等精度测量。

等数位显示(本机基础为10MHz等精度计数器)。

内部晶体振荡器稳定性高,保证仪器的测量精度和全输入信号的测量。

具有体积小、灵敏度高、极高的性能价格比等优点。

本仪器有四个主要功能:A通道测频、通道测频、A通道测周期及A通道具有输入信号衰减、低通滤器功能。

本仪器可广泛应用于实验室、工矿企业、大专院校、生产调试以及无线通信设备维修之用。

高灵敏度的测量设计可满足通信领域超高频信号的正确测量,并取得最好的测量效果。

在使用本仪器以前,建议通道并弄懂本说明书,以便正确操作。

技术参数2.1频率测量范围A通道:1z~100MHzB通道:100MHz~1000MH z(最高可达1200NHz)2.2周期测量范围(仅限于A通道)A通道:1Hz~10MHz2.3计数频率及容量(仅限于A通话)频率:1Hz~10MHz容量:108-12.4输入阻抗A通道:R≈1MΩC≤35PfB通道:50Ω2.5输入灵敏度A通道:1Hz~10Hz 优于50mV rms(仅供参考)10Hz~80MHz优于20mV rms80Hz~100MHz优于30mV rmsB通道:100Hz~1000MH z 优于20mV rms1000Hz~1200MH z 优于50mV rms(仅供参考)2.6闸门时间预选:0.01s;1 s或保持2.7输入衰减(仅限于通道)A通道:×1或20固定2.8输入低通滤波器(仅限于A通道)2.8.1截止频率:≈100KHz2.8.2衰减:≈3Db(100 KHz频率点,输入幅度不得<30mVrm s)2.9最大安全电压A通道:250V(直流和交流之和;衰减置×20档)B通道:3V2.10准确度±时基准确度±触发误差×被测频率(或被测周期)±LSD其中:LSD=×被测―――频率(或被测周期)2.11时基2.11.1标称频率:10 MHz2.11.2频率稳定度:优于5×10-6/d2.12时基输出2.12.1标称频率:10 MHz2.12.2输出幅度(空载)“0”电平:0V~0.8V“1”电平:3V~5V2.13显示2.13.1八位0.4寸红色发光数码管并带有十进制小数点显示。

简易数字显示交流毫伏表(最终定稿)

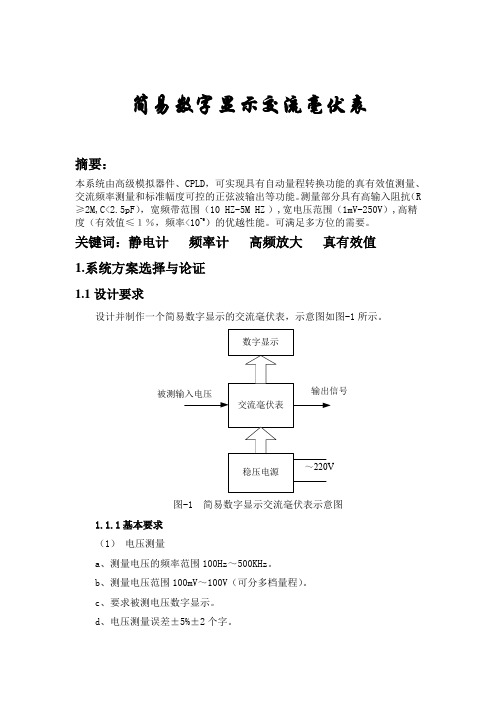

简易数字显示交流毫伏表摘要:本系统由高级模拟器件、CPLD,可实现具有自动量程转换功能的真有效值测量、交流频率测量和标准幅度可控的正弦波输出等功能。

测量部分具有高输入阻抗(R ≥2M,C<2.5pF),宽频带范围(10 HZ-5M HZ),宽电压范围(1mV-250V),高精度(有效值≤1%,频率<10-6)的优越性能。

可满足多方位的需要。

关键词:静电计频率计高频放大真有效值1.系统方案选择与论证1.1设计要求设计并制作一个简易数字显示的交流毫伏表,示意图如图-1所示。

图-1 简易数字显示交流毫伏表示意图1.1.1基本要求(1)电压测量a、测量电压的频率范围100Hz~500KHz。

b、测量电压范围100mV~100V(可分多档量程)。

c、要求被测电压数字显示。

d、电压测量误差±5%±2个字。

e、输入阻抗≥1MΩ,输入电容≤50pF(本项可不做测试,在电路设计中给予保证)f、具有超量程自动闪烁功能。

(2)设计并制作该仪表所需要的直流稳压电源。

1.1.2发挥部分(1)将测量电压的频率范围扩展为10Hz~1MHz。

(2)将测量电压的范围扩展到10mV~200V。

(3)交流毫伏表具有自动量程转换功能。

(5)其他。

1.2系统基本方案及框图根据题目要求及适当的发挥,我们的硬件电路主要包括输入信号的有效值测量、输入信号的频率测量。

其中前两者构成一个测量系统。

测量系统包括:信号调理模块、A/D,D/A模块、信号真有效值转换模块、CPLD频率测试模块、算法控制器模块、键盘显示模块、语音播报及打印模块、电源模块等。

图-3所示。

为实现各模块的功能,分别作了几种不同的设计方案并进行了论证,我们选取了较好的方案实现。

图-3 测量系统框图1.2.1各模块方案选择和论证(1)有效值测量部分:方案一:用分立元件搭焊高频放大电路,用精密整流电路测量输入信号的真有效值。

这种方案成本较低。

但是这种电路结构复杂,调试困难,精度低,温漂大,稳定度低。

EDA课设--简易电子琴

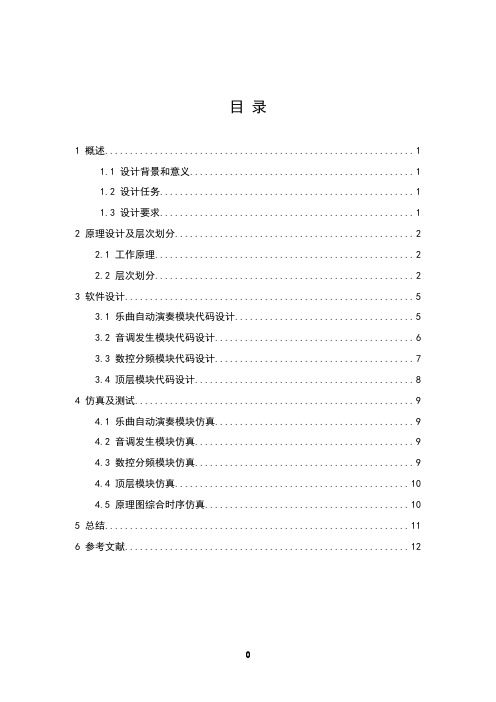

目录1 概述 (1)1.1 设计背景和意义 (1)1.2 设计任务 (1)1.3 设计要求 (1)2 原理设计及层次划分 (2)2.1 工作原理 (2)2.2 层次划分 (2)3 软件设计 (5)3.1 乐曲自动演奏模块代码设计 (5)3.2 音调发生模块代码设计 (6)3.3 数控分频模块代码设计 (7)3.4 顶层模块代码设计 (8)4 仿真及测试 (9)4.1 乐曲自动演奏模块仿真 (9)4.2 音调发生模块仿真 (9)4.3 数控分频模块仿真 (9)4.4 顶层模块仿真 (10)4.5 原理图综合时序仿真 (10)5 总结 (11)6 参考文献 (12)1 概述1.1 设计背景和意义EDA技术是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言VHDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

EDA技术的出现,极大地提高了电路设计的效率和可操作性,减轻了设计者的劳动强度。

1.2 设计任务利用所学的EDA设计方法设计简易电子琴,熟练使用QUARTUSⅡ应用软件,进一步学习使用VHDL语言、原理图等EDA设计方法进行综合题目的方法。

1.3 设计要求①设计一个简易的八音符电子琴,它可通过按键输入来控制音响。

②演奏时可以选择是手动演奏(由键盘输入)还是自动演奏已存入的乐曲。

③能够自动演奏多首乐曲,且每首乐曲可重复演奏。

④它由乐曲自动演奏模块、音调发生模块和数控分频模块三部分组成。

2 原理设计及层次划分2.1 工作原理本课程设计目的在于灵活运用EDA技术编程实现一个简易电子琴的乐曲演奏,它要求在实验箱上构造一个电子琴电路,不同的音阶对应不同频率的正弦波。

按下每个代表不同音阶的按键时,能够发出对应频率的声音。

故系统可分为乐曲自动演奏模块(AUTO)、音调发生模块(TONE)和数控分频模块(FENPIN)三部分。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

湖南工程学院应用技术学院课程设计

课程名称

课题名称

专业

班级

学号

姓名

指导教师

2015 年7 月3 日

报告撰写要求(此页不打印)

课程设计报告是体现课程设计成果的载体,具体要求如下:

1、课程设计报告的基本格式

(1)说明书统一使用word文档打印,A4纸张,页边距设置为:上2cm,下2cm,左2.54cm,右2cm。

(2)正文采用宋体小四,字间距20磅;1级标题采用黑体小三,2级标题采用黑体四号,3级标题采用黑体小四;1和2级标题段落间距为上下0.5行。

(3)图表需统一编号,图标标题采用黑体五号;图标题在图片下方,表格标题在表格上方。

(4)装订顺序为:封面、任务书、报告正文、评分表。

2、课程设计报告的撰写要求

(1)设计报告正文内容为10页左右为宜,主要内容为自己的设计思路、设计步骤、关键性步骤的记录、重要结果的记录以及自己本次课程设计的总结。

报告撰写要求思路清晰、结构合理、层次清晰,报告简洁但又要能体现设计过程。

(2)报告中图表要求清晰、规范,图表的尺寸大小适当。

(3)课程设计报告内容(仅供参考):

应用技术学院

课程设计任务书

课题名称频率计数器设计

姓名专业班级学号

指导老师寻大勇

课程设计时间2015年6月22日-2015年7月3日

一、任务及要求

设计任务:

本课题以单片机为核心,设计和制作一个频率计数器,来完成对输入的信号进行频率计数,计数的频率结果能够显示出来。

要求能够对0-250KHz的信号频率进行准确计数,计数误差不超过±1HZ。

设计要求:

(1)确定系统设计方案;

(2)进行系统的硬件设计;

(3)完成应用程序设计;

(4) 应用系统的硬件和软件的调试。

二、进度安排

第一周:

周一:集中布置课程设计任务和相关事宜,查资料确定系统总体方案。

周二~周三:完成硬件设计和电路连接

周四~周日:完成软件设计

第二周:

周一~周三:程序调试

周四~周五:设计报告撰写。

周五进行答辩和设计结果检查。

三、参考资料

1、王迎旭等.单片机原理及及应用. 2版.机械工业出版社,2012

2、胡汉才.单片机原理及其接口技术.3版.清华大学出版社,2010.

3、戴灿金.51单片机及其C语言程序设计开发实例.清华大学出版社,2010

(报告正文:正文采用宋体小四,字间距20磅;1级标题采用黑体小三,2级标题采用黑体四号,3级标题采用黑体小四;1和2级标题段落间距为上下0.5行。

打印前删除)

目录

第1章总体方案设计

设计任务与要求;设计原理或者设计思路,给出总体设计框图。

第2章硬件电路设计

系统各模块硬件电路的设计方法、与单片机I/O口连接方法及原理图。

第3章软件设计

系统主程序、中断服务程序及主要的子程序的设计思路(文字描述)及其流程图。

第4章调试

系统调试方法(硬件调试,还是仿真调试)、调试结果、调试中遇到的问题及其解决方法。

第5章总结

整个课程设计过程中,你觉得学习到了什么,课设过程中自己做的不足的地方有哪些?对自己的学习有何启示?希望课程设计过程或者指导老师如何改进?……

附录

附录A ***原理图

附录B 程序清单

《单片机原理及应用》课程设计评分表

注:①表中标*号项目是根据课题实际情况二选一;

②此表装订在课程设计说明书的最后一页。