伪随机测试激励信号设计

Artemis_ATP08_and_ME'scope_VES锤击法模态分析操作指南-牛维2012

FRF测试,参考的选择

H( f ) X ( f ) / F( f )

Response( roving response a column of FRF)

Excitation(roving Hammer a row of FRF)

H1

G fx Gff

F

k 1 m k 1

m

*

( f )X ( f )

设臵启动为Integrated Recorder

连接并检测硬件连接,点击上图 中的图标,打开采集界面

FRF测试

选择前端,根据最大关心频率设臵主采样频率

进入Analyze界面

FRF测试

通道设臵:

1、根据配臵选择开启通道,配臵传感器,量程及DOF 量程需要反复调试,以保证信号的最大信噪比; 2、如果为多参考输入出,注意DOF的选择;

幅值

1阶模态 2阶模态 3阶模态 梁 加速度

Force Force Force Force Force Force Force Force Force Force 力Force

试验模态激励:

1、步进式正弦激励法:从最低频率到最高频率选定足够数目离散的频率值, 每次使用一个频率给出激励信号,测出该激励的稳定响应,在进行下一个频率;

频响函数 固有频率、阻尼、振型

模态试验的基本假设

1、振动系统是线性的,满足叠加原理 任何输入组合引起的输出等于各自输出的组合,在模态试验中首 先检查结构的线性动态特性

2、振动系统是时不变的 结构动态特性不随时间变化的 3、可观测性假设 系统的动态特性所需要的全部数据都是可以测量的,这对选择响 应的自由度非常重要 4、振动系统遵从Maxwell互易性原理 在A点的输入所引起B点的响应等于B点的相同输入所引起的A点的 响应

实验九 用正弦扫频

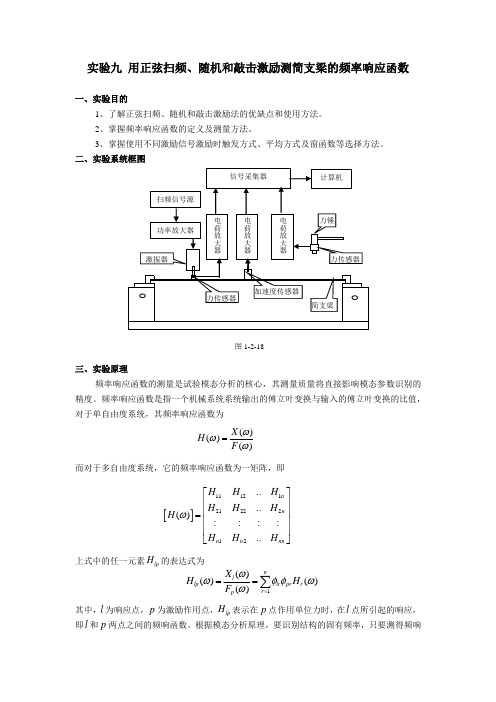

实验九 用正弦扫频、随机和敲击激励测简支梁的频率响应函数一、实验目的1、了解正弦扫频、随机和敲击激励法的优缺点和使用方法。

2、掌握频率响应函数的定义及测量方法。

3、掌握使用不同激励信号激励时触发方式、平均方式及窗函数等选择方法。

二、实验系统框图三、实验原理频率响应函数的测量是试验模态分析的核心,其测量质量将直接影响模态参数识别的精度。

频率响应函数是指一个机械系统系统输出的傅立叶变换与输入的傅立叶变换的比值,对于单自由度系统,其频率响应函数为()()()X H F ωωω= 而对于多自由度系统,它的频率响应函数为一矩阵,即上式中的任一元素lp H 的表达式为其中,l 为响应点,p 为激励作用点,lp H 表示在p 点作用单位力时,在l 点所引起的响应,即l 和p 两点之间的频响函数。

根据模态分析原理,要识别结构的固有频率,只要测得频响图1-2-18 []111212122212....()::::..n n n n nn H H H H H H H H H H ω⎡⎤⎢⎥⎢⎥=⎢⎥⎢⎥⎣⎦1()()()()n l lp lr pr r r p X H H F ωωφφωω===∑函数矩阵中任何一个元素即可,但要识别所有模态参数时,必须测得频响函数矩阵中的一行或一列。

由lp H 的表达式可知,要测量矩阵中的一行时,要求拾振点固定不变,轮流激励所有的点,即可求得[()]H ω中的一行,这一行频响函数包含进行模态分析所需要的全部信息。

而要测量[()]H ω中任一列时,则激励点固定不变,而在所有点进行拾振,便可得到[()]H ω中的一列,这一列频响函数也包含进行模态分析所需要的全部信息。

在进行多点拾振时,若传感器足够多,且所有传感器质量加起来比试验物体的质量小很多时,就可安装多个传感器同时拾振,这样可以节省试验时间,且数据的一致性也好;但如果只有一只传感器时,则一个一个点进行测量,这样虽试验时间长一些,但试验成本较低,需保证激励信号的一致性。

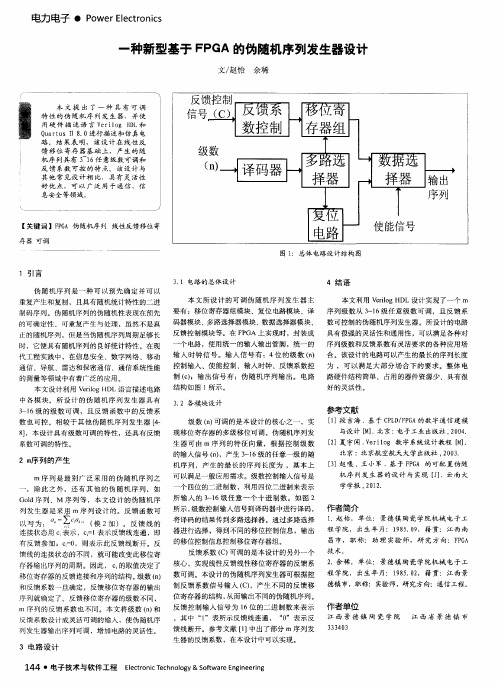

一种新型基于FPGA的伪随机序列发生器设计

参考文献

级数 ( n ) 可调 的是本设计的核心之一 ,实 现移位寄存器的多级 移位可调 。伪 随机序列 发 生器 可 由 m序列 的特 征 向量 ,根据控 制级数 的输入信号 ( n ) ,产生 3 ~ 1 6级 的任意一级 的随 机序列 ,产生 的最长 的序 列长度 为 ,基本上 可 以满足一般应用需求。级数控制 输入信号是

学学报 , 2 0 1 2 .

Go l d序列 、M 序 列等 ,本 文设计 的伪 随机序 列 发生器是 采用 m序 列设计 的。反馈 函数 可

所 输入 的 3 N 1 6级 任意 一个 十进制数 。如 图 2 所示 , 级数控 制输入信号到译码器 中进 行译码 , 将译码的结果传到多路选择器 。通 过多路选择 器进行选择 ,得到不同的移位控制信息,输出 的移位控制信息控制移 位寄存器组 。 核心 ,实现线性反馈线性移 位寄存器 的反馈 系

系数 可 调 的特 性 。

个电路 ,使 用统一 的输入输 出管脚 ,统一 的

输 入时钟信 号 。输入信 号有 :4位 的级 数 ( n ) 合 。该设 计的电路可以产生 的最长的序列长度 控制输入 、使能控制、输入 时钟、反馈系数控 为 ,可 以满 足大部 分场合 下的要求 。整体 电 制( c ) ;输 出信号有 :伪 随机 序列输 出。 电路 路硬件结构简单、 占用的器件 资源少 、具有很 结构如图 1所示。

电力 电子 ・ P o we r E l e c t r o n i c s

一

种新型基于 F P G A的伪随机序列发生器设计

文/ 赵怡 余 稀

特

用 Q u 路

馈

机

反

第八章伪随机序列

二、 游程分布(游程分布的随机性)

游程:一个序列中取值(1 或 0)相同连在一起的元素的统称 游程长度:

分布特性:

1.m序列的一个周期(p=2n-1)中,游程总数为2n-1。

2.当1 <游程长度k ≤n-1,游程数目占总数2-k 当1 ≤k ≤n-2,连“1”和连”0“游程各占一

半

例如 m序列:000111101011001, p=15

cn-1 n

a0

cn=1 输出 ak

线性反馈移位寄存器

它是由n级移位寄存器、时钟发生器(图中未画出)

及一些异或电路连接而成。图中ai(i=1,2,…..n-1)

为某一级移存器状态,Ci表示反馈线连接状态: Ci=1,表示反馈线通,参与反馈; Ci=0,表示断开,不参与反馈。 C0 =Cn=1。

1.

0

0

1

1

0

0

1

1

1

0

1

1

1

1

0

1

1

1

1

0

1

1

0

1

0

1

1

0

1

0

1

1

0

1

15位

0

1

1

0

ak 0

0

1

1

1

0

0

1

0

1

0

0

0

0

1

0

需要自己推导一下

0

0

0

1

1

0

0

0

… … … …

说明:

1.为了m序列发生器组成尽量简单, 就使用项数少的那些本原多项式。

2.本原多项式的递多项式也是本原 多项式,表中每一项多项式可组成 两种发生器。

伪随机序列的产生及应用设计-通信原理课程设计

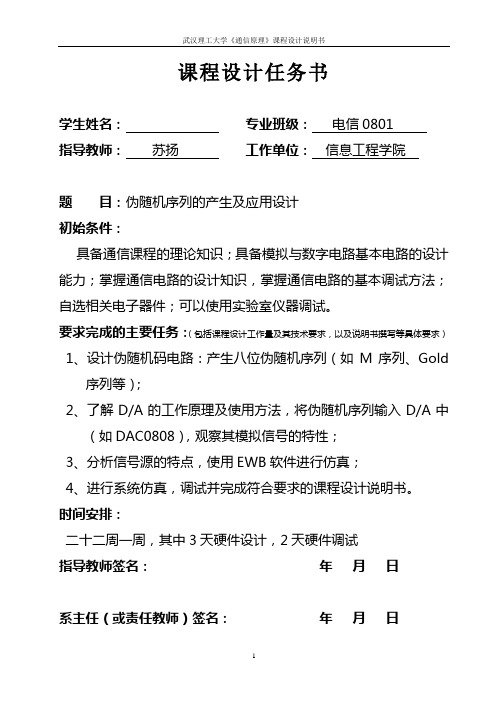

课程设计任务书学生姓名:专业班级:电信0801指导教师:苏扬工作单位:信息工程学院题目:伪随机序列的产生及应用设计初始条件:具备通信课程的理论知识;具备模拟与数字电路基本电路的设计能力;掌握通信电路的设计知识,掌握通信电路的基本调试方法;自选相关电子器件;可以使用实验室仪器调试。

要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求)1、设计伪随机码电路:产生八位伪随机序列(如M序列、Gold序列等);2、了解D/A的工作原理及使用方法,将伪随机序列输入D/A中(如DAC0808),观察其模拟信号的特性;3、分析信号源的特点,使用EWB软件进行仿真;4、进行系统仿真,调试并完成符合要求的课程设计说明书。

时间安排:二十二周一周,其中3天硬件设计,2天硬件调试指导教师签名:年月日系主任(或责任教师)签名:年月日目录摘要 (I)1理论基础知识 (1)1.1伪随机序列 (1)1.1.1伪随机序列定义及应用 (1)1.1.2 m序列产生器 (2)1.2芯片介绍 (4)1.2.1移位寄存器74LS194. (4)1.2.2移位寄存器74LS164 (5)1.2.3 D/A转换器DAC0808 (6)2 EWB软件介绍 (8)3设计方案 (9)4 EWB仿真 (11)5电路的安装焊接与调试 (13)6课程设计心得体会 (14)参考文献 (15)附录1 (16)摘要伪随机序列具有良好的随机性和接近于白噪声的相关函数,使其易于从信号或干扰中分离出来。

伪随机序列的可确定性和可重复性,使其易于实现相关接收或匹配接收,因此有良好的抗干扰性能。

伪随机序列的这些特性使得它在伪码测距、导航、遥控遥测、扩频通信、多址通信、分离多径、数据加扰、信号同步、误码测试、线性系统、各种噪声源等方面得到了广泛的应用,特别是作为扩频码在CDMA系统中的应用已成为其中的关键问题。

此次课设根据m序列的产生原理,利用74LS164加少量门电路方法设计了8位m序列发生器。

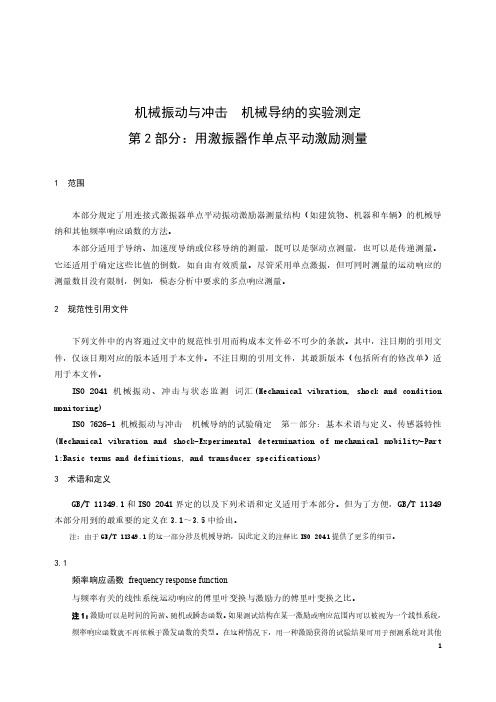

机械振动与冲击 机械导纳的实验测定 第2部分:用激振器作单点平动激励测量-最新国标

3.4

传递导纳,Yij

transfer mobility,Yij

除了表示结构在预计应用中的正常支撑之外没有其他约束,允许结构上除 j 点外的所有点自由响

应,这时 i 点的速度响应相量与 j 点的激励力相量之比构成的频率响应函数。单位为 m/(N·s)。

monitoring)

ISO 7626-1 机械振动与冲击

机械导纳的试验确定

第一部分:基本术语与定义、传感器特性

(Mechanical vibration and shock-Experimental determination of mechanical mobility-Part

1:Basic terms and definitions, and transducer specifications)

短时间间隔内,激励能量集中在其扫描的频带内。

6.2.4 平稳随机激励

平稳随机激励的波形没有显式数学表达式,但具有一定的统计性质。激励信号谱用激励

力的谱密度来表示,9.4.3 推荐了把激励集中在关注的频率范围内以形成谱密度的方法。这

样,可同时激励起这个频率范围内的所有模态。

6.2.5 其他激励波形

6.2.5.1 概述

3.2

导纳 mobility

机械导纳 mechanical mobility

机械系统中一点的速度与该点或另一点施加的激振力的复数比。

注 1:除了结构在使用中正常支撑表现的约束之外,结构上所有其他测量点没有任何约束,允许其自由响应。此时,

�点的复速度响应与�点处的复激励力的比率,即为导纳。

注 2:术语“点”是指位置和方向。

机械振动与冲击

伪随机信号发生

序列长度

3 7 15 31 63 127 255 511 1023 2047 32767 131071 262143 1048575 2097151 4194303 8388607 33554431 268435455 536870911 2147483647 8589934591 68719476735

y ( t) + n1 ( t)

式中 n1 ( t) 与 n ( t) 的输出一样 , 也是白噪声干扰 。 可见 ,当伪随机信号输入时 ,其互相关函数的计算只 需在一个周期的时间即可 ,即

∫ R xz (τ)

=

1 T

T

z ( t) x ( t - τ) d t

0

综上所述 ,采用伪随机信号代替白噪声信号后 ,

图 5 脉冲响应与互相关函数的关系

3 钻井工程应用

如果把上述伪随机信号加入到文献 [1 ] 中脉冲 响应为 g (τ) 的钻柱系统的输入端 , 则输入 x ( t) 与 被测输出 z ( t) 间互相关函数 R xz (τ) 为

R xz (τ) = R xy (τ) + R xn (τ)

若伪随机信号 x ( t) 大的周期 T 选择比较大 ,以

66 随机信号产生的逻辑框图 。

西南石油学院学报 2000 年

T = NΔt

表 2 4 级移位寄存器各输出状态级

级

状态

数 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

1 1000100110101111

2 1100010011010111

68

西南石油学院学报 2000 年

变化曲线 。这种测振装置是安装在钻头或钻头附近 底部钻具组合上 ,用无线或有线的方式将钻头振动 信号传输到地面进行处理 。这种方法可以直接测量 钻头或钻具的振动 ,了解钻头在井底的工作状况 、磨 损情况 、以及所钻地层岩性 。

基于FPGA的伪随机序列发生器设计方案

基于FPGA的伪随机序列发生器设计方案1基本概念与应用1)1FSR:线性反馈移位寄存器(1inear feedbackshiftregister,1FSR)是指给定前一状态的输出,将该输出的线性的薮再用作输入的移位寄存器。

异或运算是最常见的单比特线性函数:对寄存器的某些位进行异或操作后作为输入,再对寄存器中的各比特进行整体移位。

1FSR产生的两种形式为伽罗瓦(Ga1ois)和斐波那契(FibonaCCi)两种形式。

也有成为外部(Ex隹rna1)执行方式和内部(Interna1)执行方式。

(1)伽罗瓦方式(Interna1)X0X4X17! ! TepCount ,-Θ□□EF-Γ>4300000000Θ{3B0-*~*DaiaFtowW>)∙ι.x4.χ“(Ga1oisImp1ementation)Ga1ois方式特征数据的方向从左至右,反馈线路是从右至左。

其中XCo项(本原多项式里面的T'这一项)作为起始项。

按照本原多项式的指示确定异或门(XOR)在移位寄存器电路上的位置。

如上图所示XM。

因此Ga1ois方式也有人称作线内或模类型(M-型)1FSRo(2)斐波那契方式(Externa1)TapCountB*0;E3t3-⅛QEHIH30GHZHHDGIFSHpcivncrTMrig(M)-X14.X,>♦X n»1(Fibonacciimp1ementation)从图中我们可以看到Fibonacci方式的数学流向和反馈形式是恰好跟Ga1ois方式相反的,按照本原多项式,其中XCO这一项作为最后一项,这里需要一个XOR∏,将本原多项式中所给的taps来设定它的异或方式。

因此Fibonacci方式也被叫做线外或者简型(S-型)1FSR。

2)本原多项式本原多项式是近世代数中的一个概念,是唯一分解整环上满足所有系数的最大公因数为1的多项式。

本原多项式不等于零,与本原多项式相伴的多项式仍为本原多项式。

振动测试及其信号处理

振动测试及其信号处理伏晓煜倪青吴靖宇王伟摘要:随着试验条件和技术的不断完善,越来越多的领域需要进行振动测试,尤其是土木工程领域。

本文首先介绍了振动测试的基本内容和测试系统的组成,其次对振动测试中的激励方式进行了简单的概括,最后总结了信号数据的处理一般方法,包括数据的预处理方法、时域处理方法和频域处理方法。

关键词:振动测试测试系统信号处理Vibration Test and Signal processingFu Xiaoyu Ni Qing Wu Jingyu Wang WeiAbstract: Vibration test has been applied in more and more fields, especially in civil engineering, as experiment methods and technology elevated. This paper introduced the contents of vibration test and consists of test system firstly, and generalized the exciting mode subsequently. General methods of vibration signal processing were summarized in the end, including preprocessing, time-domain processing and frequency-domain processing methods.Key words: vibration test; test system; signal processing0 引言研究结构的动态变形和内力是个十分复杂的问题,它不仅与动力荷载的性质、数量、大小、作用方式、变化规律以及结构本身的动力特性有关,还与结构的组成形式、材料性质以及细部构造等密切相关。

伪随机码发生器研究与设计

伪随机码发生器研究与设计伪随机码发生器是一种通过其中一种算法生成伪随机序列的电子设备或程序。

与真随机数发生器不同,伪随机码发生器是基于确定性算法生成的序列,其看似是随机的,但实际上可以通过逆向计算或算法分析来预测出后续的码值。

1.算法选择:伪随机码发生器的性能很大程度上取决于所选择的算法。

常用的算法包括线性反馈移位寄存器(LFSR)、离散余弦变换(DCT)、线性同余发生器(LCG)等。

研究者可以根据特定需求选择合适的算法,并通过数学分析、理论推导和模拟实验来评估其性能。

2.随机性测试:伪随机码发生器生成的序列是否具备足够的随机性是一个关键问题。

为了评估伪随机码发生器的性能,需要设计合适的随机性测试方法。

常用的测试方法包括统计分析、频谱分析、序列均匀性检测、序列独立性检验等。

3.秘密性与安全性:在密码学应用中,伪随机码发生器的秘密性和安全性是非常重要的。

秘密性指发生器的设计和参数应保密,只有掌握这些信息的人才能伪装成合法用户。

安全性指发生器生成的序列在密码攻击下能够抵抗各种攻击手段。

确保秘密性和安全性需要对伪随机码发生器进行全面的安全性分析和风险评估,以便发现可能存在的漏洞和弱点,并采取相应的安全措施和改进措施。

4.性能优化:伪随机码发生器的性能包括生成速度、存储空间和计算复杂度等方面。

研究者需要在保证安全性的前提下,尽可能提高伪随机码发生器的性能。

这包括改进算法、优化参数选择、使用硬件加速等。

总结起来,伪随机码发生器的研究与设计需要深入理解随机性、密码学和计算机科学等领域的知识,并结合具体应用需求来选择合适的算法和进行性能优化。

通过合理的算法设计、随机性测试和安全性分析评估,以及针对性的安全措施和改进措施,可以设计出安全可靠的伪随机码发生器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

伪随机测试激励信号设计作者:孙永建秦鹏唐景华

来源:《数码设计》2020年第07期

摘要:模数混合电路的内建自测试(BIST)研究是近些年比较有挑战的,其中如何以较小的硬件开销获得模拟激励信号以及数据响应分析比较关键。

本文将以伪随机信号作为研究对象,对BIST结构的激励模块进行设计伪随机信号,并在QuartusⅡ里进行仿真验证,为后续混合信号BIST结构设计打下基础。

关键词:BIST;测试激励;LFSR

中图分类号:TN407文献标识码:A文章编号:1672-9129(2020)07-0076-02

Abstract: The study of modular hybrid circuit built-in self-testing (BIST) is challenging in recent years, among which how to obtain analog excitation signal and data response analysis with less hardware cost is key. This article will take the pseudo random signal as the research object, the incentive of BIST structure module design pseudo random signal, and Quartus Ⅱ simulation verification, lay the foundation for subsequent mixed-signal BIST structure design.

Key words: BIST; Test incentives; LFSR

1引言

内建自测试(BIST)是由测试电路自身生成测试激励信号,作用于电路本身并根据响应来进行测试的方法[1],是一種很重要的测试方法。

若测试结构中的测试激励为零均值的高斯随机信号时,不仅能简化求取各阶累积量谱的计算[2],而且高斯随机信号在性质上接近白噪声,其带宽和幅度都可以控制,可以保证对被测电路的持续激励,所以采用高斯随机信号作为某混合信号BIST结构中的激励信号。

但是设计服从高斯分布的随机信号比较复杂而且在设计中是无法得到完全服从高斯分布的激励信号。

2激励模块设计

2.1 激励结构。

伪随机信号在现实应用中通常采用线性移位寄存器序列(M序列)来产生,具有十分接近白噪声的性质,因此又称伪随机信号为伪高斯信号。

激励生成的结构如图1所示,包含控制信号、线性反馈移位寄存器(LFSR)[3]和DAC三部分组成。

当BIST控制器使能有效时,激励内部的控制器则产生LFSR使能信号,使得LFSR开始移位输出,并同时给DAC控制时钟信号,DAC输出的模拟信号就是伪随机信号。

2.2 ;LFSR设计。

如果n元布尔函数 f(x1,x2,…,x n)可以表示成n个变元x1,x2,

x3,…,xn的线性奇次函数:f(x1,x2,…,x n)=c n x n+c n-1x n-1+…c1x1f(x1,x2,…,x n)

=c n x n+c n-1x n-1+…c1x1其中c i=0或1,则以f(x1,x2,…,x n)为反馈函数的移位寄存器就叫做线性反馈移位寄存器(LFSR)[4]。

图2为n级线性反馈移位寄存器的一般结构形式。

其中A1,A2,…,A n是寄存器串联成的移位寄存器;h i是反馈控制,h i∈0,1。

为0不存在,为1则存在反馈控制,线性反馈移位寄存器的特征多项式为:

h(x)=x n+h1x n-1+h2x n-2+…+h n-1x+1(1)

产生线性反馈移位寄存器序列的n级移位寄存器,其特征多项式必须是n次本原多项式,也就是说特征多项式与输出序列的周期有密切的关系。

要设计LFSR,并使之输出序列具有最大的周期性,必须要找到本原多项式[5]。

以12Bit的TI芯片DAC902芯片(转换速度最高达到165M)为例,最少需要12bit位移位寄存器。

选取LFSR本原多项式为: x12+x6+x4+x+1,设计线性反馈移位寄存器取其并行输出作为DAC的编码,在QuartusII环境下用Verilog HDL硬件描述语言设计,输出的序列仿真如图3所示。

该序列发生器的输出信号是一个数字随机信号,在设计中,通过D/A转换器得到模拟信号。

若被测电路是数字输入,不需要再加D/A转换器,可根据实际需要直接将数字信号接到被测电路。

2.3 控制设计仿真

由图1可知,激励模块不仅要设计LFSR产生随机序列,还要产生控制时钟来控制DAC 工作,DAC902控制时序图如图4所示。

DAC控制起来比较容易,使能LFSR后,产生M序列并行输出到DAC数据端,然后控制器输出DAC控制时钟,上升沿时数据有效,DAC转换输出信号。

用硬件描述语言对激励模块数字部分进行设计,功能仿真如图5所示。

从图5中可以看出,在复位信号无效(即高电平)时,在系统时钟的驱动下,模块的输入使能置位有效时,LFSR并行有数据输出到DAC,并同时输出DAC控制时钟,来驱动DAC工作。

3结论

本文对BIST结构的测试激励进行设计,通过仿真结果可知,能够实现ADC的控制信号和数据,产生伪随机测试激励信号,为后续混合信号BIST测试结构设计打下基础。

参考文献:

[1]陈佳楠,马永涛,李松等. 多目标优化的多存储器内建自测试[J].电子测量与仪器学报.2020,01(34):193-198.

[2]孙永建,加等.混合BIST对象建模及结构分析[J].国外电子测量技术2010.05(29):21-23.

[3]刘伟,雷加.基于伪随机测试的模数混合信号内建自测试法[J].计算机工程与应用.2008,44(33).

[4]肖国镇,梁传甲,王育民.伪随机序列及其应用[M].国防工业出版社.1985.3

[5]王荣阳,刘福浩,李向阳紫外光通信误码率测试系统设计[J].半导体光电.2012.05:707-710

[6]杨舟,王红,杨士元.混合信号SOC联合测试方案[J].清华大学学报(自然科学版),2011.5(S1):1381-1387

[7]安宝森等.BIST电路在嵌入式非易失性存储器可靠性测试中的应用[J].电子设计工

程.2019,06(11):33-36

[8]谈恩民,贾亚平.用于数模混合电路中ADC测试的IP核设计[J].北京:微电子学,2016.12(6):849-851

作者简介:孙永建(1986—),男,研究方向:混合信号电路测试研究、嵌入式系统开发。