DDS正弦信号发生器设计外文文献

DDS信号发生器设计报告

基于DDS技术的全数控函数发生器【摘要】随着信息技术的发展,现代电子系统对波形发生器提出了更高的要求。

直接数字合成(Direct Digital Synthesize,DDS)是一种重要的频率合成技术,具有分辨率高,频率变换快等优点。

利用键盘输入波形频率,存入单片机,通过单片机控制1602液晶,让1602液晶显示输入频率的大小。

再通过单片机控制AD9851,再经过AD9851内部的相位累加器、相位寄存器、正弦查询表、DAC转换器、内部低通滤波器,然后经外部低通滤波器后,可输出正弦波,或者接到高速比较器上,可输出方波。

【关键词】 DDS;单片机;AD9851【Abstract】 Along with the information technology development, the modern electron system set a higher request to the profile generator.The direct digital synthesis (Direct Digital Synthesize, DDS) is one kind of important frequency synthesis technology, has the resolution to be high, frequency transformation quick and so on ing the keyboard entry profile frequency, stores the monolithic integrated circuit, controls 1602 liquid crystals through the monolithic integrated circuit, lets 1602 liquid crystal display input frequency the size.Again controls AD9851, AD9851through the monolithic integrated circuit after the phase accumulator, the phase register, the sine questionnaire, the DAC switch, after passes through the low pass filter, may output the sine wave, then receives on the high speed comparator, then may output the square-wave.【Key word】DDS; Entire numerical control; Monolithic integrated circuit; 目录前言 (3)1.方案论证与分析 (3)1.1主机的论证与分析 (3)1.2 DDS芯片的论证与分析 (3)1.3显示模块的论证与分析 (4)2.系统硬件设计 (4)2.1 系统设计 (4)2.2 单元电路设计 (5)2.2.1主机模块设计 (5)2.2.2电源模块设计 (5)2.2.3 DDS信号产生模块设计 (5)2.2.4 AD9851的控制字与控制时序 (7)2.2.5 DDS芯片输出频率 (8)2.2.6实现与PC机控制电路设计 (8)2.2.7键盘模块设计 (9)2.2.8显示模块设计 (10)2.2.9低通滤波器电路设计 (10)2.2.10波形调制设计 (11)3.系统软件设计 (11)3.1 主程序 (11)3.2信号频率数字预置子程序 (12)3.3 键盘扫描子程序 (12)3.4 液晶控制器操作流程 (13)4.系统测试 (13)4.1 测试仪器 (13)4.2 测试数据 (13)5.总结与体会 (14)6.参考文献 (14)附录 (14)附一:作品实物及测试图..................... . (14)附二:整机电路图 (16)附三:PCB图 (18)前言本设计采用DDS系统进行频率的直接数字控制。

DDS信号发生器设计源程序(DDSsignalgeneratordesignsource)

DDS信号发生器设计源程序(DDS signal generator design source)Program codePrescaler module1, set number:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY Zhishu ISPORT (M:OUT STD_LOGIC_VECTOR (31, DOWNTO, 0));END ENTITY;ARCHITECTURE, func, OF, Zhishu, ISBEGINM < = "00000101010111100110001110111000";END ARCHITECTURE;Accumulation step control module2, step selection:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY bcxuanze ISPORT (bcxzmaichong:IN STD_LOGIC);Bc:BUFFER STD_LOGIC_VECTOR (19, DOWNTO, 0);END ENTITY;ARCHITECTURE, func, OF, bcxuanze, ISSIGNAL bc1:STD_LOGIC_VECTOR (19, DOWNTO, 0): = "00000000000000000001"";SIGNAL bc2:STD_LOGIC_VECTOR (19, DOWNTO, 0): = "00000000000000001010"";SIGNAL bc3:STD_LOGIC_VECTOR (19, DOWNTO, 0): = "00000000000000110010"";SIGNAL bc4:STD_LOGIC_VECTOR (19, DOWNTO, 0): = "00000000000001100100"";SIGNAL bc5:STD_LOGIC_VECTOR (19, DOWNTO, 0): = "00000000001111101000"";SIGNAL tmp:STD_LOGIC_VECTOR (19, DOWNTO, 0);BEGINPROCESS (bcxzmaichong)BEGINIF, bcxzmaichong'EVENT, AND, bcxzmaichong ='1', THENBC < = bc1;BC1 < = bc2;BC2 < = bc3;BC3 < = bc4;Bc4 < = bc5;Bc5 < = bc;END IF;END PROCESS;END ARCHITECTURE;3, cumulative controlLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY kongzhi ISPORT (key:IN STD_LOGIC);Clr:IN STD_LOGIC;M:IN STD_LOGIC_VECTOR (19, DOWNTO, 0);Fout:BUFFER STD_LOGIC_VECTOR (19, DOWNTO, 0); END ENTITY;ARCHITECTURE, func, OF, kongzhi, ISBEGINPROCESS (key, CLR)BEGINIF CLR ='0'THENIF, key'EVENT, AND, key ='1', THEN IF fout > 10000 THENFout < = M;ELSEFout < = fout + M;END IF;END IF;ELSEFout < = "00000000000000000000"; END IF;END PROCESS;END ARCHITECTURE;Display module4 frequency displayLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY Xianshi ISPORT (foutin:IN STD_LOGIC_VECTOR (19, DOWNTO, 0); Clk:IN STD_LOGIC;Num1:OUT STD_LOGIC_VECTOR (6, DOWNTO, 0);Num2:OUT STD_LOGIC_VECTOR (6, DOWNTO, 0);Num3:OUT STD_LOGIC_VECTOR (6, DOWNTO, 0);Num4:OUT STD_LOGIC_VECTOR (6, DOWNTO, 0);Num5:OUT STD_LOGIC_VECTOR (6, DOWNTO, 0);END ENTITY;ARCHITECTURE, func, OF, Xianshi, ISSIGNAL dec:INTEGER;BEGINDec CONV_INTEGER (foutin); PROCESS (CLK)BEGIN如果clk'event和时钟=“1”然后病例10当0=>num1 < =“1000000”;当1=>num1 < =“1111001”;当2=>num1 < =“0100100”;当3=>num1 < =“0110000”;当4=>num1 < =“0011001”;当5=>num1 < =“0010010”;当6=>num1 <=“00000 10”;当7=>num1 < =“1111000”;当8=>num1 < =“0000000”;当9=>num1 < =“0010000”;当别人= > num1 < =“1111111”;案例;案例(DEC REM 100)/ 10是当0=>num2 < =“1000000”;当1=>num2 < =“1111001”;当2=>num2 < =“0100100”;当3=>num2 < =“0110000”;当4=>num2 < =“0011001”;当5=>num2 < =“0010010”;当6 = > < =“00000 10”num2;当7=>num2 < =“1111000”;当8=>num2 < =“0000000”;当9=>num2 < =“0010000”;当别人= > num1 < =“1111111”;案例;案例(DEC REM 1000)/ 100是当0=>小键盘数字3 < =“1000000”;当1=>小键盘数字3 < =“1111001”;当2=>小键盘数字3 < =“0100100”;当3=>小键盘数字3 < =“0110000”;当4=>小键盘数字3 < =“0011001”;当5=>小键盘数字3 < =“0010010”;当6 = > < =“00000 10”小键盘数字3;当7=>小键盘数字3 < =“1111000”;当8=>小键盘数字3 < =“0000000”;当9=>小键盘数字3 < =“0010000”;当别人= > num1 < =“1111111”;案例;案例(DEC REM 10000)/ 1000是当0=>NUM4 < =“1000000”;当1=>NUM4 < =“1111001”;当2=>NUM4 < =“0100100”;当3=>NUM4 < =“0110000”;当4=>NUM4 < =“0011001”;当5=>NUM4 < =“0010010”;当6=>NUM4 <=”00000 10”;当7=>NUM4 < =“1111000”;当8=>NUM4 < =“0000000”;当9=>NUM4 < =“0010000”;当别人= > num1 < =“1111111”;案例;十二月10000日是当0=> num5 < =“1000000”;当1=> num5 < =“1111001”;当2=> num5 < =“0100100”;当3=> num5 < =“0110000”;当4=> num5 < =“0011001”;当5=> num5 < =“0010010”;当6=> num5 < =“00000 10”;当7=> num5 < =“1111000”;当8=> num5 < =“0000000”;当9=> num5 < =“0010000”;当别人= > num1 < =“1111111”;案例;最后如果;结束进程;端架构;波形存储模块5、提取高8位图书馆的IEEE;使用ieee.std_logic_1164.all;使用ieee.std_logic_arith.all;使用ieee.std_logic_unsigned.all;实体转换为端口(zh_in:在std_logic_vector(19到0);zh_out:出std_logic_vector(7到0));终端实体;是建筑功能的转换开始过程(zh_in)开始zh_out(7)< = zh_in(19);an _ out (6) < = zh _ in (18)._ out (5)) = zh _ in (17)._ out) (4) = zh _ in (16).an _ out (3) < = zh _ in (15)._.) (2) < = zh _ in (14)._ out) (1) < = zh _ in (13).an _ out (0) < = zh _ in (12).end process;end architecture.6、方波生成library ieee;use ieee.std _ logic _ 1164.all.use ieee.std _ logic _ arith.all.use ieee.std _ logic _ unsigned.all.the entity fangboport (fb _ in std _ logic.in _ fbclk std logic;for all _ out std _ logic _ vector (7 downto 0). end entity.the architecture of fangbo funcbeginprocess for _, fbclk)beginif fbclk'event and fbclk =' 1 '.for i in 0 to 7 loopfor _ out (i) < = fb _.end loop;end if;end process;end architecture.7、四路选通library ieee;use ieee.std _ logic _ 1164.all.use ieee.std _ logic _ arith.all. use ieee.std _ logic _ unsigned.all. the company xuanzeport (xzmaichong: in std _ logic.input1: in std _ logic _ vector (7 downto 0). input2: in std _ logic _ vector (7 downto 0). input3: in std _ logic _ vector (7 downto 0). input4: in std _ logic _ vector (7 downto 0). output: out std _ logic _ vector (7 downto 0). end entity.the architecture of xuanze funcsignal count: integer range 0 to 3).beginprocess (xzmaichong)beginif xzmaichong'event and xzmaichong =' 1 '. count = count + 1.end if;if count = 0 thenoutput = input1.elsif count = 1 then output = input2. elsif count = 2 then output = input3. elseoutput = input4.end if;end process;end architecture.。

基于DDS的信号发生器的设计与开发

基于DDS的信号发生器的设计与开发The Design and Development of Function Generator Based on DDS作者:东南大学机械工程系冯建雨关键词:直接数字频率合成低通滤波器正弦波信号1 引言在频率合成(FS- Frequency Synthesis)领域中,常用的频率合成技术有:(1) 直接频率合成(DS);(2) 锁相环频率合成(PLL);(3) 直接数字频率合成(DDS)。

其中,直接数字频率合成(Direct Digital Frequency Synthesis-DDS)是近年来新的FS技术。

由于DDS具有超高速的频率转换时间,极高的频率分辨率和较低的相位噪声,在频率改变与调频时, DDS器件能够保持相位的连续,因此很容易实现频率、相位和幅度调制,此外还具有可编程控制的突出优点。

因此,直接数字频率合成器得到了越来越广泛的应用,成为当今电子系统及设备中频率源的首选器件。

本文在介绍DDS原理的基础上重点介绍利用DDS技术,采用单片机AT89C51控制AD9850芯片实现多功能函数发生器的设计方案。

2 DDS的基本原理DDS由相位累加器、正弦ROM表和数模转换器等组成,系统组成如图1所示。

在正弦ROM表中存储着一张正弦函数查询表,对应不同的瞬时相位码输出不同的幅度编码。

工作时往DDS中写入控制字ΔPhase到相位累加器并转化成瞬时相位,在外部参考时钟CLKIN的作用下,每个时钟周期相位累加器累加相位步进一次,对应的幅度编码输出给数模转换器(D/A),把数字量转化为模拟量,再通过低通滤波器平滑后得到最后需要的信号。

并且该模拟正弦波与一门限电压进行比较可得到同频率的方波时钟信号。

图1 DDS原理简图DDS输出信号的频率为最小频率分辨率为最小相位分辨率为式中, △phase为频率控制字, sysclk为系统时钟, CLKIN为DDS的输入参考时钟频率,N为频率寄存器的位数, M为相位偏移寄存器的位数。

基于DDS技术的正弦信号发生器的设计

基于DDS技术的正弦信号发生器的设计摘要:基于直接数字合成原理,采用单片机STC89C52RC为主控芯片、以可编程DDS集成芯片AD9851为核心,设计了一个正弦信号发生器,输出正弦波形幅度稳定可调,频率精度优于0.1Hz,最高输出频率可达70MHz。

关键词:DDS;信号发生器;AD9851引言信号发生器又称信号源或振荡器,它用于产生被测电路所需特定参数的电测试信号,在生产实践和科技领域中有着广泛应用。

传统的信号源一般采用RC振荡电路、LC振荡电路、石英晶体振荡电路或波形发生集成电路来实现,很难在较宽的频带范围内实现高质量、高频率精度和高稳定性波形的输出,且一般频率调节是通过调节电阻、电感、电容等参数来实现,难于实现高精度和数控调节。

利用直接数字合成技术(DDS)设计的波形发生器具有精度高、稳定性好、频率和波形易于控制等优点,因此,DDS技术越来越广泛地得到应用,成为现代频率合成技术的趋势。

本设计采用STC89C52RC单片机为主控芯片、以可编程DDS集成芯片AD9851为核心,设计了一种结构简单、精度较高、便携式的正弦信号发生器。

1 DDS技术简介DDS是一种运用数字技术来实现产生信号的方法,它从相位概念出发直接合成所需波形的一种频率合成技术。

它主要由三个部分组成:相位累加器、相位幅度转换、数模转换器(DAC)。

其工作原理如图1所示。

图1 DDS工作原理一个正弦波,虽然它的幅度不是线性的,但是它的相位却是线性增加的。

DDS正是利用了这一特点来产生正弦信号。

根据DDS的频率控制字的位数N,把360°平均分成了2N等份。

假设系统时钟为Fc,输出频率为Fout。

每次转动一个角度360°/2N,则可以产生一个频率为Fc/2N的正弦波的相位递增量。

那么只要选择恰当的频率控制字M,使得Fout/Fc=M/2N,就可以得到所需要的输出频率Fout,即Fout=Fc×M/2N。

通过相位累加器,得到合成Fout频率所对应的相位信息,然后相位幅度转换器把0°~360°的相位转换成相应相位的幅度值。

基于DDS的正弦波信号发生器的设计

me o . h s m f r i aywa e r e ea ra d i f r ei a d o i c dg a snh s e( t d T es t o bt r v f r g n rt n s ot ed s n b s ndr t ii l y tei r DDS h ye a r on o t s wa g e e t z )

tc e hno l y ve be n s use n de t i1A he e i a na l i f t yse ro r a e i lo g v n.The og ha e d ic s d i a . t or tc la yss he s t m pe f m nc s as i e o

2 1 年 8月 o1 繁 8期

电 子

测

试

E ECT L RONI E C T ST

Aug. 201 1 No. 8

基于DDS 的正 弦波信 号发 生器 的设 计★

崔唯佳 ,高磊 ,陈晓军

( 中北大学 信息探测与处理技术 研究所 ,山西 太原 0 0 5 ) 301

摘 要 :在频率合成领域 中, 直接数 字合成( DS是近年来 新的技术 ,它是从相位概 念出发直接合成所 需波形的 D )

中图 分 类 号 : TN9 5 9 2 +. 文献标识 码: A

D e i n gia r ns it r ba e on FPGA sg of di t lt a m t e s d

DDS正弦信号发生器设计外文文献

DDS devices to produce high-quality waveform: a simple, efficient and flexibleAbstract: Direct digital frequency synthesis (DDS) technology for the generation and regulation of high-quality waveforms, widely used in medical, industrial, instrumentation, communications, defense and many other areas. This article will briefly describe the technology, on its strengths and weaknesses, examine some application examples, and also introduced some new products that contribute to the promotion1.IntroductionA key requirement in many industries is an exact production, easy operation and quick change of different frequencies, different types of waveforms. Whether it is broadband transceiver requires low phase noise and excellent spurious-free dynamic performance of agile frequency source, or for industrial measurement and control system needs a stable frequency excitation, fast, easy and economical to produce adjustable waveform while maintaining phase continuity capabilities are critical to a design standard, which is what the advantages of direct digital frequency synthesis.2.Frequency synthesis taskThe growing congestion of the spectrum, coupled with lower power consumption, quality of never-ending demand for higher measuring equipment, these factors require the use of the new frequency range, requires a better use of existing frequency range. A result, the search for better control, in most cases, by means of frequency synthesizer for frequency generation. These devices use a given frequency, fC of to generate a target frequency (and phase) fOUT the general relationship can be simply expressed as:fOUT = εx× fCAmong them, the scale factor εx, sometimes known as the normalized frequency.The equation is usually gradual approximation of the real number algorithms. When the scale factor is a rational number, two relatively prime numbers (output frequency and reference frequency) than the harmonic. However, in most cases, εx may belong to a broader set of real numbers, the approximation process is within the acceptable range will be truncatedThe frequency synthesizer a practical way to achieve is the direct digital frequency synthesis (of DDFS), usually referred to as direct digital synthesis (DDS). This technique using digital data processing to generate a frequency and phase adjustable output, the output anda fixed frequency reference clock source fC. related. DDS architecture, the reference or the system clock frequency divided by a scale factor to produce the desired frequency, the scale factor is controlled by the binary tuning word programmable.In short, direct digital frequency synthesizer to convert a bunch of clock pulses into an analog waveform, usually a sine wave, triangle wave or square wave. Shown in Figure 1, its main parts: the phase accumulator (to produce the output waveform phase angle data), relative to digital converter, (above the phase data isconverted to the instantaneous output amplitude data), and digital-to-analog converter (DAC) (the magnitude of data into a sampled analog data points)Figure 2-1 DDS function of the system block diagram.For the sine wave output, relative to digital converter is usually a sine lookup table (Figure 2). Phase accumulator unit count N a relative to the frequency of fC, according to the following equation:The number of pulses of the fC:M is the resolution of the tuning word (24-48)N corresponds to the smallest increment of phase change of the phase accumulator output wordFigure2-2 Typical DDS architecture and signal path (with DACs).Changing N will immediately change the output phase and frequency, so the system has its own continuous phase characteristics, which is one of the key attributes of many applications. No loop settling time, which is different from the analog system, such as phase-locked loops (PLLs). DAC is usually a high-performance circuit, designed specifically for the DDS core (phase accumulator and phase amplitude converter). In most cases, the results of the device (usually single-chip) is generally referred to as the pure DDS or the C-DDS.Actual DDS devices are generally multiple registers, in order to achieve a different frequency and phasemodulation scheme. Such as phase register, their storage phase of increase in the output phase of the phase accumulator. In this way, the corresponding delay output sine wave phase in a phase tuning word. This is useful for phase modulation applications for communication systems. The resolution of the adder circuit determines the number of bits of the phase tuning word, therefore, also decided to delay the resolution.Integrated in a single device on the engine of a DDS and a DAC has both advantages and disadvantages, however, whether integrated or not, need a DAC to produce ultra-high purity high-quality analog signal. DAC will convert digital sinusoidal output to an analog sine wave may be single-ended or differential. Some of the key requirements for low phase noise, excellent wideband (WB) and narrowband (NB), spurious-free dynamic range (SFDR), and low power consumption. If the external device, the DAC must be fast enough to handle the signal, so the built-in parallel port device is very common.3.DDS and other solutionsThe frequency analog phase-locked loops (PLLs), clock generator, and the use of FPGA dynamic programming of the output of the DAC. By examining the spectrum of performance and power of these technologies, a simple comparison, Table 1 shows the qualitative results of the comparisonTable 3-1DDS with competing technologies - Advanced comparePower consumption Spectral purity RemarksDDS Low Middle Ease of tuningDiscrete DAC+FPGA Middle Middle-High With tuning capabilitiesAnalog PLL Milddle High Difficult tuningPhase-locked loop is a feedback loop and its components: a phase comparator, a divider and a pressure-controlled oscillator (VCO), phase comparator reference frequency and output frequency (usually the output frequency is N)frequency) were compared. The error voltage generated by the phase comparator is used to adjust the VCO, thus the output frequency. When the loop is established, the output frequency and / or phase with the reference frequency to maintain a precise relationship. PLL has long been considered in a particular frequency range, high fidelity and consistent signal low phase noise and high spurious free dynamic range (SFDR) are ideal for applications.PLL can not be precisely and quickly tuning the frequency output waveform, and the slow response, which limits their applicability for fast frequency hopping and part of the frequency shift keying and phase shift keying applications.Other programs, including integrated DDS engine field programmable gate arrays (FPGAs) - a synthetic sine wave output with the off-the-shelf DAC - though the PLL frequency-hopping problem can be solved, but there own shortcomings. The defects of the major systems work and interface power requirements, high cost, large size, and system developers must also consider the additional software, hardware and memory. For example, using the DDS engine option in the modern FPGA to generate the 10 MHz output signal dynamic range is 60 dB up to 72 kB memory space. In addition, designers need to accept and be familiar with thesubtle balance DDS core architecture. .From a practical point of view (see Table 2), thanks to the rapid development of CMOS technology and modern digital design techniques, as well as the improvement of the DAC topology, DDS technology has been able to achieve unprecedented low power consumption in a wide range of applications, spectrum performance and cost levels. Although the pure DDS products in performance and design flexibility to achieve the level of high-end DAC technology and FPGA, but the advantages of DDS in terms of size, power consumption, cost and simplicity, making it the primary choice for many applications.Table 3-2 Benchmark Analysis Summary - frequency generation technique (<50 MHz)Phase -locked loop DAC + FPGA DDS Spectral performance High High MiddleSystem power requirements High High MiddleDigital frequency tuning No Yes YesTuning response time High Low LowSolution size Middle High LowWaveform flexibility Low Middle HighCost Middle High LowDesign reuse Middle Low HighImplementation complexity Middle High LowAlso be noted that the DDS device for digital methods to produce the output waveform, it can simplify some of the architecture of the solution, or the waveform of digital programming to create the conditions. Usually with a sine wave to explain the functions and working principle of the DDS, but using modern DDS ICs can easily generate a triangle wave or square wave (clock) output, thereby eliminating the former case the lookup table, and the latter case the DAC the need to integrate a simple and accurate enough.4. Performance and limitations of the DDS4.1 Image and envelope: Sin (x) xx roll-offThe actual output of the DAC is not a continuous sine wave, but a series of pulses with a sinusoidal time envelope. The corresponding spectrum is a series of image and signal aliasing. Image along the sin (x) / x envelope distribution (see Figure 3 | margin | graph). The need for the filter to suppress frequencies outside the target band, but can not inhibit the high-level in the passband aliasing (for example, caused due to DAC non-linear)The Nyquist criterion requires that each cycle requires at least two sampling points in order to rebuild the desired output waveform. The Mirroring response arising from sampling the output frequency K, CLOCK ×OUT In this example, which CLOCK = 25 25 MHz and fOUT = 5 MHz, the first and second mirror frequency appear in (see Figure 3) fCLOCK × fOUT, o 20 MHz and 30 MHz. The third and fourth mirror frequency at 45 MHz and 55 MHz. Note, sin (x) / x value of zero at multiples of the sampling frequency.When fOUT greater than the Nyquist bandwidth (1/2 f CLOCK), the first mirror frequency will appear in the Nyquist bandwidth, the occurrence of aliasing (such as 15 MHz signal aliasing down to 10 MHz). Can not use the traditional quist anti-aliasing filter to filter out aliasing mirror frequency from the outputFigure 4-1 Sin, in Figure 3.DDS, (x) / x roll-off.In a typical DDS application, the use of a low-pass filter to suppress the mirror frequency response of the output spectrum. To make the low-pass filter cutoff frequency to remain at reasonable levels, and keep it simple filter design, a feasible approach is the use of an economic low-pass output filter bandwidth limited to about 40% of the frequency of clock.Any given mirror frequency relative to the amplitude of the fundamental formula of sin (x) / x calculation. Because the function of the frequency roll-off, the basic output of the amplitude and the output frequency is inversely proportional to decrease; in the DDS system, reduce the amount of DC-Nyquist bandwidth range of -3.92 dB.Significant reduction in frequency in the first mirror - the fundamental 3 dB range. In order to simplify the DDS application filtering, frequency plan must be formulated and analyzed to mirror the frequency and magnitude of the sin (x) / x response in the OUT and CLOCK target frequency spectrum requirements. Other unwanted frequencies in the output spectrum (such as integral and differential linearity error of the DAC, the surge of energy associated with the DAC and clock feed through noise) does not follow the sin (x) / x roll-off response. These unwanted frequencies will be harmonic and spurious energy in the output spectrum in many places - but its magnitude is generally far below the mirror frequency response. DDS devices to the general background noise, substrate noise, thermal noise effects, ground coupling and other signal source coupling factor cumulative portfolio decisions. DDS devices, the noise floor performance of stray and jitter by the circuit board layout, power quality, and - most importantly - Enter the profound impact of the quality of the reference clock.4.2ShakeThe edge of the perfect clock source will be the precise time interval, the interval will never change. Of course, this is not possible; even the best oscillator is also the ideal components constitute, with noise and other defects. Quality and low phase noise crystal oscillator jitter picosecond, and is built up from one millionthe number of clock edge. The factors leading to jitter external interference, thermal noise, the oscillator circuit instability and power, ground and output connections bring, all these factors will interfere with the timing characteristics of the oscillator. In addition, the oscillator by the external magnetic field or electric field and the nearby transmitter RF interference. Oscillator circuit, a simple amplifier, inverter or buffer to signal additional jitter.Therefore, the choice of a low-jitter, and the edge of steep stable reference clock oscillator is critical. Higher frequency reference clock allows a larger sample, and divide to some extent, reduce the jitter, because the signal to divide a long time to produce the same amount of jitter, which can reduce the jitter on the signal percentage.4.3 Noise - including the phase noiseThe sampling system noise depends on many factors, the most important factor is the reference clock jitter, this jitter performance of phase noise on fundamental signal. In the DDS system, the register output of the truncated phase may bring the system error code. The binary word does not lead to the truncation error. But for non-binary word, phase noise truncation error in the spectrum spurious. Spurious frequency / amplitude depends on the code word. Quantification and linearity error of the DAC will be brought to the system harmonic noise. Time-domain error (such as owed to the red / overshoot and code errors) will increase the output signal distortion.5. Application5.1 DDS applications can be divided into two categories:Require agile frequency source for data coding and modulation applications, communications and radar systemsRequire measurement of the universal frequency synthesizer features and programmable tuning, scanning, and motivational skills, industrial and optical applicationsBoth cases, the trend toward higher spectral purity (low phase noise and higher spurious free dynamic range), also low power and small size requirements to accommodate the remote ordemand for battery-powered devices.5.2 Modulation / data encoding, and synchronization of the DDSDDS products first appeared on the radar and military applications and the development of some of its characteristics (performance improvements, cost and size, etc.) DDS technology is becoming more prevalent in the modulation and data encoding applications. This section will discuss the two data encoding scheme in the DDS system.5.3 Binary frequency shift keyingThe launch of the data is a continuous carrier frequency in two discrete frequency (binary one, ie, pass number, a binary 0, namely, the transformation between the space). Figure 4 shows the relationship between the data and transmit signals.Figure 5-1 binary FSK modulation.Binary 1 and 0 for two different frequencies f0 and f1, respectively. This encoding scheme can be easily DDS device. On behalf of the output frequency of the DDS frequency tuning word change to f0 and f1, will launch the 1 and 0. To transform the output frequency shall dedicated pin FSELECT, containing the appropriate tuning word registers (see Figure 5)Figure 5-2 AD9834 or AD9838 DDS tuning word selector realization of the FSK encoding.5.4 Phase shift keying (PSK)In PSK, the carrier frequency remains the same, by changing the phase of the transmitted signal to transmit information. Can take advantage of a variety of programs to achieve PSK,. The easiest way is often referred to as binary PSK (BPSK), using only two signal phase: 0 ° (logic 1) and 180 ° (logic 0). Members state depends on the status of the former one. If the wave phase remains unchanged, the signal state will remain the same (low or high). Wave phase change 180 °, ie, phase inversion, the signal state will change (low into high or high to low). PSK coding in DDS products can be easily achieved, because most devices have a separate input register (phase register), and phase values can be loaded. This value is added directly to the carrier phase, without changing its frequency. Change the contents of the register will be modulated carrier phase, resulting in a PSK output. For applications that require high-speed modulation, built-in phase register of the AD9834 and AD9838 allow PSELECT pin signal transformation, according to need modulated carrierin the preloaded phase registers.The more complex the PSK four or eight-wave phase. Thus, whenever the phase change of binary data transfer rate will be higher than the BPSK modulation. In the four-phase modulation (Quadrature PSK), in the phase angle of 0 ° to +90 °, -90 ° and +180 °; each phase to transform the two signals may represent a factor AD9830, AD9831, AD9832, and the AD9835 provides four phase registers, can be continuously updated register of different phase shift, the complex phase modulation scheme.5.5 The use of synchronous mode of multiple DDS devices to achieve the I / QMultiple DDS components to achieve the many applications of the I / Q sine wave or square wave signal of known phase relationship between two or more synchronous mode. A common example is the same phase and quadrature modulation (I / Q) in this technique, the phase angle of 0 ° and 90 ° from the carrier frequency signal information. To run two separate DDS components, you can use the same source clock to output can directly control and manipulate the signal of the phase relationship. In Figure 6, with a reference clock on the AD9838 device programming; the RESET pin is used to update the two devices. In this way, you can achieve a simple I / Q modulationRESET after power and initialized before any data to the DDS transmission. DDS output results can be placed in a known phase, making it a common reference point of view, in order to synchronize multiple DDS devices. When new data is sent to multiple DDS devices, the DDS can remain relevant phase relationship, or by the phase offset register can predict the relative phase shift between the adjustments of multiple DDS. The AD983x series of DDS products have a 12 phase resolution, the effective resolution of 0.1 °.Figure 5-3 Synchronize the two DDS components.DDS器件产生高质量波形:简单、高效而灵活摘要:直接数字频率合成(DDS)技术用于产生和调节高质量波形,广泛用于医学、工业、仪器仪表、通信、国防等众多领域。

基于DDS技术的正弦信号发生器设计

ma c f ie w v e e a rb s d o 9 5 i u h a v t e s h g r q e c e ou i d h n eo s a e g n r t a e n AD 8 0 w t s c d a a sa ih f u n y r s lt n a i a n o h n g e o n 【

输 出信号稳 定不 失真 ,控制 灵活 ,具 有广 泛的 实际应 用前景 。 关键词 :D S D ;正弦 信号发 生器 ;A 95 D 80

De i n o i e wa e g n r t r b s d o sg f sn v e e a o a e n DDS t c n l g e h oo y

0 引言

近年来 , 接数字频率 合成器 ( icDga r— 直 Dr t it Fe e il

q ec yte s简 称 D S或 D Байду номын сангаас ) 着 飞 速 的发 unySn s h i D DS 有

不 同 的幅度 编码 。D A转换 器将 数字 量形 式 的波形 /

幅值转换成模拟量形式 。低通滤波器用于滤除不需

维普资讯

2 0 年第1 07 期

中图分类号 :N 1 T 70 文献标识码 : A 文章 编号 :09 52 2c )1 0 1 3 10 —25 (0r 0 — 04—0 7

基 于 D S技 术 的正 弦信 号 发 生器 设 计 D

施 羽 暇 威 ,吕 ,李 一晨

p e iin. e o tu se s o c n r l h s h e lt d i h sw d p l ain i e ft r rcso T up ti a y t o t , a ih rai a t a e a p i t n t u u e. h o g yn i c o h Ke r s: DDS; sn v e eao ; AD9 5 y wo d i ewa e g n r tr 80

基于DDS的信号发生器的设计的相关英文文献

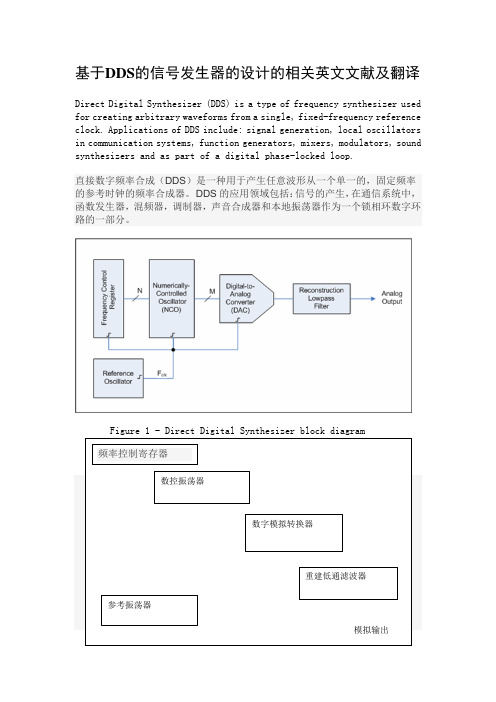

基于DDS的信号发生器的设计的相关英文文献及翻译Direct Digital Synthesizer (DDS) is a type of frequency synthesizer used for creating arbitrary waveforms from a single, fixed-frequency reference clock. Applications of DDS include: signal generation, local oscillators in communication systems, function generators, mixers, modulators,sound synthesizers and as part of a digital phase-locked loop.直接数字频率合成(DDS)是一种用于产生任意波形从一个单一的,固定频率的参考时钟的频率合成器。

DDS的应用领域包括:信号的产生,在通信系统中,函数发生器,混频器,调制器,声音合成器和本地振荡器作为一个锁相环数字环路的一部分。

Figure 1 - Direct Digital Synthesizer block diagram图1 - 直接数字频率合成器框图A basic Direct Digital Synthesizer consists of a frequency reference (often a crystal or SAW oscillator), a numerically controlled oscillator (NCO) and a digital-to-analog converter (DAC) as shown in Figure 1.The reference provides a stable time base for the system and determines the frequency accuracy of the DDS. It provides the clock to the NCO which produces at its output a discrete-time, quantized version of the desired output waveform (often a sinusoid) whose period is controlled by the digital word contained in the Frequency Control Register. The sampled, digital waveform is converted to an analog waveform by the DAC. The output reconstruction filter rejects the spectral replicas produced by the zero-order hold inherent in the analog conversion process.A DDS has many advantages over its analog counterpart, the phase-locked loop (PLL), including much better frequency agility, improved phase noise, and precise control of the output phase across frequency switching transitions. Disadvantages include spurious due mainly to truncation effects in the NCO, crossing spurious resulting from high order (>1) Nyquist (尼奎斯特定理) images, and a higher noise floor at large frequency offsets due mainly to the Digital-to-analog converter.Because a DDS is a sampled system, in addition to the desired waveform at output frequency Fout, Nyquist images are also generated (the primaryimage is at Fclk -Fout, where Fclkis the reference clock frequency). In orderto reject these undesired images, a DDS is generally used in conjunction with an analog reconstruction lowpass filter as shown in Figure 1.The output frequency of a DDS is determined by the value stored in the frequency control register (FCR) (see Fig.1), which in turn controls the NCO's phase accumulator step size. Because the NCO operates in the discrete-time domain, it changes frequency instantaneously at the clock edge coincident with a change in the value stored in the FCR. The DDS output frequency settling time is determined mainly by the phase response of the reconstruction filter. An ideal reconstruction filter with a linear phase response (meaning the output is simply a delayed version of the input signal) would allow instantaneous frequency response at its output because a linear system can not create frequencies not present at its input.The superior close-in phase noise performance of a DDS stems from the fact that it is a feed-forward system. In a traditional phase locked loop (PLL), the frequency divider in the feedback path acts to multiply the phase noise of the reference oscillator and, within the PLL loop bandwidth, impresses this excess noise onto the VCO output. A DDS on the other hand, reduces the reference clock phase noise by the ratio f clk/f out,because its output is derived by fractional division of the clock. Reference clock jitter translates directly to the output, but this jitter is a smaller percentage of the output period (by the ratio above). Since the maximum output frequency is limited to f clk/2, the output phase noise at close-in offsets is always at least 6dB below the reference clock phase-noise.At offsets far removed from the carrier, the phase-noise floor of a DDS is determined by the power sum of the DAC quantization noise floor and the reference clock phase noise floor.一个DDS以上的锁相回路(PLL),其模拟对应,许多优势,包括更好的频率灵活性,提高了相位噪声,整个频率转换开关的输出相位的精确控制。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DDS devices to produce high-quality waveform: a simple, efficient and flexibleAbstract: Direct digital frequency synthesis (DDS) technology for the generation and regulation of high-quality waveforms, widely used in medical, industrial, instrumentation, communications, defense and many other areas. This article will briefly describe the technology, on its strengths and weaknesses, examine some application examples, and also introduced some new products that contribute to the promotion1.IntroductionA key requirement in many industries is an exact production, easy operation and quick change of different frequencies, different types of waveforms. Whether it is broadband transceiver requires low phase noise and excellent spurious-free dynamic performance of agile frequency source, or for industrial measurement and control system needs a stable frequency excitation, fast, easy and economical to produce adjustable waveform while maintaining phase continuity capabilities are critical to a design standard, which is what the advantages of direct digital frequency synthesis.2.Frequency synthesis taskThe growing congestion of the spectrum, coupled with lower power consumption, quality of never-ending demand for higher measuring equipment, these factors require the use of the new frequency range, requires a better use of existing frequency range. A result, the search for better control, in most cases, by means of frequency synthesizer for frequency generation. These devices use a given frequency, fC of to generate a target frequency (and phase) fOUT the general relationship can be simply expressed as:fOUT = εx× fCAmong them, the scale factor εx, sometimes known as the normalized frequency.The equation is usually gradual approximation of the real number algorithms. When the scale factor is a rational number, two relatively prime numbers (output frequency and reference frequency) than the harmonic. However, in most cases, εx may belong to a broader set of real numbers, the approximation process is within the acceptable range will be truncatedThe frequency synthesizer a practical way to achieve is the direct digital frequency synthesis (of DDFS), usually referred to as direct digital synthesis (DDS). This technique using digital data processing to generate a frequency and phase adjustable output, the output anda fixed frequency reference clock source fC. related. DDS architecture, the reference or the system clock frequency divided by a scale factor to produce the desired frequency, the scale factor is controlled by the binary tuning word programmable.In short, direct digital frequency synthesizer to convert a bunch of clock pulses into an analog waveform, usually a sine wave, triangle wave or square wave. Shown in Figure 1, its main parts: the phase accumulator (to produce the output waveform phase angle data), relative to digital converter, (above the phase data isconverted to the instantaneous output amplitude data), and digital-to-analog converter (DAC) (the magnitude of data into a sampled analog data points)Figure 2-1 DDS function of the system block diagram.For the sine wave output, relative to digital converter is usually a sine lookup table (Figure 2). Phase accumulator unit count N a relative to the frequency of fC, according to the following equation:The number of pulses of the fC:M is the resolution of the tuning word (24-48)N corresponds to the smallest increment of phase change of the phase accumulator output wordFigure2-2 Typical DDS architecture and signal path (with DACs).Changing N will immediately change the output phase and frequency, so the system has its own continuous phase characteristics, which is one of the key attributes of many applications. No loop settling time, which is different from the analog system, such as phase-locked loops (PLLs). DAC is usually a high-performance circuit, designed specifically for the DDS core (phase accumulator and phase amplitude converter). In most cases, the results of the device (usually single-chip) is generally referred to as the pure DDS or the C-DDS.Actual DDS devices are generally multiple registers, in order to achieve a different frequency and phasemodulation scheme. Such as phase register, their storage phase of increase in the output phase of the phase accumulator. In this way, the corresponding delay output sine wave phase in a phase tuning word. This is useful for phase modulation applications for communication systems. The resolution of the adder circuit determines the number of bits of the phase tuning word, therefore, also decided to delay the resolution.Integrated in a single device on the engine of a DDS and a DAC has both advantages and disadvantages, however, whether integrated or not, need a DAC to produce ultra-high purity high-quality analog signal. DAC will convert digital sinusoidal output to an analog sine wave may be single-ended or differential. Some of the key requirements for low phase noise, excellent wideband (WB) and narrowband (NB), spurious-free dynamic range (SFDR), and low power consumption. If the external device, the DAC must be fast enough to handle the signal, so the built-in parallel port device is very common.3.DDS and other solutionsThe frequency analog phase-locked loops (PLLs), clock generator, and the use of FPGA dynamic programming of the output of the DAC. By examining the spectrum of performance and power of these technologies, a simple comparison, Table 1 shows the qualitative results of the comparisonTable 3-1DDS with competing technologies - Advanced comparePower consumption Spectral purity RemarksDDS Low Middle Ease of tuningDiscrete DAC+FPGA Middle Middle-High With tuning capabilitiesAnalog PLL Milddle High Difficult tuningPhase-locked loop is a feedback loop and its components: a phase comparator, a divider and a pressure-controlled oscillator (VCO), phase comparator reference frequency and output frequency (usually the output frequency is N)frequency) were compared. The error voltage generated by the phase comparator is used to adjust the VCO, thus the output frequency. When the loop is established, the output frequency and / or phase with the reference frequency to maintain a precise relationship. PLL has long been considered in a particular frequency range, high fidelity and consistent signal low phase noise and high spurious free dynamic range (SFDR) are ideal for applications.PLL can not be precisely and quickly tuning the frequency output waveform, and the slow response, which limits their applicability for fast frequency hopping and part of the frequency shift keying and phase shift keying applications.Other programs, including integrated DDS engine field programmable gate arrays (FPGAs) - a synthetic sine wave output with the off-the-shelf DAC - though the PLL frequency-hopping problem can be solved, but there own shortcomings. The defects of the major systems work and interface power requirements, high cost, large size, and system developers must also consider the additional software, hardware and memory. For example, using the DDS engine option in the modern FPGA to generate the 10 MHz output signal dynamic range is 60 dB up to 72 kB memory space. In addition, designers need to accept and be familiar with thesubtle balance DDS core architecture. .From a practical point of view (see Table 2), thanks to the rapid development of CMOS technology and modern digital design techniques, as well as the improvement of the DAC topology, DDS technology has been able to achieve unprecedented low power consumption in a wide range of applications, spectrum performance and cost levels. Although the pure DDS products in performance and design flexibility to achieve the level of high-end DAC technology and FPGA, but the advantages of DDS in terms of size, power consumption, cost and simplicity, making it the primary choice for many applications.Table 3-2 Benchmark Analysis Summary - frequency generation technique (<50 MHz)Phase -locked loop DAC + FPGA DDS Spectral performance High High MiddleSystem power requirements High High MiddleDigital frequency tuning No Yes YesTuning response time High Low LowSolution size Middle High LowWaveform flexibility Low Middle HighCost Middle High LowDesign reuse Middle Low HighImplementation complexity Middle High LowAlso be noted that the DDS device for digital methods to produce the output waveform, it can simplify some of the architecture of the solution, or the waveform of digital programming to create the conditions. Usually with a sine wave to explain the functions and working principle of the DDS, but using modern DDS ICs can easily generate a triangle wave or square wave (clock) output, thereby eliminating the former case the lookup table, and the latter case the DAC the need to integrate a simple and accurate enough.4. Performance and limitations of the DDS4.1 Image and envelope: Sin (x) xx roll-offThe actual output of the DAC is not a continuous sine wave, but a series of pulses with a sinusoidal time envelope. The corresponding spectrum is a series of image and signal aliasing. Image along the sin (x) / x envelope distribution (see Figure 3 | margin | graph). The need for the filter to suppress frequencies outside the target band, but can not inhibit the high-level in the passband aliasing (for example, caused due to DAC non-linear)The Nyquist criterion requires that each cycle requires at least two sampling points in order to rebuild the desired output waveform. The Mirroring response arising from sampling the output frequency K, CLOCK ×OUT In this example, which CLOCK = 25 25 MHz and fOUT = 5 MHz, the first and second mirror frequency appear in (see Figure 3) fCLOCK × fOUT, o 20 MHz and 30 MHz. The third and fourth mirror frequency at 45 MHz and 55 MHz. Note, sin (x) / x value of zero at multiples of the sampling frequency.When fOUT greater than the Nyquist bandwidth (1/2 f CLOCK), the first mirror frequency will appear in the Nyquist bandwidth, the occurrence of aliasing (such as 15 MHz signal aliasing down to 10 MHz). Can not use the traditional quist anti-aliasing filter to filter out aliasing mirror frequency from the outputFigure 4-1 Sin, in Figure 3.DDS, (x) / x roll-off.In a typical DDS application, the use of a low-pass filter to suppress the mirror frequency response of the output spectrum. To make the low-pass filter cutoff frequency to remain at reasonable levels, and keep it simple filter design, a feasible approach is the use of an economic low-pass output filter bandwidth limited to about 40% of the frequency of clock.Any given mirror frequency relative to the amplitude of the fundamental formula of sin (x) / x calculation. Because the function of the frequency roll-off, the basic output of the amplitude and the output frequency is inversely proportional to decrease; in the DDS system, reduce the amount of DC-Nyquist bandwidth range of -3.92 dB.Significant reduction in frequency in the first mirror - the fundamental 3 dB range. In order to simplify the DDS application filtering, frequency plan must be formulated and analyzed to mirror the frequency and magnitude of the sin (x) / x response in the OUT and CLOCK target frequency spectrum requirements. Other unwanted frequencies in the output spectrum (such as integral and differential linearity error of the DAC, the surge of energy associated with the DAC and clock feed through noise) does not follow the sin (x) / x roll-off response. These unwanted frequencies will be harmonic and spurious energy in the output spectrum in many places - but its magnitude is generally far below the mirror frequency response. DDS devices to the general background noise, substrate noise, thermal noise effects, ground coupling and other signal source coupling factor cumulative portfolio decisions. DDS devices, the noise floor performance of stray and jitter by the circuit board layout, power quality, and - most importantly - Enter the profound impact of the quality of the reference clock.4.2ShakeThe edge of the perfect clock source will be the precise time interval, the interval will never change. Of course, this is not possible; even the best oscillator is also the ideal components constitute, with noise and other defects. Quality and low phase noise crystal oscillator jitter picosecond, and is built up from one millionthe number of clock edge. The factors leading to jitter external interference, thermal noise, the oscillator circuit instability and power, ground and output connections bring, all these factors will interfere with the timing characteristics of the oscillator. In addition, the oscillator by the external magnetic field or electric field and the nearby transmitter RF interference. Oscillator circuit, a simple amplifier, inverter or buffer to signal additional jitter.Therefore, the choice of a low-jitter, and the edge of steep stable reference clock oscillator is critical. Higher frequency reference clock allows a larger sample, and divide to some extent, reduce the jitter, because the signal to divide a long time to produce the same amount of jitter, which can reduce the jitter on the signal percentage.4.3 Noise - including the phase noiseThe sampling system noise depends on many factors, the most important factor is the reference clock jitter, this jitter performance of phase noise on fundamental signal. In the DDS system, the register output of the truncated phase may bring the system error code. The binary word does not lead to the truncation error. But for non-binary word, phase noise truncation error in the spectrum spurious. Spurious frequency / amplitude depends on the code word. Quantification and linearity error of the DAC will be brought to the system harmonic noise. Time-domain error (such as owed to the red / overshoot and code errors) will increase the output signal distortion.5. Application5.1 DDS applications can be divided into two categories:Require agile frequency source for data coding and modulation applications, communications and radar systemsRequire measurement of the universal frequency synthesizer features and programmable tuning, scanning, and motivational skills, industrial and optical applicationsBoth cases, the trend toward higher spectral purity (low phase noise and higher spurious free dynamic range), also low power and small size requirements to accommodate the remote ordemand for battery-powered devices.5.2 Modulation / data encoding, and synchronization of the DDSDDS products first appeared on the radar and military applications and the development of some of its characteristics (performance improvements, cost and size, etc.) DDS technology is becoming more prevalent in the modulation and data encoding applications. This section will discuss the two data encoding scheme in the DDS system.5.3 Binary frequency shift keyingThe launch of the data is a continuous carrier frequency in two discrete frequency (binary one, ie, pass number, a binary 0, namely, the transformation between the space). Figure 4 shows the relationship between the data and transmit signals.Figure 5-1 binary FSK modulation.Binary 1 and 0 for two different frequencies f0 and f1, respectively. This encoding scheme can be easily DDS device. On behalf of the output frequency of the DDS frequency tuning word change to f0 and f1, will launch the 1 and 0. To transform the output frequency shall dedicated pin FSELECT, containing the appropriate tuning word registers (see Figure 5)Figure 5-2 AD9834 or AD9838 DDS tuning word selector realization of the FSK encoding.5.4 Phase shift keying (PSK)In PSK, the carrier frequency remains the same, by changing the phase of the transmitted signal to transmit information. Can take advantage of a variety of programs to achieve PSK,. The easiest way is often referred to as binary PSK (BPSK), using only two signal phase: 0 ° (logic 1) and 180 ° (logic 0). Members state depends on the status of the former one. If the wave phase remains unchanged, the signal state will remain the same (low or high). Wave phase change 180 °, ie, phase inversion, the signal state will change (low into high or high to low). PSK coding in DDS products can be easily achieved, because most devices have a separate input register (phase register), and phase values can be loaded. This value is added directly to the carrier phase, without changing its frequency. Change the contents of the register will be modulated carrier phase, resulting in a PSK output. For applications that require high-speed modulation, built-in phase register of the AD9834 and AD9838 allow PSELECT pin signal transformation, according to need modulated carrierin the preloaded phase registers.The more complex the PSK four or eight-wave phase. Thus, whenever the phase change of binary data transfer rate will be higher than the BPSK modulation. In the four-phase modulation (Quadrature PSK), in the phase angle of 0 ° to +90 °, -90 ° and +180 °; each phase to transform the two signals may represent a factor AD9830, AD9831, AD9832, and the AD9835 provides four phase registers, can be continuously updated register of different phase shift, the complex phase modulation scheme.5.5 The use of synchronous mode of multiple DDS devices to achieve the I / QMultiple DDS components to achieve the many applications of the I / Q sine wave or square wave signal of known phase relationship between two or more synchronous mode. A common example is the same phase and quadrature modulation (I / Q) in this technique, the phase angle of 0 ° and 90 ° from the carrier frequency signal information. To run two separate DDS components, you can use the same source clock to output can directly control and manipulate the signal of the phase relationship. In Figure 6, with a reference clock on the AD9838 device programming; the RESET pin is used to update the two devices. In this way, you can achieve a simple I / Q modulationRESET after power and initialized before any data to the DDS transmission. DDS output results can be placed in a known phase, making it a common reference point of view, in order to synchronize multiple DDS devices. When new data is sent to multiple DDS devices, the DDS can remain relevant phase relationship, or by the phase offset register can predict the relative phase shift between the adjustments of multiple DDS. The AD983x series of DDS products have a 12 phase resolution, the effective resolution of 0.1 °.Figure 5-3 Synchronize the two DDS components.DDS器件产生高质量波形:简单、高效而灵活摘要:直接数字频率合成(DDS)技术用于产生和调节高质量波形,广泛用于医学、工业、仪器仪表、通信、国防等众多领域。