逻辑器件选型指导书

穆勒-元器件选型手册

AC/DC100~250V(AS和AN型) ·DC24~48V(AH型)

DC24~60V(AS和AN型)

基本的保护功能(长延时/短延时/瞬时/接地故障)不带 控制电源一样可以正常操作

·可用

·可用

·N型

·N型

电话:028-86703201 传真:028-86703203

2009.11 版本

如有改动,恕不事先通知

样本编码10310000784

2009.11 印刷

上海

电力产品总图

超高压GIS

中压环网柜(CB型)

40.5kV 开关柜

中压环网柜

PROMEC 40.5kV 真空断路器

户外柱上负荷开关 户外环网开关柜

变压器

金属封闭开关柜

箱式变电站

负荷开关

变压器

凯装式金属封闭开关柜

GIPAM 115 综合数字保护装置

PROMEC 真空断路器

真空接触器

GIMAC-II plus 电机保护控制装置

GIPAM 2200 综合数字保护装置

DPR 综合数字保护装置

工控产品 (接触器、热过载继电器、电动机启动器)

Susol空气断路器

欠压线圈额定电压 不带欠压线圈

*UVT延时模块可用于AC/DC48V以上

附件

脱扣报警触头1a+ 手动复位按钮 脱扣报警触头2a+ 手动复位按钮 脱扣报警触头1a+ 手动复位按钮+远程复位开关 脱扣报警触头1a+ 手动复位按钮+远程复位开关 AL+自动复位 A2+自动复位 A3+自动复位 A4+自动复位 计数器 完全储能通讯触点 分合闸按钮锁 机械联锁 门联锁或机械操作位置开关 圆柱锁 三锁两钥匙 双重锁定钥匙锁 准备合闸开关 温度报警 自动释能机构 双分励线圈

电子行业产品开发作业指导书

电子行业产品开发作业指导书第1章产品开发概述 (4)1.1 产品开发流程 (4)1.1.1 市场调研 (4)1.1.2 概念设计 (4)1.1.3 详细设计 (4)1.1.4 样机制造与测试 (4)1.1.5 优化改进 (4)1.1.6 批量生产 (4)1.1.7 市场推广与售后服务 (4)1.2 电子行业产品发展趋势 (5)1.2.1 智能化 (5)1.2.2 互联网化 (5)1.2.3 节能环保 (5)1.2.4 轻薄化 (5)1.2.5 高功能 (5)1.3 产品开发策略 (5)1.3.1 技术创新 (5)1.3.2 市场导向 (5)1.3.3 合作共赢 (5)1.3.4 品牌建设 (5)1.3.5 人才培养 (5)第2章市场调研与分析 (5)2.1 市场调研方法 (5)2.1.1 文献调研 (6)2.1.2 问卷调查 (6)2.1.3 访谈调研 (6)2.1.4 网络数据分析 (6)2.1.5 实地考察 (6)2.2 竞品分析 (6)2.2.1 确定竞品范围 (6)2.2.2 收集竞品信息 (6)2.2.3 分析竞品优劣势 (6)2.2.4 竞品策略借鉴 (6)2.3 用户需求挖掘 (6)2.3.1 用户画像构建 (7)2.3.2 用户访谈与观察 (7)2.3.3 用户行为分析 (7)2.3.4 用户反馈收集 (7)第3章产品规划 (7)3.1 产品定位 (7)3.1.1 市场定位 (7)3.1.3 应用场景 (7)3.1.4 产品优势 (8)3.2 产品功能设计 (8)3.2.1 基本功能 (8)3.2.2 高级功能 (8)3.3 产品形态与类别 (8)3.3.1 形态 (8)3.3.2 类别 (8)第4章硬件开发 (9)4.1 电路设计基础 (9)4.1.1 电路设计原则 (9)4.1.2 电路设计流程 (9)4.1.3 电路设计注意事项 (9)4.2 元器件选型 (9)4.2.1 元器件选型原则 (9)4.2.2 元器件选型流程 (9)4.3 硬件调试与验证 (10)4.3.1 硬件调试方法 (10)4.3.2 硬件验证方法 (10)4.3.3 调试与验证注意事项 (10)第5章软件开发 (10)5.1 软件架构设计 (10)5.1.1 架构概述 (10)5.1.2 架构设计原则 (10)5.1.3 架构设计方法 (10)5.2 编程语言与工具 (11)5.2.1 编程语言选择 (11)5.2.2 开发工具与环境 (11)5.2.3 编码规范 (11)5.3 软件测试与优化 (11)5.3.1 测试策略 (11)5.3.2 测试工具与方法 (11)5.3.3 优化策略 (12)第6章用户体验设计 (12)6.1 设计原则与方法 (12)6.1.1 设计原则 (12)6.1.2 设计方法 (12)6.2 界面设计 (13)6.2.1 视觉设计 (13)6.2.2 布局设计 (13)6.2.3 内容设计 (13)6.3 人机交互 (13)6.3.1 交互逻辑 (13)第7章结构设计 (14)7.1 结构设计基础 (14)7.1.1 设计原则 (14)7.1.2 设计流程 (14)7.1.3 设计规范 (14)7.2 材料选择与应用 (14)7.2.1 材料选择原则 (14)7.2.2 常用材料 (15)7.2.3 材料应用实例 (15)7.3 结构仿真与优化 (15)7.3.1 结构仿真分析 (15)7.3.2 结构优化设计 (15)7.3.3 仿真与优化软件 (15)第8章生产工艺与制造 (16)8.1 电子制造工艺 (16)8.1.1 工艺流程规划 (16)8.1.2 印刷电路板制造 (16)8.1.3 元器件焊接工艺 (16)8.1.4 组装与调试 (16)8.2 质量控制与管理 (16)8.2.1 质量管理体系 (16)8.2.2 质量检验与控制 (16)8.2.3 不良品处理 (16)8.2.4 持续改进 (16)8.3 供应链管理 (17)8.3.1 供应商选择与评价 (17)8.3.2 物料采购管理 (17)8.3.3 库存管理 (17)8.3.4 物流配送 (17)8.3.5 合同管理 (17)第9章产品测试与认证 (17)9.1 测试方法与工具 (17)9.1.1 测试方法 (17)9.1.2 测试工具 (17)9.2 产品可靠性测试 (18)9.2.1 测试内容 (18)9.2.2 测试要求 (18)9.3 认证与标准 (18)9.3.1 认证 (18)9.3.2 标准 (18)第10章产品发布与市场推广 (19)10.1 产品发布策略 (19)10.1.1 发布时间选择 (19)10.1.3 发布形式与内容 (19)10.2 市场推广渠道 (19)10.2.1 线上推广 (19)10.2.2 线下推广 (19)10.2.3 媒体合作 (19)10.3 售后服务与用户反馈 (19)10.3.1 售后服务体系建设 (19)10.3.2 用户反馈收集与处理 (20)10.3.3 用户满意度调查 (20)第1章产品开发概述1.1 产品开发流程1.1.1 市场调研产品开发的前期工作是对市场进行深入的调研,包括市场需求分析、竞争对手分析、用户需求挖掘等,为产品开发提供明确的方向。

数字逻辑实验指导书(multisim)

实验一集成电路的逻辑功能测试一、实验目的1、掌握Multisim软件的使用方法。

2、掌握集成逻辑门的逻辑功能。

3、掌握集成与非门的测试方法。

二、实验原理TTL集成电路的输入端和输出端均为三极管结构,所以称作三极管、三极管逻辑电路(Transistor -Transistor Logic )简称TTL电路。

54 系列的TTL电路和74 系列的TTL电路具有完全相同的电路结构和电气性能参数。

所不同的是54 系列比74 系列的工作温度范围更宽,电源允许的范围也更大。

74 系列的工作环境温度规定为0—700C,电源电压工作范围为5V±5%V,而54 系列工作环境温度规定为-55—±1250C,电源电压工作范围为5V±10%V。

54H 与74H,54S 与74S 以及54LS 与74LS 系列的区别也仅在于工作环境温度与电源电压工作范围不同,就像54 系列和74 系列的区别那样。

在不同系列的TTL 器件中,只要器件型号的后几位数码一样,则它们的逻辑功能、外形尺寸、引脚排列就完全相同。

TTL 集成电路由于工作速度高、输出幅度较大、种类多、不易损坏而使用较广,特别对我们进行实验论证,选用TTL 电路比较合适。

因此,本实训教材大多采用74LS(或74)系列TTL 集成电路,它的电源电压工作范围为5V±5%V,逻辑高电平为“1”时≥2.4V,低电平为“0”时≤0.4V。

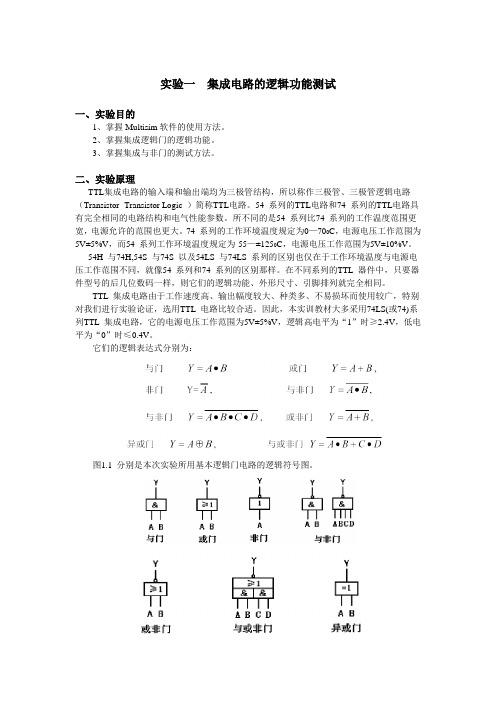

它们的逻辑表达式分别为:图1.1 分别是本次实验所用基本逻辑门电路的逻辑符号图。

图1.1 TTL 基本逻辑门电路与门的逻辑功能为“有0 则0,全1 则1”;或门的逻辑功能为“有1则1,全0 则0”;非门的逻辑功能为输出与输入相反;与非门的逻辑功能为“有0 则1,全1 则0”;或非门的逻辑功能为“有1 则0,全0 则1”;异或门的逻辑功能为“不同则1,相同则0”。

三、实验设备1、硬件:计算机2、软件:Multisim四、实验内容及实验步骤1、基本集成门逻辑电路测试 (1)测试与门逻辑功能74LS08是四个2输入端与门集成电路(见附录1),请按下图搭建电路,再检测与门的逻辑功能,结果填入下表中。

数字逻辑实验指导书(1)

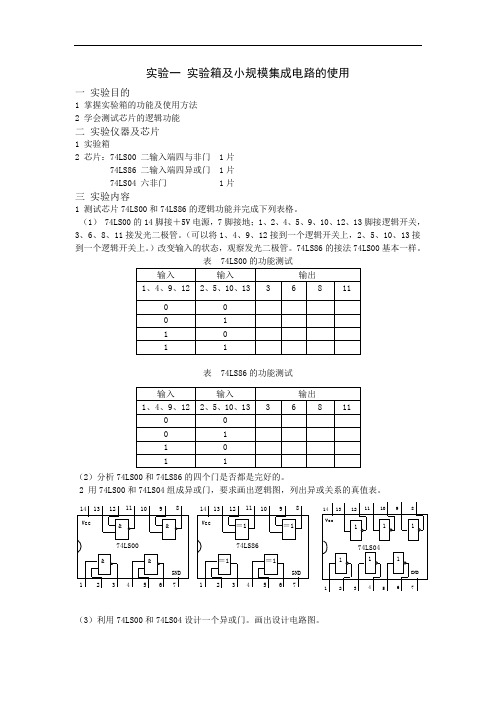

实验一 实验箱及小规模集成电路的使用一 实验目的1 掌握实验箱的功能及使用方法2 学会测试芯片的逻辑功能二 实验仪器及芯片1 实验箱2 芯片:74LS00 二输入端四与非门 1片74LS86 二输入端四异或门 1片 74LS04 六非门 1片三 实验内容1 测试芯片74LS00和74LS86的逻辑功能并完成下列表格。

(1) 74LS00的14脚接+5V 电源,7脚接地;1、2、4、5、9、10、12、13脚接逻辑开关,3、6、8、11接发光二极管。

(可以将1、4、9、12接到一个逻辑开关上,2、5、10、13接到一个逻辑开关上。

)改变输入的状态,观察发光二极管。

74LS86的接法74LS00基本一样。

表 74LS00的功能测试表 74LS86的功能测试(2)分析74LS00和74LS86的四个门是否都是完好的。

2 用74LS00和74LS04组成异或门,要求画出逻辑图,列出异或关系的真值表。

(3)利用74LS00和74LS04设计一个异或门。

画出设计电路图。

实验二译码器和数据选择器一实验目的1继续熟悉实验箱的功能及使用方法2掌握译码器和数据选择器的逻辑功能二实验仪器及芯片1 实验箱2 芯片:74LS138 3线-8线译码器 1片74LS151 八选一数据选择器 1片74LS20 四输入与非门 1片三实验内容1 译码器功能测试(74LS138)芯片管脚图如图所示,按照表连接电路,并完成表格。

其中16脚接+5V,8脚接地,1~6脚都接逻辑开关,7、9、10、11、12、13、14、15接发光二极管。

表2 数据选择器的测试(74LS151)按照表连接电路,并完成表格。

其中16脚接+5V,8脚接地;9、10、11,为地址输入端,接逻辑开关;4、3、2、1、12、13、14、15为8个数据输入端,接逻辑开关;G为选通输入端,Y为输出端,接发光二极管。

表选通端地址输入端 数据输入端 输出 GA 2 A 1 A 0 D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 Y 1 × × × × × × × × × × × 0 0 0 0 0 0 0 1 1 1 1 1 0 0 0 1 1 1 1 0 0 0 0 0 0 0 1 0 1 1 1 1 0 0 0 0 0 0 1 1 1 0 1 0 1 1 1 1 0 1 0 0 0 1 0 1 0 0 0 0 0 1 0 1 1 1 0 0 1 1 0 0 0 1 1 0 1 1 0 0 1 1 1 0 0 11111113 分别用74LS138(配合74LS20)和74LS151实现逻辑函数),,,(7421m m m m F ∑=,要求画出逻辑图。

元器件选型手册(接插件部分)-1

元器件选型手册(接插件部分)浙江正泰仪器仪表有限责任公司目录前言 (2)一、普通单双排插针 (3)二、普通单双排插座 (4)三、其他插针插座 (5)3.1蜈蚣插座 (5)3.2圆孔插座 (5)3.3DIP芯片插座 (6)3.4弯针 (6)四、线对板连接器 (7)4.1单排针座连接器 (7)4.2简牛针座 (9)4.3牛角针座 (9)五、USB接口 (10)六、天线及连接线 (11)七、其他类型接插件 (12)7.1FPC连接器 (12)7.2凤凰端子 (13)7.3PS2插座 (13)7.4DF12系列连接器 (13)7.5RJ45模块化插孔 (14)7.6IC卡座 (14)7.7SIM卡座 (14)前言1.范围本手册对公司目前使用的接插件进行了分类,对接插件的描述进行了定义。

本手册仅用于公司产品设计选型时参考。

2.注意事项本手册中部分物料因在规定的字符条件下无法描述清楚,故采用出图纸的方式,使用时,可以在PLM系统上直接查看或者下载。

本手册中物料描述的尺寸均未标明公差,如实际使用时对尺寸要求很高,请联系厂家出具规格承认书,或者参考GB/T 1804-2000。

所有物料的SAP描述均不能超过40个字符(包括空格)。

一、普通单双排插针1.1SAP描述规范双排单塑插针 2.54mm,2*14P,隔两排抽两排,针长16.5,深圳联颖①名称②脚间距③引脚数④(类型)⑤针尺寸⑥品牌①名称:单排单塑插针、双排单塑插针、单排双塑插针、双排双塑插针;②脚间距:一般为2.54mm或2mm;③引脚数:排数*单排引脚数;④(类型):如抽针,个别针加长等情况的说明,无特殊的可不写;⑤针尺寸:针长表示针两头之间的长度。

若PC=3mm默认不写,此时单塑插针,只需要写出针长;双塑插针,则需要写明针长和PA面长度;a1.2典型示例a PC面为针插入PCB的一端,PA面为远离PCB的一端。

二、普通单双排插座2.1 SAP描述规范双排插座 2.54mm,2*14P,隔两排抽两排,塑高8.5,深圳联颖①名称②脚间距③引脚数④(类型)⑤塑高⑥品牌①名称:双排插座、单排插座;②脚间距:一般为2.54mm或2mm;③引脚数:排数*单排引脚数;④(类型):如抽针等情况的说明,无特殊的可不写;⑤塑高:塑高表示焊接后的插座高度,也就是塑壳高度。

FS-00-C-IEC-60730-认证指导书

IEC 60730-1:2022 Edition 6.0 2022-09Annex H功能安全认证指导书1 / 141.Purpose 目的国际电工委员会(IEC)制定的IEC 60730-1适用于家电或类似自动控制器产品,附录 H 是该标准的功能安全评估部分,将软件分为 Class A、Class B、Class C 三个等级,详细介绍了新的设计、测试和诊断方法,以确保设备的嵌入式控制硬件和软件的运行安全。

德凯中国强大的专家团队可以根据IEC 60730-1、 IEC 60335-1及IEC 61508等安全标准进行技术培训、差距分析、技术支持(包含功能安全概念SIL支持,硬件&软件设计过程支持)及产品功能安全认证(SIL认证)服务。

从家电或类似用途的自动控制器,储能系统的整个生命周期的角度,关注风险识别、软硬件的设计、测试、安装、试运行、维护等。

本文件旨在帮助客户更快地理解IEC 60730-1,2022 Edition 6.0 Annex H功能安全评估所需资料。

2.Scope 范围家用或类似用途的自动控制器3.Class等级说明IEC 60730 标准规定了三种等级:Class A:电器安全不依靠软件,或电器不会造成人员伤害;Class B:防止家电因不安全的操作造成伤害,如洗衣机的电控门锁、电机热关断机制等。

Class C:防止发生特殊的危害,如电子点火燃气灶(有爆炸危险)。

2 / 144.评估流程项目信息搜集不评估否需评估?是准备资料预评否整改符合要求?是正式评估静态分析动态测试现场审核否符合要求?是报告和总结3 / 145.申请材料:表一.材料清单4 / 14附件:申请材料补充说明H.5 Fault Analysis (Risk Analysis)风险分析常用的可编程逻辑器件软件安全性分析方法包括 FMEA、FTA 和 BDA。

这三种方法各有特点,在实际应用中可根据需要,综合应用这三种方法,更加全面、有效地分析可编程逻辑器件软件安全性可编程逻辑器件软件 FMEA 分析方法通过识别可编程逻辑器件软件故障模式,分析造成的后果,研究分析各种故障模式产生的原因,寻找消除和减少其有害后罘的方法,以尽早发现潜在的问题,并采取相应的措施,从而提高可编程逻辑器件软件的安全性。

AAT 器件选型指南.pdf说明书

Part No.

Amplifiers Include

Vcc (V)

Icc

Ptot

(mA) (mW)

Toper Vio Iio (℃) (mV) (nA)

PKG

Replace Brand

LM358 LM393 LM324 LM339

2

16~32 50

500

0~70

2

2

SOP-8/DIP-8

2

2~36 0.4

128*8 256*8 512*8 1028*8 2056*8 5012*8 10024*8

Frequency Icc

Isb

(KHz)

(mA) (µA)

PKG

Replace Brand

Application

400

0.4~3 0.6~18 SOP-8/DIP-8 ATMEL/ISSI/ST/ROHM

400

400

0.4~3 0.6~18 SOP-8/DIP-8 ATMEL/ISSI/ST/ROHM

400

0.4~3 0.6~18 SOP-8/DIP-8 ATMEL/ISSI/ST/ROHM

400

0.4~3 0.6~18 SOP-8/DIP-8 ATMEL/ISSI/ST/ROHM

■ AAT General Line-up

I2-PAK

TO-220AB

TO-220IS

AAT PRODUCTS FOR CUSTOMERS

General Freque

Vcc

Device

ncy

Name

(KHz)

(V)

Vout (V)

Io (A)

7805

---

5~18

可编程逻辑器件实验指导书V1.5

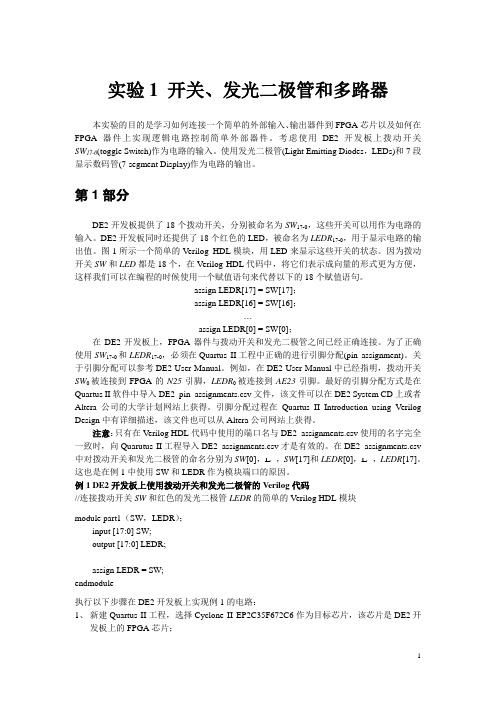

实验1 开关、发光二极管和多路器本实验的目的是学习如何连接一个简单的外部输入、输出器件到FPGA芯片以及如何在FPGA器件上实现逻辑电路控制简单外部器件。

考虑使用DE2开发板上拨动开关SW17-0(toggle Switch)作为电路的输入。

使用发光二极管(Light Emitting Diodes,LEDs)和7段显示数码管(7-segment Display)作为电路的输出。

第1部分DE2开发板提供了18个拨动开关,分别被命名为SW17-0,这些开关可以用作为电路的输入。

DE2开发板同时还提供了18个红色的LED,被命名为LEDR17-0,用于显示电路的输出值。

图1所示一个简单的Verilog HDL模块,用LED来显示这些开关的状态。

因为拨动开关SW和LED都是18个,在Verilog HDL代码中,将它们表示成向量的形式更为方便,这样我们可以在编程的时候使用一个赋值语句来代替以下的18个赋值语句。

assign LEDR[17] = SW[17];assign LEDR[16] = SW[16];…assign LEDR[0] = SW[0];在DE2开发板上,FPGA器件与拨动开关和发光二极管之间已经正确连接。

为了正确使用SW17-0和LEDR17-0,必须在Quartus II工程中正确的进行引脚分配(pin assignment)。

关于引脚分配可以参考DE2 User Manual。

例如,在DE2 User Manual中已经指明,拨动开关SW0被连接到FPGA的N25引脚,LEDR0被连接到AE23引脚。

最好的引脚分配方式是在Quartus II软件中导入DE2_pin_assignments.csv文件,该文件可以在DE2 System CD上或者Altera公司的大学计划网站上获得。

引脚分配过程在Quartus II Introduction using Verilog Design中有详细描述,该文件也可以从Altera公司网站上获得。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

缓冲驱动器:带反向的缓冲驱动器74X240、不带反向的缓冲驱动器74X244。

收发器:寄存器收发器74X245、通用收发器74X245、总线收发器等。

总线开关:包括总线交换和通用总线器件等。

逻辑器件按制造工艺分类

Bipolar工艺的器件:TTL、S、LS、AS、F、ALS、ECL。

应用技术

逻辑器件基本介绍

标准逻辑门器件包括:

2个及3个输入门

施密特触发器输入门

三态输出缓冲器

漏极开路输出

断电高阻抗(Power off Hi-Z)

缓冲器解码器及多路复用器

闭锁器及触发器

双电源轨转换器

门转换(Gate translations)

标准逻辑门器件优势:

Ioff支持热插拔

当VCC处于0 V时,Ioff可在输入或输出端上提供电压

CB3T(低电压转换总线开关)

•工作电压范围:2.3V to 3.6V VCC

•0.25ns典型tpd

LVC(低电压CMOS)

•工作电压范围:1.65V to 5.5V VCC

•3.0ns典型tpd

AUC(先进的超低电压CMOS)

•工作电压范围:0.8V to 2.7V VCC

•2.0ns典型tpd

部分断电带电插拔

主要特点:

可防止在上电或断电期间发生意外的器件动作;

可防止信号通过寄生二极管供应电流;

允许对系统内的部分电路实施断电;

部分断电工作需要Ioff规格。

支持部分断电(Ioff)的器件系列:

ABT、ALVT、AVC、AUC、AUP、CBTLV、CBT-C、GTL、GTLP、LV-A、LVC、LVT、VME

1.8-V逻辑器件:ALVC、AUC、AUP、AVC、LVC、LV1T

2.5-V逻辑器件:ALVC、ALVT、AUC、AUP、AVC、CBTLV、LV、LV1T、LV-A、LVC

3.3-V逻辑器件:AC、AHC、ALB、ALVC、ALVT、AUP、AVC、CBLTV、LV、LV-A、LVC、LVT、LV1T、AUP1T

CMOS工艺的器件:HC、HCT、CD4000、ACL、FCT、LVC、LV、CBT、ALVC、AHC、AHCT、CBTLV、AVC、GTLP。

BiCMOS工艺的器件:BCT、ABT、LVT、ALVT

逻辑器件按电平种类分类

0.8-V逻辑器件:AUC、AUP

1.2-V逻辑器件:AUC、AUP、AVC

1.5-V逻辑器件:AUC、AUP、AVC

在有效逻辑电平条件下,保持电流并未给驱动输出施加很重的负载;

免除了在未用或悬空输入/输出引脚上增设外部电阻的需要;

器件名称中的“H”表示总线保持;

系统功耗的增加微乎其微;

总线保持输入单元取代了上拉电阻。

图1总线保持示意图

具有总线保持选项的器件系列:

ABT、ALVC、ALVT、AVC、AUC、FCT、GTL、GTLP、LVC、LVT、VME

图1逻辑器件开关标准比较

逻辑器件性能比较

门电路

AHC(低功耗)

•工作电压范围:2.0 V至5.5 V

•驱动电流:4mA(在3.3 V电压下)、8mA(在5 V电压下)

•速度:典型值为150MHz(在5V电压下)

LVC(高驱动能力)

•工作电压范围:1.65 V至5.5V

•驱动电流:24mA(在3.3V电压下)、32mA(在5.0V电压下)

图2部分断电带电插拔示意图

热插拔,带电插拔,二级

主要特点:

可防止在VCC跳变点之前出现不需要的输出开通;

可防止总线在上电时承受重负载;

允许进行热插拔工作;

热插拔需要Ioff和PU3S规格。

支持热插拔(Ioff和上电三态)的器件系列:

ABT、ALVT、GTLP、LVCZ、LVT、VME

带电插拔,三级

主要特点:

√

√

√

√

√

√

√

√

LS

5

√

√

√

√

√

√

√

√

√

√

√

√

LV-AT

5

√

√

√

√

√

√

√

√

S

5

√

√

√

√

√

√

√

√

√

√

√

√

TTL

5

√

√

√

√

√

√

√

√

√

CD4000

5,10,12to18

√

√

√

√

√

√

√

√

√

√

√

√

√

√

√

逻辑器件使用说明

我司常用逻辑器件罗列如下:

400423001406

施密特触发器*MM74HC14M*M14A*2-6V*扇出1:10

4)在总线达到产生传输线效应的长度后,应考虑对传输线进行匹配,一般采用的方式有始端匹配、终端匹配等。

始端匹配是在芯片的输出端串接电阻,目的是防止信号畸变和地弹反射,特别当总线要透过接插件时,尤其须做始端匹配。内部带串联阻尼电阻的器件相当于始端匹配,由于其阻值固定,无法根据实际情况进行调整,在多数场合对于改善信号质量收效不大,故此不建议推荐使用。始端匹配推荐电阻值为10~51Ω,在实际使用中可根据IBIS模型模拟仿真确定其具体值。由于终端匹配网络加重了总线负载,所以不应该因为匹配而使Buffer的实际驱动电流大于驱动器件所能提供的最大Source、Sink电流值。应选择正确的终端匹配网络,使总线即使在没有任何驱动源时,其线电压仍能保持在稳定的高电平。

输入端上的过压耐受能力可实现降压转换(down translation)

漏极开路输出可实现升压或降压转换

AUP1Txxx器件支持升压转换(uptranslation)

施密特触发器输入允许任意的上升及下降时间斜率

逻辑器件技术介绍

总线保持输入

主要特点:

保持输入的最后已知状态——避免使输入悬空;

I(HOLD)或IBHL和IBHH确定了最小保持电流;

A

在用

Fairchild

A

在用

选型原则

1)多余不用输入管脚的处理。

在多数情况下,集成电路芯片的管脚不会全部被使用。例如74ABT16244系列器件最多可以使用16路I/O管脚,但实际上通常不会全部使用,这样就会存在悬空端子。所有数字逻辑器件的无用端子必须连接到一个高电平或低电平,以防止电流漂移(具有总线保持功能的器件无需处理不用输入管脚)。究竟上拉还是下拉由实际器件在何种方式下功耗最低确定。244、16244经测试在接高电平时静态功耗较小,而接地时静态功耗较大,故建议其无用端子处理以通过电阻接电源为好,电阻值推荐为1~10K。

选择器:2-1、4-1、8-1选择器74X157、74X153、74X151等。

编/译码器:2/4、3/8和4/16译码器74X139、74X138、74X154等。

计数器:同步计数器74X161、异步计数器74X393等。

寄存器:串-并移位寄存器74X164、并-串寄存器74X165等。

触发器:J-K触发器、带三态的D触发器74X374、不带三态的D触发器74X74、施密特触发器等。

2)选择板内驱动器件的驱动能力,速度,不能盲目追求大驱动能力和高速的器件,应该选择能够满足设计要求,同时有一定的余量的器件,这样可以减少信号过冲,改善信号质量。并且在设计时必须考虑信号匹配。

3)在对驱动能力和速度要求较高的场合,如高速总线型信号线,可使用ABT、LVT系列。

板间接口选择ABT16244/245或LVTH16244/245,并在母板两端匹配,在不影响速度的条件下与母板接口尽量串阻,以抑制过冲、保护器件,典型电阻值为10-200Ω左右,另外,也可以使用并接二级管来进行处理,效果也不错,如1N4148等(抗冲击较好)。

√

√

√

LV1T

1.8,3.3,5

√

√

√

√

√

√

LVC

1.8,3.3,5

√

√

√

√

√

√

√

√

√

√

√

√

√

√

√

√

√

√

TS

1.8,3.3,5

√

√

√

√

√

TVC

1.8,3.3,5

√

√

√

√

√

√

AC

3.3,5

√

√

√

√

√

√

√

√

√

√

√

√

AHC

3.3,5

√

√

√

√

√

√

√

√

√

√

√

√

√

HC

3.3,5

√

√

√

√

√

√

√

√

√

√

√

√

√

√

LV-A

12)在器件工作过程中,为保证器件安全运行,器件引脚上的电压及电流应严格控制在器件手册指定的范围内。逻辑器件的工作电压不要超出它所允许的范围。

13)逻辑器件的输入信号不要超过它所能允许的电压输入范围,不然可能会导致芯片性能下降甚至损坏逻辑器件。

14)对开关量输入应串电阻,以避免过压损坏。

15)对于带有缓冲器的器件不要用于线性电路,如放大器、TTL、CMOS器件的互连

断电输出停用

上电复位

双极型

CMOS

BiCMOS

AUC

0.8,1.8,2.5

√