8.1 加减运算电路

加减法运算电路设计

电子课程设——加减法运算电路设计¥学院:电信息工程学院;专业:电气工程及其自动化班级:姓名:学号:指导老师:闫晓梅2014年12月 19日加减法运算电路设计一、设计任务与要求#1.设计一个4位并行加减法运算电路,输入数为一位十进制数,2.作减法运算时被减数要大于或等于减数。

灯组成的七段式数码管显示置入的待运算的两个数,按键控制运算模式,运算完毕,所得结果亦用数码管显示。

4.系统所用5V电源自行设计。

二、总体框图1.电路原理方框图:%图2-1二进制加减运算原理框图2.分析:如图1-1所示,第一步置入两个四位二进制数(要求置入的数小于1010),如(1001)2和(0111)2,同时在两个七段译码显示器上显示出对应的十进制数9和7;第二步通过开关选择运算方式加或者减;第三步,若选择加运算方式,所置数送入加法运算电路进行运算,同理若选择减运算方式,则所置数送入减法运算电路运算;第四步,前面所得结果通过另外两个七段译码器显示。

例如:若选择加法运算方式,则(1001)2+(0111)2=(10000)2十进制9+7=16,并在七段译码显示器上显示16;若选择减法运算方式,则(1001)2-(0111)2=(00010)2十进制9-7=2,并在七段译码显示器上显示02。

三、选择器件~1.器件种类:}^表3-12.重要器件简介:(1)[(2). 4位二进制超前进位加法器74LS283:完成加法运算使用该器件。

1).74LS283 基本特性:供电电压:输出高电平电流:输出低电平电流: 8mA。

2).引脚图:图3-1引出端符号:A1–A4 运算输入端B1–B4 运算输入端《C0 进位输入端∑1–∑4 和输出端C4 进位输出端3).逻辑符号:图3-2 4).内部原理图:-图3-3 5).功能表:表3-2(3)异或门:74LS861).引脚图: 2).逻辑符号:、图3-4 图3-53). 逻辑图:图3-6·4).真值表:表3-3分析:异或:当AB不相同时, 结果才会发生。

加减运算电路

加减运算电路

加减运算电路是指将两个数相加或相减的运算电路,是一种具有数字逻辑处理能力的电路。

它由若干个基本元件及其组合而成,可以实现对二进制数据的加减运算。

加法电路可以分为两类:全加器和半加器。

全加器可以实现任意位数的加法运算,它由若干个半加器组成,每个半加器由两个异或门、一个与门和一个或门组成。

减法电路可以由补码的形式实现。

在实现减法运算时,可以使用全加器和半加器,也可以使用两个全加器和一个反相器来实现。

加减运算电路

加减运算电路加减运算电路:一、介绍1. 加减运算电路是可以进行加减运算操作的电路系统。

它是数字电路系统中最重要的组成部分之一,主要用于完成数字计算机等数字电路系统的运算操作。

2. 加减运算电路包括整数加法、减法、移位运算、位计数等多种操作,简称“四运算”。

整数加法是指在数字电路中,把两个二进制数相加,得到其和;减法是指在数字电路中,把两个二进制数相减,得到其差;移位运算是指在数字电路中,把中间输出的数值改变位置,以满足特定要求;位计数是指在数字电路中,把二进制数中1的个数进行统计和记录。

二、结构1. 加减运算电路通常主要由两部分组成:数据输入部分和运算控制部分。

数据输入部分由数据缓冲器,数据移位器等组成,主要用于收集被加减数据,并把它们传输到运算控制部分。

运算控制部分由加减器,运算控制电路以及计数器等组成,主要负责运算控制,跟踪不同的运算状态。

2. 加减运算电路结构不同,元件的组成也有所不同。

比如,可以使用半加器来完成整数加法,使用XOR门完成减法,使用带移位器完成移位运算,使用计数器电路完成位计数。

三、性能1. 加减运算电路具有高计算精度、高效率和高稳定性等优点,是现代计算机数字处理的核心技术。

2. 加减运算电路的高计算精度和高效率使它能够实现复杂的运算,而在稳定性方面,该电路可以长期稳定工作,即使在高温条件下仍能保持精度不变。

3. 此外,加减运算电路还具有抗干扰性能良好、受控制快速,可实现快速动态操作等优点。

四、应用1. 由于加减运算电路有着高计算精度、高效率和高稳定性等特性,它被广泛应用于航空、航天、汽车、机器人、医学、工业自动化等多个领域,是计算机系统的主要组成部分。

2. 加减运算电路还用于智能家居、大型安全系统、智能医疗仪器等诸多应用场景,可以实现智能化控制、数据采集、安全保障等功能。

3. 此外,加减运算电路还会出现在微处理器、控制器、数据处理机等设备中,用于实现数据处理、计算机管理和指令决策等功能。

加减法运算器电路

加法器半加法器•输入:2 个 1 位二进制数字 A 和 B•输出:和 S 和进位 C全加法器•输入:2 个 1 位二进制数字 A 和 B,以及一个进位 C•输出:和 S 和进位 C加法器电路一个 n 位加法器可以由多个半加法器或全加法器级联而成。

例如,一个 4 位加法器可以由 4 个全加法器组成。

减法器半减法器•输入:2 个 1 位二进制数字 A 和 B•输出:差 D 和借位 B全减法器•输入:2 个 1 位二进制数字 A 和 B,以及一个借位 B•输出:差 D 和借位 B减法器电路一个 n 位减法器可以由多个半减法器或全减法器级联而成。

减法器通常使用补码来实现。

补码•正数的补码与本身相同。

•负数的补码是其绝对值的 1 的补码,即按位取反并加 1。

减法使用补码•将要减去的数求补码。

•将减数和补码相加。

•如果最高位为 0,则结果为正数。

•如果最高位为 1,则结果为负数,并舍弃最高位。

加减法运算器电路一个加减法运算器电路可以将两个 n 位二进制数字相加或相减。

它通常由以下组成:•一个 n 位加法器•一个 n 位减法器•一个选择器,用于根据控制信号选择加法或减法操作设计步骤1.确定位数:确定输入和输出的位数。

2.选择加法器和减法器:选择合适的加法器和减法器电路。

3.设计选择器:设计一个选择器,用于根据控制信号选择加法或减法操作。

4.连接电路:将加法器、减法器和选择器连接起来。

5.测试电路:使用各种输入对测试电路的正确性。

运算放大器

输入正弦波

(vi:正弦波,频率500Hz,幅度1V)

思考: 输入信号 频率对输 出信号幅 度的影响?

§8.4 对数和指数运算电路

8.4.1 对数电路

→

vI

+ vD _ D A

vI iD iI R

→

R

iI

iD

→

id

+

vD vO

vO

iD Is (e 1)

Is e

vD VT

vD VT

平衡电阻 R3= R1// R2// Rf1= 12.5K

R6= R4// R5// Rf2= 8.3K

例2: 如图电路,求Avf,Ri 解: V = - R3 V o i

R2

R3 Avf R2

Vo2

2R2

Vo 2

2 R2 =Vo = 2Vi R3

A2

R3

Vi R1R 2 Ri Ii R1 R 2

R'

vO VT

Is e

vD VT 时

vI R

vI vO VT ln RIs

对数电路改进

基本对数电路缺点:

运算精度受温度影响大

小信号时exp(vD/vT)与1差不多大,所以误差很大 二极管在电流较大时伏安特性与PN结伏安特性差别较大, 所以运算只在较小的电流范围内误差较小。

v3

R3

R4

由于第一级差放 电路上下对称,R1的 中点可视为接地点, 所以:

R1

vs2

A2

+

vo2

R3

v4

R4

+

-

+

-

A3

vo

R2 vo1 = (1 + )vs1 R1/2 R2 vo2 = (1 + )vs 2 R1/2

减法运算电路

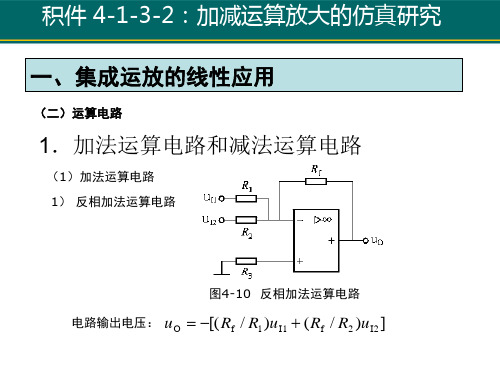

积件 4-1-3-2:加减运算放大的仿真研究

2) 同相加法运算电路

图4-11 同相加法运算电路

积件 4-1-3-2:加减运算放大的仿真研究

(2)减法运算电路

图 412 减 法 运 算 电 路

积件 4-1-3-2:加减运算放大的仿真研究

二、其它方面的应用

1.电压比较器 (1)基本电路

图4-13 电压比较器

积件 4-1-3-2:加减运算放大的仿真研究

作业: 1、画出集成运放电路组成的加法器、 减法器电路图。并证明输入电压与输出 电压的关系式。 2、画出输出电压Uo与输入电压Ui符合 下列关系的运放电路图;(1) Uo/Ui=-1;(2)Uo/Ui=15;(3) Uo/(Ui1+Ui2+Ui3)=-20。

加减运算放大的仿真研究一集成运放的线性应用二运算电路1加法运算电路反相加法运算电路图410反相加法运算电路电路输出电压

积件 4-1-3-2:加减运算放大的仿真研究

一、集成运放的线性应用

(二)运算电路

1.加法运算电路和减法运算电路

(1)加法运算电路 1) 反相加法运算电路

图4-10 反相加法运算电路

电路输出电压: uO [( Rf / R1 )uI1 (Rf / R2 )uI2 ]

积件 4-1-3-2:加减运算放大的仿真研究

可见,输出电压与输入电压反相,且uo是两输入信号加权后的负值相加,故称反相

加法器。

若取, R1 R2 则

uO (Rf / R1 )(uI1 uI2 )

若取,Rf R1 R2 则, uO (uI1 uI2 )

电路成为反相加法器。

积件 4-1-3-2:加减运算放大的仿真研究

第8章( 8.1-8.3) 相量及相量分析法

例

i(t)

+ u(t) -

R

已知: u( t ) U m sin(wt y u ) 解: L

求:稳态解 i(t)

1. 经典法: 一阶常系数 di(t ) Ri (t ) L U m sin(wt y u ) 线性微分方程 dt 自由分量(齐次方程通解): A e-(R/L) t

全解:

第8章 相量及相量分析法 8.1-8.3 重点:

复数及其运算 相位差

相量和相量图 正弦量的相量表示

电路元件VCR 的相量形式

电路定律的相量形式

8 .1 .1 正弦量的基本概念 正弦交流电路

如果在电路中电动势的大小与方向均随时间按 正弦规律变化,由此产生的电流、电压大小和方向 也是正弦的,这样的电路称为正弦交流电路。

u (t ) 2U cos(wt y ) U Uy

例1. 已知

解: I 10030o A

o

i 141.4 cos(314t 30 ) A u 311.1cos(3 14t 60o )V

试用相量表示 i, u 。

U 220 60o V

14

例2. 已知 I 5015o A, f 50Hz . 试写出电流的瞬时值表达式。

y

Re

a

Re

A a jb

A A e jy | A | y

11

2. 复数运算

(1)加减运算——直角坐标

(2) 乘除运算——极坐标 3. 旋转因子

A1±A2=(a1±a2)+j(b1±b2)

A1 A2 A1 A2 y 1 y 2

复数 e jy = cos y + jsin y = 1∠y A e jy A逆时针旋转一个角度y ,模不变

运算放大器详细的应用电路(很详细)

积分电路的其它用途:

去除高频干扰

将方波变为三角波

移相

在模数转换中将电压量变为时间量

§8.3?积分电路和微分电路

8.3.2?微分电路

微分实验电路

把三角波变为方波

(Vi:三角波,频率 1KHz,幅度 0.2V)

输入正弦波

(Vi:正弦波,频率 1KHz,幅度 0.2V)

思考:输入信号与输出信号间的相位关系?

根据与 R1?、Rf?的关系,集成运放两输入端外接电阻的对称条件。

计算出:R=3979Ω?取 R=3.9KΩ 2.根据Q值求和,因为时,根据与、的关系,集成运放两输入端外接电阻的对称条件

例题 1 仿真结果 例题与习题 2 LPF 例题与习题 2 仿真结果 例题与习题 3 HPF 例题与习题 3 仿真结果 例题与习题 4 例题与习题 4 仿真结果 vo1:红色 vo?:蓝色

、

e.?全通滤波器(APF)?

4.?按频率特性在截止频率 fp 附近形状的不同可分为 Butterworth,?Chebyshev?和?Bessel 等。 理想有源滤波器的频响: 滤波器的用途 滤波器主要用来滤除信号中无用的频率成分,例如,有一个较低频率的信号,其中包含一些较高频率成分的

干扰。滤波过程如图所示。 §8.6?有源滤波电路 8.6.2?低通滤波电路?(LPF) 低通滤波器的主要技术指标

组成:简单 RC 滤波器同相放大器特点:│Avp?│>0,带负载能力强缺点:阻带衰减太慢,选择性较差。 二.?性能分析

有源滤波电路的分析方法: 1.电路图→电路的传递函数 Av(s)→频率特性 Av(jω) 2.?根据定义求出主要参数 3.?画出电路的幅频特性 一阶 LPF 的幅频特性: 8.6.2.2?简单二阶?LPF

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1

Index

8.1 加减运算电路 8.2 积分器和微分器 8.3 电压比较器 8.4 转换器

模拟电路基础

2

8.1 加减运算电路

8.1.1 求和运算电路 一、反相求和运算

“虚短(虚地)”和“虚开”

节点N的电流方程

uI1 uI2 uI3 uO

R1 R2 R3

Rf

uO

Rf

8

8.1 加减运算电路

8.1.1 求和运算电路

【例8-1-2】试通过只含一个集成运放的电路,实现 uO uI1 uI2 uI3

的函数关系,其中Rf取1kΩ。

uI1 R1 1k

uI2 R2 1k

uI3 R3 1k

+

A

uO

R 500

Rf 1k

uI1 R1 1k uI2 R2 1k uI3 R3 1k

电平Vref,试分析输出与输入之间的关系。

@

R

仿真8-1-1

例8-1-1的

仿真

+

A

uO

16R

8R

D0

4R D1

2R D2

D3

uO

uO3

uO2

uO1

uO0

1 2

D3

1 4

D2

1 8

D1

1 16

D0

Vref

输入

Vref 24

23 D3 22 D2 21 D1 20 D0

当RP=RN时 即R1//R2//R=R3//R4//Rf时

uO2

Rf

uI1 R1

uI2 R2

模拟电路基础

10

8.1 加减运算电路

8.1.2 加减运算电路 二、差分放大电路

uO

Rf R

(uI2

uI1)

模拟电路基础

11

8.1 加减运算电路

8.1.2 加减运算电路 二、差分放大电路 ——改进:提升输入电阻

uI2 R1

uI3单独作用:

uO3

Rf

uI3 R1

共同作用: uO

uO1

uO2

uO3

Rf

uI1 R1

uI2 R2

uI3 R3

模拟电路基础

4

8.1 加减运算电路

【 例 8-1-1】4 位 权 电 阻 网 络 数 模 转 换 ( DAC , digital to

analog converter)电路。其中D3~D0为输入的控制信号,只 有两种状态0和1,为“0”时即低电平0V,为“1”时即高

uO

Rf R

uO1 uO2

Rf R

uI1 uI2

模拟电路基础

12

8.1 加减运算电路

8.1.2 加减运算电路

仪表放大器

二、差分放大电路 ——改进:增益可调

@

仿真8-1-3 仪表放大电 路的仿真

uO1

uO2

2R1 R2

R2

ui1 ui2

uO

Rf R

uO1

R 1k

+ A

Rf 1k R4 1k

@

仿真8-1-2 例8-1-2的

仿真

uO

模拟电路基础

9

8.1 加减运算电路

8.1.2 加减运算电路 一、基本加减运算电路

uO1

Rf

uI3 R3

uI4 R4

uO

uO1

uO2

Rf

uI1 R1

uI2 R2

uI3 R3

uI4 R4

节点N的电流方程

ห้องสมุดไป่ตู้uN

R R Rf

uO

模拟电路基础

6

8.1 加减运算电路

8.1.1 求和运算电路 二、同相求和运算

uI1 R1

uI2 R2

uI3 R3

1 R1

1 R2

1 R3

1 R4

R

R Rf

uO

令RP为集成运放同相输入端外接等效电阻

RP R1 // R2 // R3 // R4

uI1 R1

uI2 R2

uI3 R3

模拟电路基础

3

8.1 加减运算电路

8.1.1 求和运算电路 一、反相求和运算

注意:求和运算中的“叠加定理”

uO

Rf

uI1 R1

uI2 R2

uI3 R3

uI1单独作用:

uO1

Rf

uI1 R1

uI2单独作用:

uO2

Rf

uO

Rf

RP RN

uI1 R1

uI2 R2

uI3 R3

注意1:求和运算中的“叠加定理”

uI1单独作用:

uO1

1

Rf R

R1

R2 // R2

R3 // // R3

R4 // R4

uI1

Rf R1

RP RN

uI1

注意2:R4的意义

模拟电路基础

模拟电路基础

5

8.1 加减运算电路

8.1.1 求和运算电路 二、同相求和运算

“虚短”和“虚开”

节点P的电流方程 uI1 uP uI2 uP uI3 uP uP

R1

R2

R3

R4

uI1 R1

uI2 R2

uI3 R3

1 R1

1 R2

1 R3

1 R4

uP

uO2

uO

Rf R

1

2R1 R2

uI1

uI2

模拟电路基础

13

8.1 加减运算电路

8.1.2 加减运算电路 二、差分放大电路

模拟电路基础

14

令RN为集成运放反相输入端外接等效电阻

RN

R Rf R Rf

R // Rf

模拟电路基础

uO

Rf

RP RN

uI1 R1

uI2 R2

uI3 R3

RP=RN时

uO

Rf

uI1 R1

uI2 R2

uI3 R3

7

8.1 加减运算电路

8.1.1 求和运算电路 二、同相求和运算