微电子工艺习题总结

微电子工艺技术-复习要点答案(完整版)

微电⼦⼯艺技术-复习要点答案(完整版)第四章晶圆制造1.CZ法提单晶的⼯艺流程。

说明CZ法和FZ法。

⽐较单晶硅锭CZ、MCZ和FZ三种⽣长⽅法的优缺点。

答:1、溶硅2、引晶3、收颈4、放肩5、等径⽣长6、收晶。

CZ法:使⽤射频或电阻加热线圈,置于慢速转动的⽯英坩埚内的⾼纯度电⼦级硅在1415度融化(需要注意的是熔硅的时间不宜过长)。

将⼀个慢速转动的夹具的单晶硅籽晶棒逐渐降低到熔融的硅中,籽晶表⾯得就浸在熔融的硅中并开始融化,籽晶的温度略低于硅的熔点。

当系统稳定后,将籽晶缓慢拉出,同时熔融的硅也被拉出。

使其沿着籽晶晶体的⽅向凝固。

籽晶晶体的旋转和熔化可以改善整个硅锭掺杂物的均匀性。

FZ法:即悬浮区融法。

将⼀条长度50-100cm 的多晶硅棒垂直放在⾼温炉反应室。

加热将多晶硅棒的低端熔化,然后把籽晶溶⼊已经熔化的区域。

熔体将通过熔融硅的表⾯张⼒悬浮在籽晶和多晶硅棒之间,然后加热线圈缓慢升⾼温度将熔融硅的上⽅部分多晶硅棒开始熔化。

此时靠近籽晶晶体⼀端的熔融的硅开始凝固,形成与籽晶相同的晶体结构。

当加热线圈扫描整个多晶硅棒后,便将整个多晶硅棒转变成单晶硅棒。

CZ法优点:①所⽣长的单晶的直径较⼤,成本相对较低;②通过热场调整及晶转,坩埚等⼯艺参数的优化,可以较好的控制电阻率径向均匀性。

缺点:⽯英坩埚内壁被熔融的硅侵蚀及⽯墨保温加热元件的影响,易引⼊氧、碳杂质,不易⽣长⾼电阻率单晶。

FZ法优点:①可重复⽣长,提纯单晶,单晶纯度较CZ法⾼。

②⽆需坩埚、⽯墨托,污染少③⾼纯度、⾼电阻率、低氧、低碳④悬浮区熔法主要⽤于制造分离式功率元器件所需要的晶圆。

缺点:直径不如CZ法,熔体与晶体界⾯复杂,很难得到⽆位错晶体,需要⾼纯度多晶硅棒作为原料,成本⾼。

MCZ:改进直拉法优点:较少温度波动,减轻溶硅与坩埚作⽤,降低了缺陷密度,氧含量,提⾼了电阻分布的均匀性2.晶圆的制造步骤【填空】答:1、整形处理:去掉两端,检查电阻确定单晶硅达到合适的掺杂均匀度。

微电子工艺习题答案(整理供参考)

第一章1.集成电路:通过一系列特定的加工工艺,将晶体管、二极管等有源器件和电阻、电容等无源器件,按照一定的电路互连,“集成”在一块半导体单晶片(如Si、GaAs)上,封装在一个外壳内,执行特定电路或系统功能。

集成电路发展的五个时代及晶体管数目:小规模集成电路(小于100个)、中规模集成电路(100~999)、大规模集成电路(1000~99999)、超大规模集成电路(超过10万)、甚大规模集成电路(1000万左右)。

2、硅片制备(Wafer preparation)、硅片制造(Wafer fabrication)硅片测试/拣选(Wafer test/sort)、装配与封装(Assembly and packaging)、终测(Final test)。

3、半导体发展方向:提高性能、提高可靠性、降低价格。

摩尔定律:硅集成电路按照4年为一代,每代的芯片集成度要翻两番、工艺线宽约缩小30%,IC工作速度提高1.5倍等发展规律发展。

4、特征尺寸也叫关键尺寸,集成电路中半导体器件能够加工的最小尺寸。

5、more moore定律:芯片特征尺寸的不断缩小。

从几何学角度指的是为了提高密度、性能和可靠性在晶圆水平和垂直方向上的特征尺寸的继续缩小,more than moore定律:指的是用各种方法给最终用户提供附加价值,不一定要缩小特征尺寸,如从系统组件级向3D集成或精确的封装级(SiP)或芯片级(SoC)转移。

6、High-K:高介电系数;low-K:低介电系数;Fabless:无晶圆厂;Fablite:轻晶片厂;IDM:Integrated Device Manufactory集成器件制造商;Foundry:专业代工厂;Chipless:无晶片1、原因:更大直径硅片,更多的芯片,单个芯片成本减少;更大直径硅片,硅片边缘芯片减小,成品率提高;提高设备的重复利用率。

硅片尺寸变化:2寸(50mm)-4寸(100mm)-5寸(125mm)-6寸(150mm)-8寸(200mm)-12寸(300mm)-18寸(450mm).2、物理尺寸、平整度、微粗糙度、氧含量、晶体缺陷、颗粒、体电阻率。

微电子工艺习题参考解答

CRYSTAL GROWTH AND EXPITAXY1.画出一50cm 长的单晶硅锭距离籽晶10cm 、20cm 、30cm 、40cm 、45cm 时砷的搀杂散布。

(单晶硅锭从融体中拉出时,初始的搀杂浓度为1017cm -3)2.硅的晶格常数为Å.假设为一硬球模型: (a)计算硅原子的半径。

(b)肯定硅原子的浓度为多少(单位为cm -3)? (c)利用阿伏伽德罗(Avogadro)常数求出硅的密度。

3.假设有一l0kg 的纯硅融体,当硼搀杂的单晶硅锭生长到一半时,希望取得 Ω·cm 的电阻率,则需要加总量是多少的硼去搀杂?4.一直径200mm 、厚1mm 的硅晶片,含有的硼均匀散布在替代位置上,求:(a)硼的浓度为多少? (b)硼原子间的平均距离。

5.用于柴可拉斯基法的籽晶,通常先拉成一小直径的狭小颈以作为无位错生长的开始。

若是硅的临界屈服强度为2×106g/cm2,试计算此籽晶能够支撑的200mm 直径单晶硅锭的最大长度。

6.在利用柴可拉斯基法所生长的晶体中掺入硼原子,为安在尾端的硼原子浓度会比籽晶端的浓度高?7.为何晶片中心的杂质浓度会比晶片周围的大? 8.对柴可拉斯基技术,在k 0=时,画出C s /C 0值的曲线。

9.利用悬浮区熔工艺来提纯一含有镓且浓度为5×1016cm -3的单晶硅锭。

一次悬浮区熔通过,熔融带长度为2cm ,则在离多远处镓的浓度会低于5×1015cm -3?10.从式L kx s e k C C /0)1(1/---=,假设k e =,求在x/L=1和2时,C s /C 0的值。

11.若是用如右图所示的硅材料制造p+-n突变结二极管,试求用传统的方式搀杂和用中子辐照硅的击穿电压改变的百分比。

12.由图,若C m=20%,在T b时,还剩下多少比例的液体?13.用图解释为何砷化镓液体总会变成含镓比较多?14.间隙n s的平衡浓度为Nexp[-E s/(kT)],N为半导体原子的浓度,而E s为形成能量。

微电子工艺_哈尔滨工业大学中国大学mooc课后章节答案期末考试题库2023年

微电子工艺_哈尔滨工业大学中国大学mooc课后章节答案期末考试题库2023年1.CZ法拉不出高阻单晶硅锭的主要原因是:答案:坩埚材料分解出的氧会进入硅锭;2.实际VPE工艺温度多在质量传递控制区,此时外延速率:答案:对温度不太敏感;3.关于硅的热氧化,下面哪种说法正确:答案:氧化反应是在Si/SiO2界面发生的;4.在D-G模型中假定稳定生长氧化层时,氧化剂的气相输运、固相扩散和化学反应三个流密度应:答案:相等;5.基于LSS理论,离子注入受到靶原子核与电子的阻止:答案:核阻止和电子阻止是独立的;6.多晶硅薄膜通常采取哪种方法制备:答案:LPCVD7.PVD与CVD比较,下列那种说法正确:答案:PVD薄膜与衬底的粘附性较差;8.外延用衬底硅片一般偏离准确晶向一个小角度,如(111)-Si偏离3º,下列那种说法正确?答案:这是为了得到原子层量级的台阶;这是为外延生长提供更多的结点位置;9.硅恒定源扩散,在扩散温度硅的固溶度为N s,在进行了40min扩散后,测得结深是1.5μm,若要获得2.0μm的结深,在原工艺基础上应再扩散多少分钟?硅表面杂质浓度是多少?答案:应再扩散31 min杂质表面浓度=N s表面杂质浓度等于该工艺温度时硅的固溶度;10.P在两歩扩散工艺中,第二步再分布的同时又进行了热氧化(kp=10),这会给再分布扩散带来哪些影响:答案:P扩散速度加快;在SiO2/Si界面Si一侧的P堆积(是指高于SiO2一侧);扩入Si的P总量下降;11.扩散系数是表征扩散快慢的参数,它相当于单位浓度梯度时的扩散通量,所以它:答案:单位为m∧2/s有单位;12.看图判断,下列哪种描述正确:答案:图(b)是注入的高能离子。

图(a)是注入的低能离子;13.下列哪个工艺方法应用了等离子体技术:答案:溅射RIEHDPCVD14.蒸镀工艺要求蒸镀室为高真空度的原因:答案:为了避免蒸发分子(或原子)被氧化;为了提高蒸发分子(或原子)的平均自由程;为了降低镀膜中的杂质;15.可以采取哪种方法来提高光刻分辨率?答案:减小分辨率系数;增大光学系统数值孔径;缩短光源波长;16.CZ法、MCZ法拉单晶时必须有籽晶;而FZ法拉单晶时不需要籽晶。

微电子技术基础知识单选题100道及答案解析

微电子技术基础知识单选题100道及答案解析1. 微电子技术的核心是()A. 集成电路B. 晶体管C. 电子管D. 激光技术答案:A解析:集成电路是微电子技术的核心。

2. 以下哪种材料常用于微电子器件的制造()A. 钢铁B. 塑料C. 硅D. 木材答案:C解析:硅是微电子器件制造中常用的半导体材料。

3. 微电子技术中,芯片制造工艺的精度通常用()来衡量。

A. 纳米B. 微米C. 毫米D. 厘米答案:A解析:芯片制造工艺精度通常用纳米来衡量。

4. 集成电路中,基本的逻辑门包括()A. 与门、或门、非门B. 加法门、减法门C. 乘法门、除法门D. 以上都不对答案:A解析:与门、或门、非门是集成电路中的基本逻辑门。

5. 微电子技术的发展使得计算机的体积越来越()A. 大B. 小C. 不变D. 随机答案:B解析:微电子技术进步使计算机体积逐渐变小。

6. 以下哪个不是微电子技术的应用领域()A. 航空航天B. 农业种植C. 通信D. 医疗答案:B解析:农业种植通常较少直接应用微电子技术。

7. 在微电子制造中,光刻技术的作用是()A. 刻蚀电路B. 沉积材料C. 图案转移D. 检测缺陷答案:C解析:光刻技术主要用于图案转移。

8. 微电子封装技术的主要目的是()A. 保护芯片B. 提高性能C. 便于连接D. 以上都是答案:D解析:微电子封装技术能保护芯片、提高性能并便于连接。

9. 摩尔定律指出,集成电路上可容纳的晶体管数目约每隔()翻一番。

A. 18 个月B. 2 年C. 5 年D. 10 年答案:A解析:摩尔定律表明约每隔18 个月集成电路上晶体管数目翻番。

10. 微电子技术中的掺杂工艺是为了改变半导体的()A. 电阻B. 电容C. 电导D. 电感答案:C解析:掺杂改变半导体的电导特性。

11. 以下哪种设备常用于微电子制造中的检测()A. 显微镜B. 示波器C. 扫描仪D. 电子显微镜答案:D解析:电子显微镜常用于微电子制造中的检测。

微电子工艺计算题答案

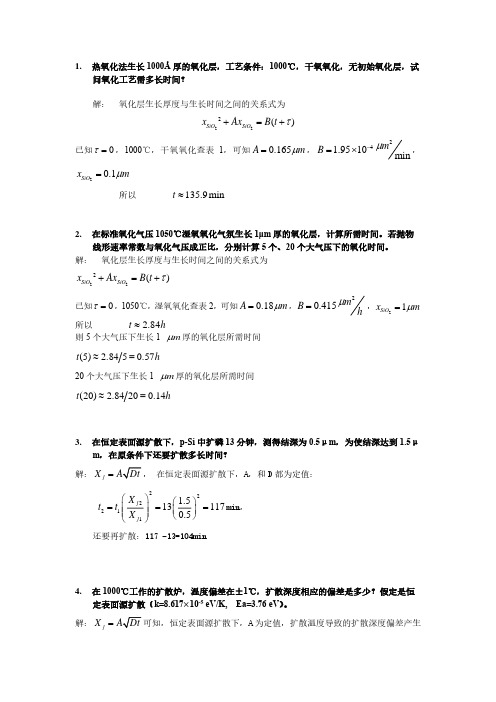

1. 热氧化法生长1000Å厚的氧化层,工艺条件:1000℃,干氧氧化,无初始氧化层,试问氧化工艺需多长时间?解: 氧化层生长厚度与生长时间之间的关系式为222()SiO SiO x Ax B t τ+=+已知0τ=,1000℃,干氧氧化查表1,可知0.165A m μ=,241.9510min m B μ−=⨯,20.1SiO x m μ=所以 135.9min t ≈2. 在标准氧化气压1050℃湿氧氧化气氛生长1μm 厚的氧化层,计算所需时间。

若抛物线形速率常数与氧化气压成正比,分别计算5个、20个大气压下的氧化时间。

解: 氧化层生长厚度与生长时间之间的关系式为222()SiO SiO x Ax B t τ+=+已知0τ=,1050℃,湿氧氧化查表2,可知0.18A m μ=,20.415m B h μ=,21SiO x m μ= 所以 2.84t h ≈则5个大气压下生长1 m μ厚的氧化层所需时间(5) 2.8450.57t h ≈=20个大气压下生长1 m μ厚的氧化层所需时间(20) 2.84200.14t h ≈=3. 在恒定表面源扩散下,p-Si 中扩磷13分钟,测得结深为0.5μm ,为使结深达到1.5μm ,在原条件下还要扩散多长时间?解:j X =, 在恒定表面源扩散下,A ,和D 都为定值: 222211 1.5131170.5j j X t t X ⎛⎫⎛⎫=== ⎪ ⎪ ⎪⎝⎭⎝⎭min , 还要再扩散:117 -13=104min4. 在1000℃工作的扩散炉,温度偏差在±1℃,扩散深度相应的偏差是多少?假定是恒定表面源扩散(k=8.617×10-5 eV/K, Ea=3.76 eV )。

解:j X =可知,恒定表面源扩散下,A 为定值,扩散温度导致的扩散深度偏差产生主要来源于扩散系数差由公式 0exp a E D D kT −⎡⎤=⎢⎥⎣⎦:10011000101.35%j j X X ===999100098.66%j j X X ===5. 30keV 、1012ions/cm 2 B 11注入Si 中,求注入的峰值深度和峰值浓度(查图时,R p 精确到0.1μm ,ΔR p 精确到0.01μm )。

微电子工艺技术 复习要点答案(完整版)

第四章晶圆制造1.CZ法提单晶的工艺流程。

说明CZ法和FZ法。

比较单晶硅锭CZ、MCZ和FZ三种生长方法的优缺点。

答:1、溶硅2、引晶3、收颈4、放肩5、等径生长6、收晶。

CZ法:使用射频或电阻加热线圈,置于慢速转动的石英坩埚内的高纯度电子级硅在1415度融化(需要注意的是熔硅的时间不宜过长)。

将一个慢速转动的夹具的单晶硅籽晶棒逐渐降低到熔融的硅中,籽晶表面得就浸在熔融的硅中并开始融化,籽晶的温度略低于硅的熔点。

当系统稳定后,将籽晶缓慢拉出,同时熔融的硅也被拉出。

使其沿着籽晶晶体的方向凝固。

籽晶晶体的旋转和熔化可以改善整个硅锭掺杂物的均匀性。

FZ法:即悬浮区融法。

将一条长度50-100cm 的多晶硅棒垂直放在高温炉反应室。

加热将多晶硅棒的低端熔化,然后把籽晶溶入已经熔化的区域。

熔体将通过熔融硅的表面张力悬浮在籽晶和多晶硅棒之间,然后加热线圈缓慢升高温度将熔融硅的上方部分多晶硅棒开始熔化。

此时靠近籽晶晶体一端的熔融的硅开始凝固,形成与籽晶相同的晶体结构。

当加热线圈扫描整个多晶硅棒后,便将整个多晶硅棒转变成单晶硅棒。

CZ法优点:①所生长的单晶的直径较大,成本相对较低;②通过热场调整及晶转,坩埚等工艺参数的优化,可以较好的控制电阻率径向均匀性。

缺点:石英坩埚内壁被熔融的硅侵蚀及石墨保温加热元件的影响,易引入氧、碳杂质,不易生长高电阻率单晶。

FZ法优点:①可重复生长,提纯单晶,单晶纯度较CZ法高。

②无需坩埚、石墨托,污染少③高纯度、高电阻率、低氧、低碳④悬浮区熔法主要用于制造分离式功率元器件所需要的晶圆。

缺点:直径不如CZ法,熔体与晶体界面复杂,很难得到无位错晶体,需要高纯度多晶硅棒作为原料,成本高。

MCZ:改进直拉法优点:较少温度波动,减轻溶硅与坩埚作用,降低了缺陷密度,氧含量,提高了电阻分布的均匀性2.晶圆的制造步骤【填空】答:1、整形处理:去掉两端,检查电阻确定单晶硅达到合适的掺杂均匀度。

2、切片3、磨片和倒角4、刻蚀5、化学机械抛光3. 列出单晶硅最常使用的两种晶向。

微电子工艺习题参考解答

CRYSTAL GROWTH AND EXPITAXY1.画出一50cm 长的单晶硅锭距离籽晶10cm 、20cm 、30cm 、40cm 、45cm 时砷的掺杂分布。

(单晶硅锭从融体中拉出时,初始的掺杂浓度为1017cm -3) 2.硅的晶格常数为?.假设为一硬球模型: (a)计算硅原子的半径。

(b)确定硅原子的浓度为多少(单位为cm -3)(c)利用阿伏伽德罗(Avogadro)常数求出硅的密度。

3.假设有一l0kg 的纯硅融体,当硼掺杂的单晶硅锭生长到一半时,希望得到 Ω·cm 的电阻率,则需要加总量是多少的硼去掺杂4.一直径200mm 、厚1mm 的硅晶片,含有的硼均匀分布在替代位置上,求: (a)硼的浓度为多少(b)硼原子间的平均距离。

5.用于柴可拉斯基法的籽晶,通常先拉成一小直径的狭窄颈以作为无位错生长的开始。

如果硅的临界屈服强度为2×106g/cm2,试计算此籽晶可以支撑的200mm 直径单晶硅锭的最大长度。

6.在利用柴可拉斯基法所生长的晶体中掺入硼原子,为何在尾端的硼原子浓度会比籽晶端的浓度高7.为何晶片中心的杂质浓度会比晶片周围的大8.对柴可拉斯基技术,在k 0=时,画出C s /C 0值的曲线。

9.利用悬浮区熔工艺来提纯一含有镓且浓度为5×1016cm -3的单晶硅锭。

一次悬浮区熔通过,熔融带长度为2cm ,则在离多远处镓的浓度会低于5×1015cm -3 10.从式L kx s e k C C /0)1(1/---=,假设k e =,求在x/L=1和2时,C s /C 0的值。

11.如果用如右图所示的硅材料制造p +-n 突变结二极管,试求用传统的方法掺杂和用中子辐照硅的击穿电压改变的百分比。

12.由图,若C m =20%,在T b 时,还剩下多少比例的液体13.用图解释为何砷化镓液体总会变成含镓比较多14.空隙n s 的平衡浓度为Nexp[-E s /(kT)],N 为半导体原子的浓度,而E s 为形成能量。

微电子工艺技术复习要点答案(完整版)

微电子工艺技术复习要点答案(完整版)晶圆制造1.CZ法提单晶的工艺流程。

说明CZ法和FZ法。

比较单晶硅锭CZ、MCZ和FZ三种生长方法的优缺点。

答:1、溶硅2、引晶3、收颈4、放肩5、等径生长6、收晶。

CZ法:使用射频或电阻加热线圈,置于慢速转动的石英坩埚内的高纯度电子级硅在1415度融化(需要注意的是熔硅的时间不宜过长)。

将一个慢速转动的夹具的单晶硅籽晶棒逐渐降低到熔融的硅中,籽晶表面得就浸在熔融的硅中并开始融化,籽晶的温度略低于硅的熔点。

当系统稳定后,将籽晶缓慢拉出,同时熔融的硅也被拉出。

使其沿着籽晶晶体的方向凝固。

籽晶晶体的旋转和熔化可以改善整个硅锭掺杂物的均匀性。

即悬浮区融法。

将一条长度50-100cm 的多晶硅棒垂直放在高温炉反应室。

加热将多晶硅棒的低端熔化,然后把籽晶溶入已经熔化的区域。

熔体将通过熔融硅的表面张力悬浮在籽晶和多晶硅棒之间,然后加热线圈缓慢升高温度将熔融硅的上方部分多晶硅棒开始熔化。

此时靠近籽晶晶体一端的熔融的硅开始凝固,形成与籽晶相同的晶体结构。

当加热线圈扫描整个多晶硅棒后,便将整个多晶硅棒转变成单晶硅棒。

CZ法优点:①所生长的单晶的直径较大,成本相对较低;②通过热场调整及晶转,坩埚等工艺参数的优化,可以较好的控制电阻率径向均匀性。

缺点:石英坩埚内壁被熔融的硅侵蚀及石墨保温加热元件的影响,易引入氧、碳杂质,不易生长高电阻率单晶。

①可重复生长,提纯单晶,单晶纯度较CZ法高。

②无需坩埚、石墨托,污染少③高纯度、高电阻率、低氧、低碳④悬浮区熔法主要用于制造分离式功率元器件所需要的晶圆。

缺点:直径不如CZ法,熔体与晶体界面复杂,很难得到无位错晶体,需要高纯度多晶硅棒作为原料,成本高。

改进直拉法优点:较少温度波动,减轻溶硅与坩埚作用,降低了缺陷密度,氧含量,提高了电阻分布的均匀性2.晶圆的制造步骤答:1、整形处理:去掉两端,检查电阻确定单晶硅达到合适的掺杂均匀度。

2、切片3、磨片和倒角4、刻蚀5、化学机械抛光3. 列出单晶硅最常使用的两种晶向。

微电子工艺习题参考解答

微电子工艺习题参考解答

CRYSTAL GROWTH AND EXPITAXY 1.画出一50cm 长的单晶硅锭距离籽晶10cm 、20cm 、30cm 、40cm 、45cm 时砷的掺杂分布。(单晶硅锭从融体中拉出 时,初始的掺杂浓度为1017cm -3) 2.硅的晶格常数为5.43?.假设为一硬球模型: (a)计算硅原子的半径。 (b)确定硅原子的浓度为多少(单位为cm -3)? (c)利用阿伏伽德罗(Avogadro)常数求出硅的密度。 3.假设有一l0kg 的纯硅融体,当硼掺杂的单晶硅锭生长到一半时,希望得到0.01 Ω·cm 的电阻率,则需要加总量是多少的硼 去掺杂? 4.一直径200mm 、厚1mm 的硅晶片,含有5.41mg 的硼均匀分布在替代位置上,求: (a)硼的浓度为多少? (b)硼原子间的平均距离。 5.用于柴可拉斯基法的籽晶,通常先拉成一小直径(5.5mm)的狭窄颈以作为无位错生长的开始。如果硅的临界屈服强度为 2×106g/cm2,试计算此籽晶可以支撑的200mm 直径单晶硅锭的最大长度。 6.在利用柴可拉斯基法所生长的晶体中掺入硼原子,为何在尾端的硼原子浓度会比籽晶端的浓度高? 7.为何晶片中心的杂质浓度会比晶片周围的大? 8.对柴可拉斯基技术,在k 0=0.05时,画出C s /C 0值的曲线。 9.利用悬浮区熔工艺来提纯一含有镓且浓度为5×1016cm -3 的单晶硅锭。一次悬浮区熔通过,熔融带长度为2cm ,则在离多远处镓的浓度会低于5×1015cm -3? 10.从式L kx s e k C C /0)1(1/---=,假设k e =0.3,求在x/L=1和2时,C s /C 0的值。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1. What is a wafer? What is a substrate? What is a die?什么是硅片,什么是衬底,什么是芯片答:硅片是指由单晶硅切成的薄片;芯片也称为管芯(单数和复数芯片或集成电路);硅圆片通常称为衬底。

2. List the three major trends associated with improvement in microchip fabrication technology, and give a short description of each trend.列出提高微芯片制造技术相关的三个重要趋势,简要描述每个趋势答:提高芯片性能:器件做得越小,在芯片上放置得越紧密,芯片的速度就会提高。

提高芯片可靠性:芯片可靠性致力于趋于芯片寿命的功能的能力。

为提高器件的可靠性,不间断地分析制造工艺。

降低芯片成本:半导体微芯片的价格一直持续下降。

3. What is the chip critical dimension (CD)? Why is this dimension important?什么是芯片的关键尺寸,这种尺寸为何重要答:芯片的关键尺寸(CD)是指硅片上的最小特征尺寸;因为我们将CD作为定义制造复杂性水平的标准,也就是如果你拥有在硅片某种CD 的能力,那你就能加工其他所有特征尺寸,由于这些尺寸更大,因此更容易产生。

4. Describe scaling and its importance in chip design.描述按比例缩小以及在芯片设计中的重要性答:按比例缩小:芯片上的器件尺寸相应缩小是按比例进行的重要性:为了优电学性能,多有尺寸必须同时减小或按比例缩小。

5. What is Moore's law and what does it predict?什么是摩尔定律,它预测了什么答:摩尔定律:当价格不变时,集成电路上可容纳的晶体管数,月每隔18个月便会增加1倍,性能也将提升1倍。

预言在一块芯片上的晶体管数大约每隔一年翻一番。

第二章6. What is the advantage of gallium arsenide over silicon?砷化镓相对于硅的优点是什么答:优点:具有比硅更高的电子迁移率;减小寄生电容和信号损耗的特性;集成电路的速度比硅电路更快;材料的电阻率更大。

7. What is the primary disadvantage of gallium arsenide over silicon?砷化镓相对于硅的主要缺点是什么答:主要缺点:缺乏天然氧化物;材料的脆性;成本比硅高10倍;有剧毒性在设备,工艺和废物清除设施中特别控制。

8. What is an active component? Give two examples of this type of component.什么是无源元件,举出两个无源元件的例子答:有源器件:在不需要外加电源的条件下,就可以显示其特性的电子元件。

例子:电阻,电容。

9. What are some notable characteristics of bipolar technology? What is biggest drawback to bipolar technology?双极技术有什么显著特征,双极技术的最大缺陷是什么答:显著特征:高速,耐久性和功率控制能力。

最大缺陷:功耗高。

10. What are the benefits of the field-effect transistor (FET)?场效应管有什么优点答:低电压和低功耗。

11. What are the two basic types of FETs? What is the major difference between them?FET的两种基本类型是什么,他们之间的主要区别是什么答:类型:结型(JFET)和金属-氧化物型(MOSFET)半导体。

区别:MOSFET作为场效应管晶体输入端的栅极由一层薄介质与晶体管的其他两极绝缘。

JFET的栅极实际上同晶体管其他电极形成物理的pn结。

12. What are the two categories of MOSFETs? How are they distinguishable from one another?MOSFET有哪两种类型,他们怎样区分答:类型:nMOS(n沟道)和pMOS(p沟道)区分方法:可有各自器件的多数载流来区别。

13. What two IC technologies are used in BiCMOS?BiCMOS使用了哪两种集成电路技术答:采用了CMOS和双极技术14. What could a digital/analog (D/A) converter chipbe used for? What could an analog/digital (A/D) chip be used for?数模转换器芯片能用做什么,模数转换器芯片能用做什么答:数/模转化器芯片可用来提供用做电子机械设备的控制模拟驱动信号。

模/数转换器芯片可用来测量模拟驱动信号的输出。

15. Explain the difference between an enhancement-mode transistor and depletion-mode transistor with regards to their standby condition.解释增强型晶体管和耗尽型晶体管使用情况的区别答:增强型晶体管很好地工作于数字陆机应用中,只需要单极的输入信号控制场效应晶体管。

耗尽型被已经存在的闭合沟道部分开启。

输入电压可以在一个方向变化以提高流过沟道的电流,或者在相反方向降低流过的沟道电流。

如果栅极的输入电压在反向更大地提高,耗尽型晶体管将会断开。

第四章16. Why is it necessary to have monocrystal silicon for wafer fabrication?为什么要用单晶进行硅片制造答:半导体芯片加工需要纯净的单晶硅结构,这是因为单胞重复的单晶结构能够提供制作工艺和器件特性所需要的电学和机械性质。

糟糕的晶体结构和缺陷导致微缺陷的形成。

17.Which crystal plane orientation is most common MOS? Which is most common for bipolar?MOS器件中用的最多的是哪种方向晶向,双极型用的最多的是哪几种答:MOS :(100)面的硅片;双极型:(111)面的硅片18.Define crystal growth. What is the CZ method for crystal growth?定义晶体生长,什么是CZ单晶生长法答:晶体生长:是把半导体级硅的多晶硅块转换成一块大的单晶硅。

CZ单晶生长法:是熔化了的半导体级硅液体变为有正确晶向并且被掺杂成n型或p型的固体硅锭。

19. List seven wafer quality requirements for a silicon wafer.列举硅片的七种质量要求答:物理尺寸;平整度;微粗糙度;氧含量;晶体缺陷;颗粒;体电阻率20. What is an epitaxial layer, and why is it used on wafers?什么是外延层,为什么在硅片上使用它答:在某种情况下,需要硅片有非常纯的与衬底有相同晶体结构的硅表面,还要保持对杂质类型和浓度的控制,这要通过在硅表面沉积一个外延层来达到。

原因是外延层在优化pn结的击穿电压的同时降低了集电极电阻,在适中的电流强度下提高了器件速度。

外延在CMOS集成电路中变得重要起来,因为随着器件尺寸不断缩小它将闩锁效应降到最低。

外延层通常是没有玷污的。

第八章21、What is plasma? Why is RF energy used in plasma?什么是等离子体,为什么要在等离子体中使用RF能量答:等离子是一种中性,高能量,离子化的气体,包含中性原子或分子,带电离子和自由电子。

RF能量的使用可以产生一个高功效的等离子体。

第九章22、List the six distinct production areas in a wafer fab and give a shortdescription of each area.列出芯片厂中6个不同的生产区域并对每一个区域做简单的描述答:扩散:扩散区一般认为是进行高温工艺及薄膜沉积的区域。

光刻:使用黄色莹光管照明使得光刻区与芯片厂中的其他各个区明显不同。

刻蚀:是在硅片上没有光刻胶保护的地方留下永久的图形。

离子注入:采用高电压和磁场来控制并加速离子。

薄膜生长:主要负责生产各个步骤当中的介质层与金属层的沉积。

抛光:为了使硅片表面平坦化,是通过将硅片表面突出的部分减薄到下凹部分的高度实现。

23、Identify the three production areas where photoresistcoated wafers can be found.确定有光刻胶覆盖硅片的三个生产区域答:光刻区,刻蚀区和离子注入区24、What is the purpose of the etch process? Name the most common tools used in this area?刻蚀工艺的目的是什么,这个区中最常用的设备是什么答:目的:硅片上没有光刻胶保护的地方留下永久的图形。

常用设备:等离子刻蚀机,等离子体去胶机和湿法清洗设备。

25、What are the reasons for the thermal anneal process after ion implantation? 离子注入后进行退火工艺的原因是什么答:可使裸露的硅片表面生长一层新的阻挡氧化层;高温使得杂质向硅中移动;可使注入引入的损伤得到修复;使杂质原子与硅原子间的共价键被激活,使得杂质原子成为晶格结构中的一部分。

26、What is shallow trench isolation (STI)? What process did it replace?什么是浅槽隔离(STI),它取代了什么工艺答:浅槽隔离(STI)是在衬底制作的晶体管有源区之间隔离区的一种可选工艺。

取代了局域氧化工艺(LOCOS)第十章27、What is the difference between a grown and a deposited oxide layer?生长氧化层和淀积氧化层间的区别是什么答:在升温环境里,通过外部供给高纯氧气使之与硅衬底反应,可以在硅片上得到一层热生长的氧化层;沉积的氧化层可以通过外部供给氧气和硅源,使它们在腔体中反应,从而在硅片表面形成一层薄膜。