第5章 算术逻辑单元-英文

计算机组原理英文缩写解译

计算机组成原理缩写词汇总第1章计算机系统概论1、ENIAC(Electronic Numerical Integrator And Computer)电子数值积分计算机(说明:第1台电子数字计算机)2、EDV AC(Electronic Discrete Variable Automatic Computer)电子离散变量自动计算机3、CPU(Central Processing Unit)中央处理器,是计算机硬件的核心部件,主要由运算器和控制器组成。

4、ALU (Arithmetic Logic Unit )算术逻辑单元,为运算器的核心部件,其功能是进行算术、逻辑运算。

5、CU(Control Unit)控制单元,为控制器的核心部件,其功能是产生微操作命令序列。

6、ACC(Accumulator)运算器的累加器,是运算器中既能存放运算前的操作数,又能存放运算结果的寄存器。

7、MQ(Multiplier-Quotient Register)运算器的乘商寄存器,乘法运算时存放乘数、除法时存放商的寄存器。

8、MAR(Memory Address Register)存储器地址寄存器,在主存中用来存放欲访问的存储单元的地址。

9、MDR (Memory Data Register)存储器数据寄存器,在主存中用来存放从某单元读出、或要写入某存储单元的数据。

10、PC(Program Counter)程序计数器,其功能是存放当前欲执行指令的地址,并可自动计数形成下一条指令地址。

11、IR(Instruction Register) 指令寄存器,其功能是存放当前正在执行的指令。

12、MIPS(Million Instruction Per Second)百万条指令每秒(说明:运算速度指标)13、CPI(Cycle Per instruction)执行一条指令所需的时钟周期(说明:运算速度指标)为计算机运算速度指标的一种计量单位。

计算机专业英语教程(第5版)翻译完整版

1.1 A Closer Look at the Processor and PrimaryStorage仔细看看处理器和主存储器We have learned that all computers have similar capabilities and perform essentially the same functions, although some might be faster than others. We have also learned that a computer system has input, output, storage, and processing components; that the processor is the “intelligence” of a computer system; and that a single computer system may have several processors. We have discussed how data are represented inside a computer system in electronic states called bits. We are now ready to expose the inner workings of the nucleus of the computer system — the processor.我们已经知道,所有的计算机都具有相似的能力,并且在本质上执行相同的功能,尽管一些可能会比另一些快一点。

我们也知道,一个计算机系统具有输入,输出,存储和处理部件;处理器是一个计算机系统智能核心,并且一个计算机系统可以有许多个处理器。

我们已经讨论过如何在计算机系统内部,用被称作“位”的电子状态来表现数据,现在我们要弄明白计算机系统的核心,即处理器,的内在的工作方式。

计算机组成原理-作业参考答案

第1章计算机系统概论5. 冯诺依曼计算机的特点是什么解:冯诺依曼计算机的特点是:P8(1)计算机由运算器、控制器、存储器、输入设备、输出设备五大部件组成;(2)指令和数据以同同等地位存放于存储器内,并可以按地址访问;(3)指令和数据均用二进制表示;(4)指令由操作码、地址码两大部分组成,操作码用来表示操作的性质,地址码用来表示操作数在存储器中的位置;(5)指令在存储器中顺序存放,通常自动顺序取出执行;(6)机器以运算器为中心(原始冯诺依曼机)。

7. 解释下列概念:主机、CPU、主存、存储单元、存储元件、存储基元、存储元、存储字、存储字长、存储容量、机器字长、指令字长。

解:课本P9-10(1)主机:是计算机硬件的主体部分,由CPU和主存储器MM合成为主机。

(2)CPU:中央处理器,是计算机硬件的核心部件,由运算器和控制器组成;(早期的运算器和控制器不在同一芯片上,现在的CPU内除含有运算器和控制器外还集成了Cache)。

(3)主存:计算机中存放正在运行的程序和数据的存储器,为计算机的主要工作存储器,可随机存取;由存储体、各种逻辑部件及控制电路组成。

(4)存储单元:可存放一个机器字并具有特定存储地址的存储单位。

(5)存储元件:存储一位二进制信息的物理元件,是存储器中最小的存储单位,又叫存储基元或存储元,不能单独存取。

(6)存储字:一个存储单元所存二进制代码的逻辑单位。

(7)存储字长:一个存储单元所存储的二进制代码的总位数。

(8)存储容量:存储器中可存二进制代码的总量;(通常主、辅存容量分开描述)。

(9)机器字长:指CPU一次能处理的二进制数据的位数,通常与CPU的寄存器位数有关。

(10)指令字长:机器指令中二进制代码的总位数。

8. 解释下列英文缩写的中文含义:CPU、PC、IR、CU、ALU、ACC、MQ、X、MAR、MDR、I/O、MIPS、CPI、FLOPS解:全面的回答应分英文全称、中文名、功能三部分。

计算机导论第五章_计算机组成

只读存储器 Read-only memory (ROM) ROM的内容是由制造商写进去的

特性1:用户只能读不能写。

特性 2 :非易失性。当切断电源后, 储存在 ROM 中的数据不会丢失。通常 用来存储那些关机后也不能丢失的程序 或数据

17:28 26

只读存储器 Read-only memory (ROM)

中央处理单元 (CPU) 用于数据的运算.

在大多数体系结构中,它有三个组成部分:

算术逻辑单元 (ALU) 控制单元

寄存器组( 快速存储单元)

17:28 8

Figure 5.2 中央处理单元(CPU)

17:28 9

算术逻辑单元 The arithmetic logic unit (ALU)

算术逻辑单元对数据进行逻辑、移位和算术运算。 逻辑运算:非、与、或、异或 移位运算:逻辑移位运算和算术移位运算。 逻辑移位运算对无符号整数进行向左或右的移位 算术移位运算对带符号整数进行向左或右的移位 算术运算:第4章已讨论整数和实数的算术运算。

17:28 15

i 内存地址用无符号二进制整数定义。

17:28 16

Example 5.1

16千兆字节是(

)字节?

A、 216

解:B

ቤተ መጻሕፍቲ ባይዱ

B、234

C、240

D、244

E、256

16千兆=24×210×220

17:28

17

Example 5.2

16T字节是(

)字节?

A、 216

解:D

B、234

C、240

需要借助激光把转换后的二进制数据刻在具 有反射能力的盘片上。 与磁盘相同,光存储设备也是以二进制数据 的形式来存储信息。

《微机原理与接口A》英文专业词汇

《微机原理与接口A》英文专业词汇《微机原理与接口微机原理与接口A A》英文专业词汇序号英文中文1Microcomputer微型计算机2Microprocesser微处理器3Binary system二进制4Decimal system十进制5Hexadecimal system十六进制6BCD码:Binary Coded Decimal二进制编码的十进制数7ASCII 码(American Standard Code for Information Interchange—美国标准信息交换码8CPU:Central Processing Unit中央处理器9Trigger触发器10Memory存储器11Counter计数器12Synchronous counter同步计数器13Program counter程序计数器14ALU:arithmetic logical unit 算术逻辑单元15Register寄存器16Shifting register移位寄存器17Traveling wave counter行波计数器18Ring counter环形计数器19Accumulator累加器20ROM:Read Only Memory只读存储器21Bit位22Word单字23MAR:Memory Address Register存储地址寄存器24Buffer缓冲器25Main memory主存储器26Memory cycle存取周期27RAM:Random Access Memory随机存取存储器28Byte字节29Double word双字30MDR:Memory Data Register存储数据寄存器31Cache高速缓冲存储器32External memory辅助存储器33Access time存取时间34DRAM:Dynamistic RAM动态RAM35PROM: Programmable ROM可编程ROM序号英文中文36EEPROM: Electrically Erasable Programmable ROM电子可檫除可编程ROM37BIU: bus interface unit总线接口部件38CS:code segment register代码段寄存器39SS: Stack Segment Register堆栈段寄存器40IP: Instruction Pointer指令指针寄存器41BP:Base Point Register基址指针寄存器42SI:Source Index Register源变址寄存器43CX:Count Register计数寄存器44DS: Data segment Register数据段寄存器45ES: Extra Segment Register附加段寄存器46SP: Stack Point Register堆栈指针寄存器47BX:Base Register基数寄存器48DI: Destination Index Register目的变址寄存器49DX: Data Register数据寄存器50Interrupt中断51Maskable Interrupt可屏蔽中断52Non-maskable Interrupt非屏蔽中断53Instruction指令54Program程序55Effective Address有效地址56Physical Address物理地址57OFFSET偏移地址58Machine Language机器语言59Assembler汇编程序60Assembly Language汇编语言61Macro Assembler宏汇编语言62High-level Language高级语言63Small Assembler小汇编64Compiler编译程序65Immediate addressing立即数寻址66Register addressing 寄存器寻址方式67Direct addressing 直接寻址方式68Register indirect addressing寄存器间接寻址方式69Register relative addressing寄存器相对寻址方式(或称直接变址寻址方式)70Based indexed addressing基址变址寻址方式71Relative based indexed addressing相对基址变址寻址方式序号英文中文72Intrasegment direct addressing 段内直接寻址73Intrasegment indirect addressing段内间接寻址74Arithmetic Operators算术运算符75Relational Operators关系运算符76Synthetic Operators综合运算符77Logical Operators逻辑运算符78Analytic Operators分析运算符79Object Oriented Language面向对象语言80Port端口81Interface接口82DMA:Direct memory access 直接存储器存取方式83UART:Universal asynchronous Receiver/Transmitter通用异步接收器/发送器84Handshaking握手信号85Parallel communication并行通信86Serial communication串行通信87RXD:Receiver Data接收数据端88Parity Error奇偶错误89Overrun Error 溢出错误90Frame Error帧错误91TXD:Transmitter Data发送数据端92Modem调制解调器93PSK: Phase shift keying 相移键控94FSK:Frequency shift keying频移键控95CRC:Cycle Redundancy check循环冗余校验96Recommended Standard推荐标准97EIA:Electronic Industry Association电子工业协会98Synchronous Character同步字符99Break Character中止字符100Synchronous transmitter同步传送101Asynchronous transmitter异步传送102EOI:End of Interrupt中断结束。

微型计算机复习题

第一章微型计算机概述复习题一、填空题1、微机系统由(硬件系统)和(软件系统)两部分组成。

2、总线按传输的信息种类可分成(数据)、(地址)和(控制)三种。

3、模型机CPU主要由(运算器)、(控制器)和(寄存器)三部分组成。

4、指令格式通常由(操作码)和(操作数)组成。

5、指令的执行分(取指)和(执指)两个阶段。

6、8086有(20 )位地址线,存储器容量为(1M )B。

二、名字解释1、PC :程序计数器2、CACHE:高速缓冲存储器2、FLAGS :标志寄存器3、ALU :算术逻辑运算单元4、ID:指令译码器三、问答题1、微机中各部件的连接采用什么技术?为什么?解答:现代微机中广泛采用总线将各大部件连接起来。

有两个优点:一是各部件可通过总线交换信息,相互之间不必直接连线,减少了传输线的根数,从而提高了微机的可靠性;二是在扩展计算机功能时,只须把要扩展的部件接到总线上即可,十分方便。

2、微机系统的总线结构分哪三种?解答:单总线、双总线、双重总线3、微机系统的主要性能指标(四种)?解答:字长、主频、内存容量、指令系统4、模型机有哪些寄存器,以及作用?解答:通用寄存器组:可由用户灵活支配,用来存放参与运算的数据或地址信息。

地址寄存器:专门用来存放地址信息的寄存器。

程序计数器:它的作用是指明下一条指令在存储器中的地址。

指令寄存器:用来存放当前正在执行的指令代码指令译码器:用来对指令代码进行分析、译码,根据指令译码的结果,输出相应的控制信号5、请举例8、16、准16、32、准32位CPU芯片型号。

解答:8085:8位;8086:16位;8088准16位;80386DX:32位;80386SX:准32位第二章典型微处理器一、填空题1、8086CPU 内部组成结构从功能上讲,可分为__BIU_____和___EU______两部分。

2、8086/8088的四个段寄存器为___DS_____、___ES_____、___SS____、__CS_______3、用来存放CPU状态信息的寄存器是_____FLAGS______。

数字电路英文版第五单元

110 1 1 0

111 0 1 0 111 1 1 1

Output

X

0 0 0 1 0 0 0 1 0 0 0

1 1

1

1 1

AND-OR-Invert Logic ( POS )

A

AB

B

C CD

D

A & ≥1

X

B

X

C&

D

X = AB + CD = (A + B)(C + D)

Signal tracing A troubleshooting technique in which waveforms are observed in a step-by-step manner beginning at the input and working toward the output or vice versa. At each point the observed waveform is compared with the correct signal for that point.

3.

AND-OR Logic ( SOP )

A B

AB

A & ≥1

XB

X

C

C&

D

CD

D

Fig.5-1

X = AB + CD

4.

TABLE 5-1 Truth table for the AND-OR logic in Fig.5-1

X = AB D AB CD

000 0 0 0 000 1 0 0 001 0 0 0 001 1 0 1 010 0 0 0 010 1 0 0 011 0 0 0 011 1 0 1 100 0 0 0 100 1 0 0 101 0 0 0

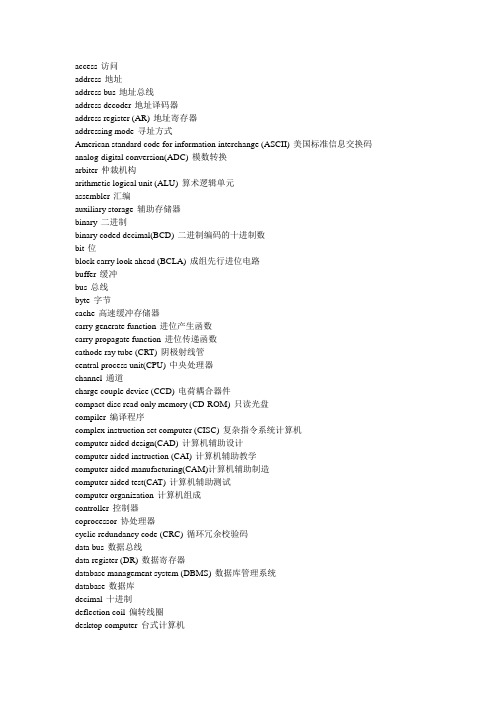

计算机专业词汇中英文对照

access 访问address 地址address bus 地址总线address decoder 地址译码器address register (AR) 地址寄存器addressing mode 寻址方式American standard code for information interchange (ASCII) 美国标准信息交换码analog-digital conversion(ADC) 模数转换arbiter 仲裁机构arithmetic logical unit (ALU) 算术逻辑单元assembler 汇编auxiliary storage 辅助存储器binary 二进制binary coded decimal(BCD) 二进制编码的十进制数bit 位block carry look ahead (BCLA) 成组先行进位电路buffer 缓冲bus 总线byte 字节cache 高速缓冲存储器carry generate function 进位产生函数carry propagate function 进位传递函数cathode ray tube (CRT) 阴极射线管central process unit(CPU) 中央处理器channel 通道charge couple device (CCD) 电荷耦合器件compact disc read only memory (CD-ROM) 只读光盘compiler 编译程序complex instruction set computer (CISC) 复杂指令系统计算机computer aided design(CAD) 计算机辅助设计computer aided instruction (CAI) 计算机辅助教学computer aided manufacturing(CAM)计算机辅助制造computer aided test(CAT) 计算机辅助测试computer organization 计算机组成controller 控制器coprocessor 协处理器cyclic redundancy code (CRC) 循环冗余校验码data bus 数据总线data register (DR) 数据寄存器database management system (DBMS) 数据库管理系统database 数据库decimal 十进制deflection coil 偏转线圈desktop computer 台式计算机destination operand 目的操作数digital camera 数字照相机digital-analog conversion (DAC) 数模转换direct memory access (DMA) 直接存储器存取display 显示器dot pitch 点距dots per inch (dpi) 每英寸点数dynamic random access memory (DRAM) 动态随机存储器effective address (EA) 有效地址electrically erasable programmable read only memory(EEPROM) 电擦除可编程只读存储器electronic design automation (EDA) 电子设计自动化erasable programmable read only memory (EPROM) 可擦编程只读存储器even parity 奇校验excess-3 code 余3 码expansion bus speed 扩展总线速度exponent 阶码extended industry standard architecture (EISA) 扩展工业标准结构firmware 固件fixed point numbers 定点数flag register (FR) 标志寄存器floating point numbers 浮点数flow chart 流程图flyback transformer 回转变压器full adder (FA) 全加器general register (GR) 通用寄存器general-purpose computer 通用计算机gray code 格雷码hardware 硬件hexadecimal 十六进制immediate operand 立即数industrial standard architecture(ISA) 工业标准总线ink-jet printer 喷墨打印机input 输入input device 输入设备instruction 指令instruction cycle 指令周期instruction decoder (ID) 指令译码器instruction register(IR) 指令寄存器instruction set 指令系统interface 接口interpreter 解释程序interrupt 中断interrupt flip-flop 中断触发器interrupt mask register (IMR) 中断屏蔽寄存器interrupt priority level 中断优先级interrupt request register (IRR) 中断请求寄存器interrupt response 中断响应interrupt service register (ISR) 中断服务寄存器interrupt source 中断源keyboard 键盘large scale integration (LSI)大规模集成电路laser printer 激光打印机last in first out (LIFO) 后进先出least recently used(LRU) 近期最少使用(算法)light emitting diode (LED) 发光二极管liquid crystal display (LCD) 液晶显示器machine instruction 机器指令machine language 机器语言magnetic disk 磁盘mainframe 大型机,主机mantissa 尾数mean time between failures (MTBF) 平均无故障时间memory 存储器memory bus speed 内存总线速度memory location 存储单元memory management unit (MMU) 存储器管理单元memory size 存储容量microcomputer 微型机microinstruction 微指令microprocessor 微处理器microprogram 微程序million floating point operations per second (MFLOPS) 每秒百万次浮点运算million instructions per second (MIPS) 每秒百万条指令minicomputer 小型机mnemonics 助记符model 模monochrome monitor 单色显示器mouse 鼠标notebook 笔记本object program 目标程序octal 八进制odd parity 偶校验one’s complement 反码operating system (OS) 操作系统operation code (OP) 操作码operand 操作数optical character reader (OCR) 光学字符阅读机optical disk 光盘output 输出output device 输出设备overflow 溢出paged virtual memory 页式虚拟存储器peripheral component interconnect(PCI) 外围设备互联peripheral device 外围设备personal computer (PC) 个人计算机personal digital assistant (PDA) 个人数字助理pipeline 流水线plasma display panel(PDP) 等离子显示器pop 出栈printer 打印机priority 优先权program counter 程序计数器program status word (PSW) 程序状态字寄存器programmable read only memory (PROM) 可编程序的只读存储器programming 程序设计push 进栈random access memory (RAM) 随机存储器read only memory (ROM) 只读存储器reduced instruction set computer (RISC) 精简指令系统refresh 刷新register 寄存器scanner 扫描仪sector 扇区segment virtual memory 段式虚拟存储器shadow masks 点状阴罩software 软件source operand 源操作数source program 源程序special purpose computer 专业计算机stack 堆栈stack pointer (SP) 堆栈指针static random access memory (SRAM) 静态随机存储器string 字符串stylus printer 针式打印机supercomputer 巨型机supply voltage 工作电压track 磁道trigger 触发器true value 真值complementary code 补码very large scale integration(VLSI) 超大规模集成电路virtual memory 虚拟存储器word length 字长work station 工作站write once read many (WORM) 只写一次型(光盘)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

the bit number increases, the number of product terms and maximum number of literals in a product term in the expression would increase proportionally. limit the fan-in of an AND gate or an OR gate to 5. single-stage carry look-

Computer Organization

Chapter 5 The arithmetic logic unit

Chapter 5 The arithmetic logic unit

5.1 The von Neumann computer model

5.2 Parallel fast adders

Carry look-ahead(超前进位) It reduces significantly the carry creation time by generating the carry signals for all the bits at once directly from the input carry C 0

When executed, the instructions in it are retrieved from memory, one after another, and brought into the processing unit. Decodes instruction, retrieve data, perform operation, stores result in register or memory.

Carry is

transferred serially, and Fi is calculated when Ci-1 is coming. Time consumed is determined by number of bits.

A simple 4 bits serial full adder

The worst-case of

carry propagation occurs when a carry signal propagates from C0 to Cn all the way along the carry propagation circuit.

5.2 Parallel fast adders

Then C1 can be expressed :

C1=X1Y1+(X1+Yt adders

The nature of carry propagation

C2 is

generated as long as one of the following conditions is satisfied:

5.2 Parallel fast adders

Design of a fast adder

How to improve the speed of

adder?

Change the pathway of one by one carry bits

Cn= XnYnCn-1+ XnYnCn-1 + XnYnCn-1+ XnYnCn-1 =(Xn+Yn) Cn-1+ XnYn

5.2 Parallel fast adders

The block carry look-ahead circuit

Theoretically speaking, expression C1~C4 can be

expanded to higher order bits up to n-1 for n>4.

Gi:when Xi and Yi are“1”,no matter whether there is low-order carry bit,the current carry bit is generated.

Pi:when either of Xi and Yi is 1,if there exist low-order carry bit, then Ci-1 is propagated to high-order carry bit

The carry of

Although n

the full adder of the Ci depends on the Ci-1

full adders work in parallel, the carry signals are generated and propagated in sequential.

The nature of carry propagation

C1 is

generated as long as one of these two conditions is meeting: (1) Both of X1,Y1 are“1”; (2) Either of X1,Y1 is“1”,and C0 is“1”。

5.2 Parallel fast adders

Design of full adder

Full

adder with the carry bit Cn-1. Fn and Cn are given as below: Fn=XnYnCn-1+ XnYnCn-1 + XnYnCn-1+ XnYnCn-1 Cn= XnYnCn-1+ XnYnCn-1 + XnYnCn-1+ XnYnCn-1

An arithmetic unit (ALU) is the heart of the CPU

The ALU usually has a binary adder

The performance of the ALU is mainly determined by its adder. We need to design a fast adder to get rid of the excessive carry-propagation time of the ripplecarry adder.

5.2 Parallel fast adders

The nature of carry propagation

Put P1, G1 into C1~C4:

C1=G1+P1C0 C2=G2+P2G1+P2P1C0

(low-order bit)

C3=G3+P3G2+P3P2G1+P3P2P1C0

Control unit

Internal Bus

registers Main memory Input/ Output

CPU

ALU

External Bus

The basic organization of a stored-program computer

5.2 Parallel fast adders

half adders

add result of Xn、Yn and Cn-1 Yn Cn-1

Fn=Xn

5.2 Parallel fast adders

Design of full adder

A n

bit adder can be produced by connecting n full adders

5.2 Parallel fast adders

Design of full adder

Logic maps:

Fn=XnYnCn-1+ XnYnCn-1 + XnYnCn-1+ XnYnCn-1 Cn= XnYnCn-1+ XnYnCn-1

+ XnYnCn-1+ XnYnCn-1

Formed by two F n :

C3=X3Y3 +(X3+Y3)X2Y2 +(X3+Y3)(X2+Y2)X1Y1 +(X3+Y3)(X2+Y2)(X1+Y1)C0 C4=X4Y4 +(X4+Y4)X3Y3 +(X4+Y4)(X3+Y3)X2Y2 +(X4+Y4)(X3+Y3)(X2+Y2)X1Y1 +(X4+Y4)(X3+Y3)(X2+Y2)(X1+Y1)C0

5.3 Analysis of the design of a commercial ALU Chip 5.4 Summary

5.1 The von Neumann computer model

The vast majority of computer systems used today are constructed on the van Neumann computer model. A computer is viewed as a stored program computer. A program is a sequence of instructions, each of which performs a basic operation. Before execution, the program is stored in memory along with data to be manipulated.

Then C2

can be expressed :

C2=X2Y2

+(X2+Y2)X1Y1 +(X2+Y2)(X1+Y1)C0

5.2 Parallel fast adders