线性反馈移位寄存器

我国在zuc序列密码算法

我国在zuc序列密码算法

ZUC(祖冲之)序列密码算法是我国自主研发的一种序列密码算法,该算法主要用于数据的机密性和完整性保护,是实现网络空间安全的基础算法和核心技术。

ZUC算法已成为国际标准ISO/IEC 29189:2017,标志着我国在密码算法领域取得了重要突破。

ZUC算法主要由LFSR(线性反馈移位寄存器)、BR(比特重组)和F (非线性函数)三部分组成。

输入为128位长的密钥和128位长的初始化向量,输出为(n, n),其中n为节拍数(轮数)。

在ZUC算法的实现过程中,首先进行初始化阶段,然后进行多轮迭代,每轮迭代包括以下步骤:

1. 线性反馈移位寄存器(LFSR)操作:根据初始化向量和密钥进行LFSR操作,生成新的状态。

2. 比特重组(BR)操作:将LFSR生成的状态进行比特重组,得到新的数据。

3. 非线性函数(F)操作:将BR操作得到的新数据作为输入,经过非线性函数F处理,生成输出。

4. 输出:经过一定的轮数迭代后,ZUC算法输出一系列32位长的字串,用于加密和解密数据。

ZUC算法在我国商用密码体系中具有重要地位,广泛应用于移动通信、物联网、安全认证等领域。

其成为国际标准,不仅提升了我国在全球密码算法领域的地位,也为全球网络安全提供了更为可靠的技术保障。

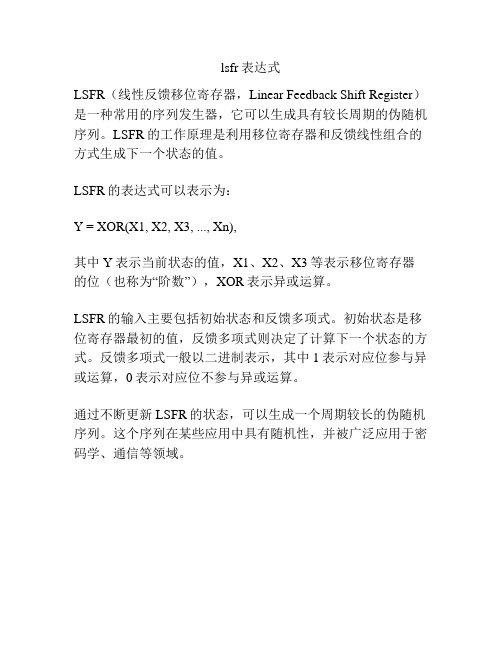

lsfr表达式

lsfr表达式

LSFR(线性反馈移位寄存器,Linear Feedback Shift Register)是一种常用的序列发生器,它可以生成具有较长周期的伪随机序列。

LSFR的工作原理是利用移位寄存器和反馈线性组合的方式生成下一个状态的值。

LSFR的表达式可以表示为:

Y = XOR(X1, X2, X3, ..., Xn),

其中Y表示当前状态的值,X1、X2、X3等表示移位寄存器的位(也称为“阶数”),XOR表示异或运算。

LSFR的输入主要包括初始状态和反馈多项式。

初始状态是移位寄存器最初的值,反馈多项式则决定了计算下一个状态的方式。

反馈多项式一般以二进制表示,其中1表示对应位参与异或运算,0表示对应位不参与异或运算。

通过不断更新LSFR的状态,可以生成一个周期较长的伪随机序列。

这个序列在某些应用中具有随机性,并被广泛应用于密码学、通信等领域。

作业参考答案3级线性反馈移位寄存器在c3=1时可有4种

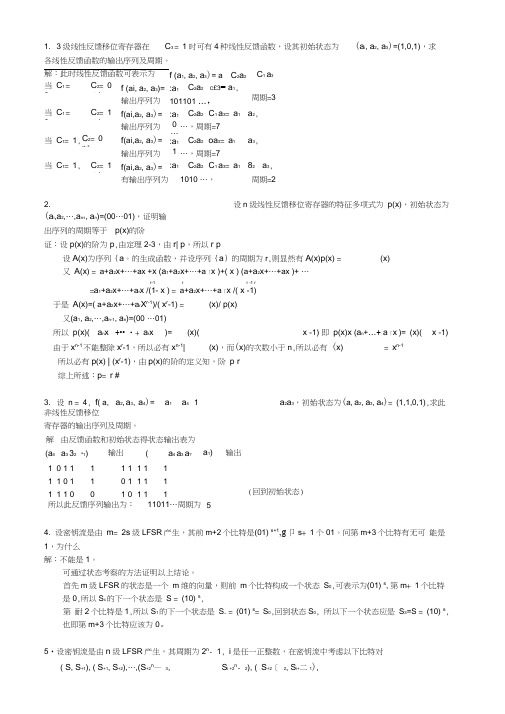

1. 3级线性反馈移位寄存器在 C 3 = 1时可有4种线性反馈函数,设其初始状态为(a i , a 2, a 3)=(1,0,1),求各线性反馈函数的输出序列及周期。

解:此时线性反馈函数可表示为 f (a 1, a 2, a 3)= a C 2a 2 C 1 a 3 当 C 1 = 0, C 2= 0 时, f (ai, a 2, a 3)= :a 1 C 2a 2 C £3= a 1,输出序列为 101101 …, 周期=3 当 C 1 = 0, C 2= 1 时, f (ai,a 2, a 3)= :a 1 C 2a 2 C 1 a 3= a 1 a 2,输出序列为 0……,周期=7当 C 1= 1, C 2= 0 时,f (ai,a 2, a 3)= :a 1 C 2a 2 oa 3= a 1 a 3,输出序列为 1……,周期=7当 C 1= 1, C 2= 1 时, f (ai,a 2, a 3)= :a 1 C 2a 2 C 1 a 3= a 1 82 a 3,有输出序列为 1010 …, 周期=22. 设n 级线性反馈移位寄存器的特征多项式为 p (x ),初始状态为(a i ,a 2,…,a n-i , a n )=(00…01),证明输出序列的周期等于 p (x )的阶证:设p (x )的阶为p ,由定理2-3,由r | p ,所以r p设A (x )为序列{a 。

的生成函数,并设序列{a }的周期为r ,则显然有A (x )p (x ) = (x )又 A (x ) = a+a 2x +…+ax +x (a 1+a 2x +…+a 「x )+( x ) (a+a 2x +…+ax )+ …r-1rr -1 r=a 1+a 2x +…+a r x /(1- x ) = a+a 2x +…+a 「x /( x -1)于是 A (x )=( a+a 2x +…+a r X r-1)/( x r -1) = (x )/ p (x )又(a 1, a 2,…,a n-1, a n )=(00 …01) 所以 p (x )( a n x +•• •+ a r x)=(x )(x -1) 即 p (x )x (a n +…+ a 「x )= (x )( x -1)由于x n-1不能整除x r -1,所以必有x n-1| (x ),而(x )的次数小于n ,所以必有 (x )= x n-1所以必有p (x ) | (x r -1),由p (x )的阶的定义知,阶 p r综上所述:p = r #3. 设 n = 4, f ( a, a 2, a 3, a 4)=a 1 a 4 1a 2a 3,初始状态为(a, a 2, a 3, a 4)= (1,1,0,1),求此非线性反馈移位寄存器的输出序列及周期。

线性反馈与对偶移位寄存器的功能实现

线性反馈与对偶移位寄存器的功能实现091234 谢锦仪一、实验目的:该实验为验证性实验。

通过本实验,使学生切实理解线性反馈移位寄存器与对偶移位寄存器的工作原理,学会编写和运用两种移位寄存器“进动一拍”的程序,培养和锻炼学生对于密码学中各种基本“构造”的编程实现能力。

二、实验内容及完成情况:1. 分别写出实现n-LFSR与 n-DSR(n为正整数)进动一拍的程序(旨在能“由寄存器的一个状态算出紧接着的下一个状态”),要求:寄存器状态的各分量自然地与相应数据存储区的各比特位一一对应,不允许仅1个状态分量就占据1个存储单元(字节、字或双字等)。

2. 基于上述程序完成以下工作:选定一个8次联接多项式,这时检验状态存储区自然形成的1字节二进制数是否与前出现者相同就可判定状态是否开始成圈(即进入周期性重复),据此编制i) 分别计算LFSR与DSR在一个给定初态(由外部响应给出)下输出序列ii) 求出LFSR或DSR之一状态图的程序。

三、实验要求:1.对较低次数的联接多项式,程序计算结果须与手工推算一致;2.抓图显示“输出序列”与“状态图”(附页),不能出现明显错误。

四、结果:1、LFSR2、DSR五、实验体会:这次实验有很大的难度,尤其是对其中移位的操作难倒了不少人。

并且看了老师给的程序后理解不是很深,看了很长时间后才有所了解,后来经过复习以前的课程对LFSR和DSR 有了更深层次的理解之后终于明白了程序改如何编写了。

总的来说,这次实验不但是我对LFSR和DSR两种古典密码有了很好的理解,而且也是我对C语言编程中的位运算也熟悉了不少,相信在以后的工作中会给我带来很大的便利。

六、思考题:为什么“检验状态存储区自然形成的二进制数是否与前出现者相同就可判定状态是否开始成圈(即进入周期性重复)”?答:因为每个状态都有唯一的前一拍状态,对应的所有的状态应该是一一连接的(不一定都在一条线上)。

所以如果出现了2个一样的状态,那么后续的对应状态一定相同。

线性反馈移位寄存器LFSRverilog实现

线性反馈移位寄存器LFSRverilog实现⼀、什么是LFSR?线性反馈移位寄存器(linear feedback shift register, LFSR)是指,给定前⼀状态的输出,将该输出的线性函数再⽤作输⼊的移位寄存器。

异或运算是最常见的单⽐特线性函数:对寄存器的某些位进⾏异或操作后作为输⼊,再对寄存器中的各⽐特进⾏整体移位(百度百科定义)。

线性反馈移位寄存器反馈分为两种,⼀种是IE型的LFSR,即异或门内接的线性反馈移位寄存器:另⼀种是异或门外接的线性反馈移位寄存器,简称EE型LFSR:gi表⽰接不接⼊反馈,只能为0或1,为1即为接⼊,为0不接⼊。

关于线性反馈移位寄存器(LFSR)数学原理更加详细的介绍,可以参考下⾯这篇⽂章。

本⽂主要是介绍如果使⽤verilog来实现LFSR电路的编写。

需要注意的是,LFSR是伪随机的,这意味着它只是接近随机,并不是完全随机的。

这是因为其实从LFSR的任何状态,你都可以预测下⼀个状态。

有⼀些重要的移位寄存器属性需要注意:LFSR是伪随机的,从LFSR的任何状态,都可以预测下⼀个状态。

影响下⼀个状态的⽐特位叫做抽头。

当抽头使⽤XOR门时,全0状态不会出现,这是因为0与0异或将始终产⽣0,此时LFSR将停⽌运⾏。

当抽头使⽤XNOR门时,全1状态不会出现,这是因为1与1同或(异或⾮)将始终产⽣1,此时LFSR将停⽌运⾏。

任何LFSR的最⼤可能迭代次数 = 2^N-1,N为级数,也就是寄存器bit位的个数。

那么怎样的LFSR才能遍历2^N-1个状态,产⽣最⼤的迭代次数呢?也就是到底寄存器的哪些位去组合然后反馈到输⼊端,才能使该LFSR的所有2^N-1个状态都出现呢?这⾥官⽅给了⼀个表,我们可以根据这个表来确定LFSR的结构:需要注意的是LFSR的每⼀位的索引是从1开始,然后到N,⼀共2^N-1个状态(因为使⽤异或反馈时要除去全0状态,使⽤异或⾮反馈时要除去全1状态)。

第八章伪随机序列

二、 游程分布(游程分布的随机性)

游程:一个序列中取值(1 或 0)相同连在一起的元素的统称 游程长度:

分布特性:

1.m序列的一个周期(p=2n-1)中,游程总数为2n-1。

2.当1 <游程长度k ≤n-1,游程数目占总数2-k 当1 ≤k ≤n-2,连“1”和连”0“游程各占一

半

例如 m序列:000111101011001, p=15

cn-1 n

a0

cn=1 输出 ak

线性反馈移位寄存器

它是由n级移位寄存器、时钟发生器(图中未画出)

及一些异或电路连接而成。图中ai(i=1,2,…..n-1)

为某一级移存器状态,Ci表示反馈线连接状态: Ci=1,表示反馈线通,参与反馈; Ci=0,表示断开,不参与反馈。 C0 =Cn=1。

1.

0

0

1

1

0

0

1

1

1

0

1

1

1

1

0

1

1

1

1

0

1

1

0

1

0

1

1

0

1

0

1

1

0

1

15位

0

1

1

0

ak 0

0

1

1

1

0

0

1

0

1

0

0

0

0

1

0

需要自己推导一下

0

0

0

1

1

0

0

0

… … … …

说明:

1.为了m序列发生器组成尽量简单, 就使用项数少的那些本原多项式。

2.本原多项式的递多项式也是本原 多项式,表中每一项多项式可组成 两种发生器。

【常用电路】线性反馈移位寄存器(LFSR)

【常⽤电路】线性反馈移位寄存器(LFSR)读华为技术⽂档《FIFO经验谈》看到的这个电路: FIFO的读写地址产⽣⽐较简单,当读使能有效时,在时钟作⽤下,读地址加1;当写使能有效时,写地址加1。

当FIFO深度较⼤时,同时FIFO的速度要求较⾼时,可以采⽤线性反馈移位计数器(LFSR)。

它的速度⾮常快,但是要牺牲⼀个地址。

针对同步的⼤FIFO,它们的读写地址完全可以使⽤线性反馈移位寄存器 LFSR 产⽣,⽽不是简单的加1操作,极⼤的提⾼了速度,如果对FIFO的利⽤率没有很⾼要求的时候,推荐使⽤该⽅法。

使⽤LFSR的优点是在XILINX的FPGA中布线,可以使⽤LUT直接完成。

1/************************************************************\2* *3* Generation of Read and Write address pointers. They use *4* LFSR counters, which are very fast. Because of the *5* nature of LFSR, one address is sacrificed. *6* *7\************************************************************/8wire read_linearfeedback, write_linearfeedback;910assign read_linearfeedback = ! (read_addr[8] ^ read_addr[4]);11assign write_linearfeedback = ! (write_addr[8] ^ write_addr[4]);1213always @(posedge clock or posedge fifo_gsr)14if (fifo_gsr) read_addr <= 9'h0;15else if (read_allow)16 read_addr <= { read_addr[7], read_addr[6], read_addr[5],17 read_addr[4], read_addr[3], read_addr[2],18 read_addr[1], read_addr[0], read_linearfeedback };1920always @(posedge clock or posedge fifo_gsr)21if (fifo_gsr) write_addr <= 9'h022else if (write_allow)23 write_addr <= { write_addr[7], write_addr[6], write_addr[5],24 write_addr[4], write_addr[3], write_addr[2],25 write_addr[1], write_addr[0], write_linearfeedback };。

线性移位寄存器

2r 2

C(t) (ai )(ait )

i0

2r 1, 1,

t 0 0 t 2r 1

16

习题

一、一个线性移存器如图,

(1)写出该线性移存器的线性递推式。 (2)写出该线性移存器的联接多项式。 (3)写出该线性移存器

二、已知 f (x) x6 x 1 是6次本原多项式,a是 f (x) 生 成的m序列, (1) a的周期是多少? (2) a在的一个周期内,0、1各出现多少次? (3) a在的一个周期内,游程分布如何?

其中 cn 0 ,若 cn 0 我们说该寄存器是退化 的,否则是非退化的。

4

移位寄存器序列空间

符号说明:G(f)表示以f(x)为联结多项式的n级线 性移位寄存器序列构成的空间

定理1:G(f)是GF(q)上的一个n维线性空间。 证明:只需证明G(f)中的任意两个序列的任意线

性组合也属于G(f)即可。即证:

• 在密码学中,我们希望参与变换的序列周期越 长越好,因此对线性反馈移存器我们更感兴趣 的是能达到最长周期的序列,即m序列。

9

本原多项式

若n次多项式f(x)是不可约多项式且 p(f)=qn-1,则称f(x)是GF(q)上的本原多项式。

以本原多项式为连接多项式产生的非零序 列均是m序列。

10

m序列特性

a G( f ),b G( f ), a b G( f ),, GF(q)

特例:当q=2时,G(f)中任意两个序列之和仍然 属于G(f)。

5

(不)可约多项式

(不)可约多项式 定义:若存在g(x),h(x),使得f(x)=g(x)h(x),则

称f(x)是可约多项式;否则,称其为不可约多 项式。

周期为3

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

但对任意整数d,满足d整除2n-1,多项式不能整除xd+1。 用 本 原 多 项 式 x32+x7+x5+x3+x2+x+1 构 造 最 大 周 期 的

LFSR:

b32 … b7 b6 b5 b4 b3 b2 b1 输出位

加密算法的输入是上一个密文块 和下一个明文块的异或

一次处理J位,上一块密文作为加 密算法的输入,用产生一个伪随 机数输出与明文异或作为下一块 的输入(J=8) 与CFB基本相同,只是加密算法 的输入是上一次DES的输出

不能用于密码学

3

6.2 线性反馈移位寄存器

移位寄存器:一个二进制位序列。需要1位时, 所有位都向右移动一位,空出的最左边一位由 寄存器中其他位的一个函数来计算。 移位寄存器的输出为1位,通常是最低位。 周期为输出序列开始重复之前的长度。

反馈移位寄存器:由一个移位寄存器和一个反 馈函数组成。

64

选择 | 丢弃 j位 | 64-j位

···

64

选择 | 丢弃 j位 | 64-j位

jjjj来自+C1

+

C2

j

j

(b) 加P1密

P2

j

j

+

CM

j

PM

17

IV

移位寄存器 64-j位 | j位

移位寄存器 64-j位 | j位

OFB OM-1

移位寄存器 64-j位 | j位

K

DES加密

选择 | 丢弃 j位 | 64-j位

32位的最长周期的LFSR

6

6.3 序列密码的设计与分析

线性复杂度:能够模拟产生器输出的最短的 LFSR的长度n。 低线性复杂度的产生器肯定是不安全的 有高的线性复杂度也不一定安全

相关免疫函数

7

6.6 进位反馈移位寄存器

进位反馈移位寄存器(FCSR):包括一个移位 寄存器,一个反馈函数和一个进位寄存器。

PN

K DES解密 K DES解密 ··· K DES解密

C1

C2

(b) 解密

CN

15

CBC

Time =1 IV P1

+ K DES加密

Time =2 P2

+

K DES加密

(a) 加密C1 C1

K DES解密

C2 C2 K DES解密

IV

+

+

(b) 解密P1

P2

CN-1 ······ K

Time =N PN +

电码本(ECB) 密文分组链接 (CBC) 密文反馈 (CFB) 输出反馈 (OFB)

14

ECB

TIME = 1 P1

TIME = 2 P2

TIME = N PN

K DES加密 K DES加密 ··· K DES加密

C1 (a) 加密

TIME = 1 P1

C2 TIME = 2

P2

CN TIME = N

K

DES加密

选择 | 丢弃 j位 | 64-j位

···

K

DES加密

选择 | 丢弃 j位 | 64-j位

+

C1

+

C2

+

CM

P1

P2

PM

(b) 解密

18

密码模式

模式

描述

典型应用

电子密 码本

( ECB )

密文块 链接

( CBC )

密文反 馈

( CFB )

输出反 馈

( OFB )

用相同的密钥分别对明文块加密

···

64

选择 | 丢弃 j位 | 64-j位

j

j

j

j

+

C1

+

C2

j

j

+

CM

j P1

(a) 加密

IV

移位寄存器 64-j位 | j位

j P2

移位寄存器 64-j位 | j位

CM-1

j PM

移位寄存器 64-j位 | j位

64 K

DES加密

64

K

DES加密

64

K

DES加密

64

选择 | 丢弃 j位 | 64-j位

10

密码学应用

目录

1. 密码学的数学基础 2. 传统密码学算法 3. 对称钥算法 4. 公开钥算法 5. 序列密码 6. 程序安全 7. 操作系统安全 8. 数据库安全 9. 网络安全 10. 灾难恢复计划 11. 信息隐藏与数字水印

12

7.1 保密通信

1. 链路加密 2. 端-端加密

13

7.2 密码模式

4

bn bn-1 … b4 b3 b2 b1

反馈函数

反馈移位寄存器

线性反馈移位寄存器(LFSR):反馈函数为寄 存器中特定位的异或。 这些位的列表称为一个选择序列。 具有特定选择序列的LFSR会遍历所有的2n-1 个内部状态,为最大周期的LFSR。

m序列:最大周期的LFSR产生的输出序列。 最大周期的LFSR的选择序列构成的多项式加上常数1

复习上节课的内容

1

6 序列密码

6.1 线性同余产生器 6.2 线性反馈移位寄存器 6.3 序列密码的设计与分析 6.4 进位反馈移位寄存器 6.5 非线性反馈移位寄存器 6.6 设计序列密码的方法

2

6.1 线性同余产生器

线性同余产生器:伪随机序列产生器 Xn = (aXn-1+b) mod m Xn为序列中第n个数,Xn-1为序列中第n-1个数 变量a,b和m为常数 X0为密钥或种子 最大周期:m-1

进位寄存器:将选择序列的各位相加,并加上 进位寄存器的内容,结果模2成为新位,结果除 以2成为进位寄存器的新内容。

和模2

bn bn-1 …

输出位

b4 b3 b2 b1

和

和除以2

进位反馈移位寄存器

8

6.7 非线性反馈移位寄存器

反馈函数可以是任意的 问题:

可能会有倾向性 最大周期可能很低 开始值不同,可能周期不同 序列可能退化

K

DES加密

选择 | 丢弃 j位 | 64-j位

···

K

DES加密

选择 | 丢弃 j位 | 64-j位

+

C1

P1

(a) 加密

IV

移位寄存器 64-j位 | j位

+

C2

P2

移位寄存器 64-j位 | j位

OM-1

+

CM

PM

移位寄存器 64-j位 | j位

K

DES加密

选择 | 丢弃 j位 | 64-j位

9

6.8 设计序列密码的方法

系统理论方法:尽量保证每次设计都为攻击者 设置一个未知且难以解决的问题,使用一套基 本的设计原则和标准。

信息论方法:尽量让攻击者对明文一无所知。 复杂性理论方法:尽量让密码系统基于或等价

于一些已知的数学难题。 随机化方法:尽量通过迫使攻击者在密码分析

中去检查大量无用的数据的方式来产生一个难 以处理的大问题。

DES加密

······

CN CN

K DES解密

CN-1

+

PN

16

CFB

CM-1

IV

移位寄存器 64-j位 | j位

移位寄存器 64-j位 | j位

移位寄存器 64-j位 | j位

64 K

DES加密

64

K

DES加密

64

K

DES加密

64

选择 | 丢弃 j位 | 64-j位

64

选择 | 丢弃 j位 | 64-j位