线性反馈移位寄存器(LFSR)

m序列信号 -回复

m序列信号-回复什么是[m序列信号]?在通信系统和数字信号处理中,[m序列信号]是一种特殊的数列序列,它具有伪随机性和平稳性的特点。

它是一种特定的二进制数列,其数值只能为1或者-1。

m序列信号广泛应用于通信和调制解调中,特别在现代无线通信中是非常重要的一种信号。

m序列信号由一个叫做m序列生成多项式的线性反馈移位寄存器(LFSR)产生。

LFSR是由若干个互相连接的D触发器和异或门构成的电路。

每一个时钟周期,LFSR都会产生一个序列输出位,这个序列输出位就是m序列信号中的一个元素。

m序列信号的长度被定义为2的幂次,通常表示为M=2^L-1,其中L是LFSR的长度。

由于LFSR的反馈结构使得其输出序列是周期性的,周期为2^L-1。

这个周期长度是m序列信号的最长周期,一个m序列信号中总共包含2^L-1个元素。

m序列信号是伪随机的,也就是说它的数值看似随机,但实际上是根据特定的生成多项式生成的。

由于m序列信号有伪随机性质,因此它可以用于调制解调、扩频通信和加扰等应用中。

在扩频通信中,m序列信号被用作扩频码,可以将低速数据扩展到高速信号进行传输。

m序列信号还具有平稳性的特点,也就是说信号的统计特性在时间上是稳定的。

这种平稳性使得m序列信号在通信系统中具有良好的性能和鲁棒性。

此外,m序列信号的自相关函数具有明显的峰值和零交叉特性,这使得可以通过相关性操作来进行信号的解调和检测。

在实际应用中,m序列信号被广泛使用。

例如,它可以应用于扩频通信系统中的码分多址(CDMA)技术,以增加系统容量和提高抗干扰能力。

此外,m序列信号还可以通过生成多项式的选择和级联连接等方法进行改进,以满足更高的性能要求。

总结起来,[m序列信号]是一种特殊的二进制数列序列,具有伪随机性和平稳性的特点。

它由LFSR产生,被广泛应用于通信和调制解调中。

m序列信号的特点使得它在现代无线通信中发挥着重要的作用,为信号传输提供了很大的便利和效率。

zuc算法比特重组br层从上层lfsr寄存器单元

zuc算法比特重组br层从上层lfsr寄存器单元

ZUC算法是中国自主设计的一种流密码算法,主要用于无线通信或数

据传输的加密保护。

在ZUC算法中,比特重组(Bit Reorganization,BR)层负责从上层LFSR(线性反馈移位寄存器)寄存器单元中获取输入,进

行比特重组,然后输出给下一层。

比特重组层的作用是对输入比特流进行重组,改变其顺序和位置,从

而增强算法的安全性和抗攻击能力。

具体来说,BR层会将多个输入比特

合并成一个更长的比特串,并根据一定规则重组比特的位置,形成新的比

特串。

这个新的比特串会作为下一层LFSR的输入,继续流加密过程。

BR层的设计很重要,因为它直接影响到算法的安全性。

在ZUC算法中,BR层采用了一个巧妙的设计,通过增加输入比特的多样性,提高了

算法的随机性和强度。

具体来说,BR层会在输入比特之间插入特定的冗

余比特,增加不确定性,使得攻击者难以猜测和预测输入比特的分布情况。

这种设计能够有效抵御统计分析和差分攻击等常见攻击手段。

此外,BR层还对输出比特进行重组,以保证输出比特的随机性和均

匀性。

通过对输入和输出比特的巧妙重组,ZUC算法能够提供高强度的密

钥流,从而保证了加密过程的安全性和可靠性。

综上所述,比特重组(BR)层在ZUC算法中扮演着非常重要的角色,

它通过改变输入比特的顺序和位置,增加输入比特的多样性,提高算法的

随机性和强度,从而增强了算法的安全性和抗攻击能力。

BR层的设计需

要兼顾安全性和性能,以保证加密过程的有效性和可靠性。

线性反馈移位寄存器(LFSR)

最近一直在研究信道编码,发现在信道编码里面有一个电路比较重要也比较有趣,那就是线性反馈移位寄存器LFSR ,相信大家对LFSR 电路也不陌生了,在通信领域lfsr有着很广泛的应用,比如说M序列,扰码,信道编码,密码学这方面都有很广泛的应用,LFRS的结构一般如下图:其中他需要一个生成多项式为:这个多项式是一个本原多项式,然后知道这个电路有一些有意思的性质,下面我以m = 3 来做个例子具体的电路图如下所示:假设开始的时候(D2,D1,D0 )= (0,0,1),那么每过一个时钟周期会进行跳变一次,可以看到具体的跳变如下所示:然后我们可以看到这个计数器循环起来了,很好玩吧,无论进入那样一个状态除了0之外,都可以循环着回来,其实这里就相当于了一个3bit的伪随机数,很有意思,不是所有的多项式都有这个特性,我们现在在从数学上面来看看这个问题,其实最上面的电路是可以看成是一个除法电路,在Galois域的一个除法电路。

现在假设的是R(x)是寄存器中剩余的数据,M(x)是输入的码字多项式,然后数学公式可以表示成:然后我分别计算出了M(x)的各种情况,然后我们单独进行一下7次方的运算发现7次方的运算和0次的时候的余数是一样的然后我们发现其实在上面的电路中对多项式的除法也是可以循环起来的,可以验证的是把这个记成上面的式子是可以循环的,然后我又想到了CRC的计算,CRC的计算也可以通过一个除法电路来实现, 假设码子多项式为生成多项式为那么CRC的码字为这样我们同样可以用LFSR电路来进行实现首先对M(x)乘以一个x的r次方,然后去去除G(x),在电路上的表现就是所以在输入码字以后还需要多输入r拍的0这样才能使最后的CRC码字数据.同理这个电路也可以进行CRC校验,把生成的数据全部都依次输入进这个Love is not a maybe thing. You know when you love someone.。

zuc算法的lfsr部分中移位寄存器总长度

zuc算法的lfsr部分中移位寄存器总长度ZUC算法中的LFSR(线性反馈移位寄存器)部分是该算法的关键组成部分之一,它的长度对于算法的安全性和性能起着重要的作用。

在这篇文章中,我们将全面介绍ZUC算法中LFSR部分的总长度,并解释它对于算法的性能和安全性的影响,以及如何选择合适的长度。

LFSR是一种基于位运算的寄存器,它能够生成伪随机序列。

在ZUC算法中,LFSR被用于生成密钥流,这是一种用于加密和解密数据的关键序列。

因此,LFSR的总长度直接影响了ZUC算法的安全性。

对于ZUC算法,LFSR的总长度是160位。

这个长度是经过密钥扩展算法计算出来的,并且是为了实现算法的安全性而选择的最优长度。

通过使用160位的LFSR,ZUC算法可以生成足够长的密钥流,以确保抵抗各种攻击,包括线性和差分攻击。

但是,LFSR的总长度也会对算法的性能产生一定的影响。

较长的LFSR可能会增加算法的计算复杂性和运算时间。

因此,在设计ZUC算法时,需要平衡安全性和性能。

选择160位的LFSR长度是基于可行性和效率方面的考虑,它既能够提供足够的安全性,又能够保持较高的算法性能。

另外,LFSR的总长度也是一种指导,以帮助开发者进行合理的密码学设计。

在实际应用中,除了选择合适的LFSR长度外,还应该注意密钥的选择和保护、算法的使用方式等其他因素。

只有将这些因素合理结合,才能够确保算法的安全性和性能。

总之,ZUC算法中LFSR部分的总长度为160位。

这个长度既能够满足算法的安全性要求,又能够保持较高的性能。

在实际应用中,开发者应该综合考虑安全性、性能和可行性等因素,选择适当的LFSR长度,并注意其他相关因素的影响,以确保算法的安全性和可靠性。

simulink信道编码中的卷积码

Simulink信道编码是一种用于数字通信系统的重要技术,可用于提高数据传输的可靠性和效率。

其中,卷积码是一种常用的信道编码方案,具有良好的纠错能力和复杂度适中的特点。

本文将重点介绍Simulink信道编码中的卷积码原理、应用和性能分析。

首先,让我们了解一下卷积码的原理。

卷积码是一种线性反馈移位寄存器(Linear Feedback Shift Register,简称LFSR)实现的编码器。

它通过将输入数据序列与生成多项式进行异或运算,生成编码后的输出序列。

卷积码具有很好的纠错能力,可以通过增加编码器的约束长度和选取适当的生成多项式来提高纠错性能。

在Simulink中,我们可以通过使用Convolutional Encoder模块来实现卷积码编码。

该模块可以设置编码器的约束长度、生成多项式以及输入数据的采样率等参数。

通过将输入数据连接到Convolutional Encoder模块的输入端口,我们可以得到编码后的输出数据序列。

此外,Simulink还提供了其他相关模块,如Viterbi Decoder模块用于卷积码解码和Error Rate Calculation模块用于计算解码后的误码率等。

在实际应用中,卷积码广泛应用于无线通信系统中的信道编码环节。

通过引入卷积码编码和解码,可以有效降低信道传输过程中的误码率,提高通信系统的可靠性。

此外,卷积码还被广泛用于数字广播、卫星通信、移动通信等领域。

在Simulink中进行卷积码性能分析时,我们可以通过模拟不同信噪比(Signal-to-Noise Ratio,简称SNR)下的误码率来评估卷积码的性能。

通过调整信噪比,我们可以观察到误码率与信噪比之间的关系,并选择适当的编码参数以满足系统性能要求。

此外,我们还可以通过比较不同约束长度和生成多项式的卷积码来分析它们在不同信道条件下的性能差异。

总之,Simulink信道编码中的卷积码是一种重要的数字通信技术,具有良好的纠错能力和适中的复杂度。

bist线性反馈移位寄存器LFSR

Pin overhead -- At least 1 pin needed to activate BIST operation Performance overhead – extra path delays due to BIST Yield loss – due to increased chip area or more chips in system because of BIST Reliability reduction – due to increased area Increased BIST hardware complexity – happens when BIST hardware is made testable

BIST Hierarchy

Pattern Generator CUT Response Analyzer

线性反馈移位寄存器LFSRverilog实现

线性反馈移位寄存器LFSRverilog实现⼀、什么是LFSR?线性反馈移位寄存器(linear feedback shift register, LFSR)是指,给定前⼀状态的输出,将该输出的线性函数再⽤作输⼊的移位寄存器。

异或运算是最常见的单⽐特线性函数:对寄存器的某些位进⾏异或操作后作为输⼊,再对寄存器中的各⽐特进⾏整体移位(百度百科定义)。

线性反馈移位寄存器反馈分为两种,⼀种是IE型的LFSR,即异或门内接的线性反馈移位寄存器:另⼀种是异或门外接的线性反馈移位寄存器,简称EE型LFSR:gi表⽰接不接⼊反馈,只能为0或1,为1即为接⼊,为0不接⼊。

关于线性反馈移位寄存器(LFSR)数学原理更加详细的介绍,可以参考下⾯这篇⽂章。

本⽂主要是介绍如果使⽤verilog来实现LFSR电路的编写。

需要注意的是,LFSR是伪随机的,这意味着它只是接近随机,并不是完全随机的。

这是因为其实从LFSR的任何状态,你都可以预测下⼀个状态。

有⼀些重要的移位寄存器属性需要注意:LFSR是伪随机的,从LFSR的任何状态,都可以预测下⼀个状态。

影响下⼀个状态的⽐特位叫做抽头。

当抽头使⽤XOR门时,全0状态不会出现,这是因为0与0异或将始终产⽣0,此时LFSR将停⽌运⾏。

当抽头使⽤XNOR门时,全1状态不会出现,这是因为1与1同或(异或⾮)将始终产⽣1,此时LFSR将停⽌运⾏。

任何LFSR的最⼤可能迭代次数 = 2^N-1,N为级数,也就是寄存器bit位的个数。

那么怎样的LFSR才能遍历2^N-1个状态,产⽣最⼤的迭代次数呢?也就是到底寄存器的哪些位去组合然后反馈到输⼊端,才能使该LFSR的所有2^N-1个状态都出现呢?这⾥官⽅给了⼀个表,我们可以根据这个表来确定LFSR的结构:需要注意的是LFSR的每⼀位的索引是从1开始,然后到N,⼀共2^N-1个状态(因为使⽤异或反馈时要除去全0状态,使⽤异或⾮反馈时要除去全1状态)。

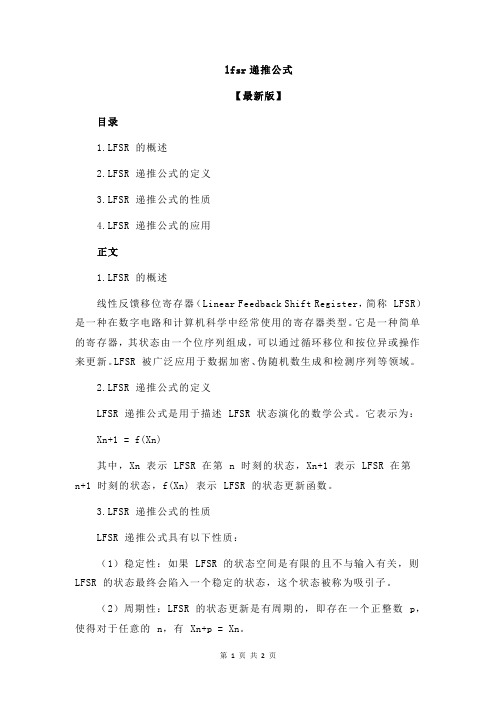

lfsr递推公式

lfsr递推公式【最新版】目录1.LFSR 的概述2.LFSR 递推公式的定义3.LFSR 递推公式的性质4.LFSR 递推公式的应用正文1.LFSR 的概述线性反馈移位寄存器(Linear Feedback Shift Register,简称 LFSR)是一种在数字电路和计算机科学中经常使用的寄存器类型。

它是一种简单的寄存器,其状态由一个位序列组成,可以通过循环移位和按位异或操作来更新。

LFSR 被广泛应用于数据加密、伪随机数生成和检测序列等领域。

2.LFSR 递推公式的定义LFSR 递推公式是用于描述 LFSR 状态演化的数学公式。

它表示为:Xn+1 = f(Xn)其中,Xn 表示 LFSR 在第 n 时刻的状态,Xn+1 表示 LFSR 在第n+1 时刻的状态,f(Xn) 表示 LFSR 的状态更新函数。

3.LFSR 递推公式的性质LFSR 递推公式具有以下性质:(1)稳定性:如果 LFSR 的状态空间是有限的且不与输入有关,则LFSR 的状态最终会陷入一个稳定的状态,这个状态被称为吸引子。

(2)周期性:LFSR 的状态更新是有周期的,即存在一个正整数 p,使得对于任意的 n,有 Xn+p = Xn。

(3)伪随机性:当 LFSR 的状态更新函数设计得当时,LFSR 的状态序列可以生成伪随机数。

这是因为 LFSR 的状态更新具有确定性,但其周期性和不可预测性使得产生的序列看起来像是随机的。

4.LFSR 递推公式的应用LFSR 递推公式在多个领域都有应用,主要包括:(1)数据加密:LFSR 可以用作加密算法中的伪随机数生成器,生成的伪随机数序列可以用作密钥或初始向量。

(2)伪随机数生成:LFSR 可以用来生成伪随机数,这在许多应用场景中是很有用的,例如模拟随机事件或进行蒙特卡洛模拟。

(3)检测序列:LFSR 的状态序列可以用来检测序列,例如在通信系统中检测帧同步码。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

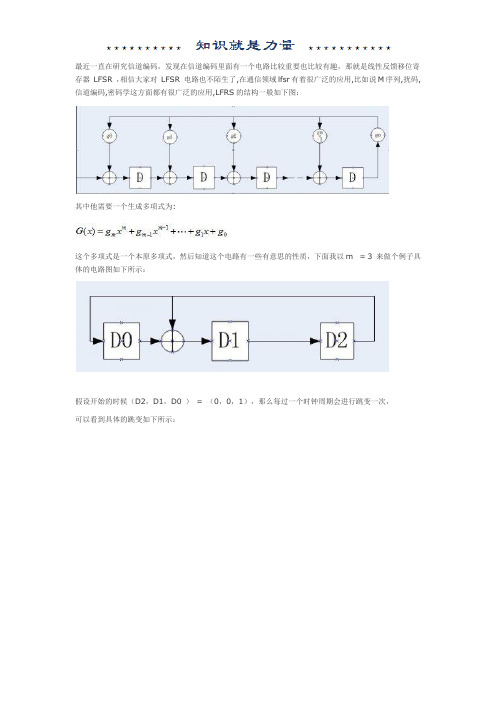

最近一直在研究信道编码,发现在信道编码里面有一个电路比较重要也比较有趣,那就是线性反馈移位寄存器LFSR ,相信大家对LFSR 电路也不陌生了,在通信领域lfsr有着很广泛的应用,比如说M序列,扰码,信道编码,密码学这方面都有很广泛的应用,LFRS的结构一般如下图:

其中他需要一个生成多项式为:

这个多项式是一个本原多项式,然后知道这个电路有一些有意思的性质,下面我以m = 3 来做个例子具体的电路图如下所示:

假设开始的时候(D2,D1,D0 )= (0,0,1),那么每过一个时钟周期会进行跳变一次,

可以看到具体的跳变如下所示:

然后我们可以看到这个计数器循环起来了,很好玩吧,无论进入那样一个状态除了0之外,都可以循环着回来,其实这里就相当于了一个3bit的伪随机数,很有意思,不是所有的多项式都有这个特性,我们现在在从数学上面来看看这个问题,其实最上面的电路是可以看成是一个除法电路,在Galois域的一个除法电路。

现在假设的是R(x)是寄存器中剩余的数据,M(x)是输入的码字多项式,然后数学公式可以表示成:

然后我分别计算出了M(x)的各种情况,

然后我们单独进行一下7次方的运算

发现7次方的运算和0次的时候的余数是一样的

然后我们发现其实在上面的电路中对多项式的除法也是可以循环起来的,可以验证的是

把这个记成

上面的式子是可以循环的,然后我又想到了CRC的计算,CRC的计算也可以通过一个除法电路来实现, 假设码子多项式为

生成多项式为

那么CRC的码字为这样我们同样可以用LFSR电路来进行实现

首先对M(x)乘以一个x的r次方,然后去去除G(x),在电路上的表现就是

所以在输入码字以后还需要多输入r拍的0这样才能使最后的CRC码字数据.

同理这个电路也可以进行CRC校验,把生成的数据全部都依次输入进这个。