74hc595的引脚功能和作用

74hc595中文资料

74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态.三态。

特点 8位串行输入 8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除 100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换 Remote control holding register。

描述 595是告诉的硅结构的CMOS器件, 兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗, PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容 f 0=输出频率(MHz) Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解 595的工作情况74HC595引脚图,管脚图________QB-—|1 16|——VccQC—-|2 15|--QAQD——|3 14|--SIQE—-|4 13|—-/GQF—-|5 12|--RCKQG--|6 11|—-SRCKQH-—|7 10|—-/SRCLRGND- |8 9|-—QH'|________|74595的数据端:QA—-QH: 八位并行输出端,可以直接控制数码管的8个段。

QH':级联输出端。

我将它接下一个595的SI端。

74HC595的工作原理

74HC595的工作原理1.寄存器结构2.数据输入数据输入引脚DS用于将要输出到寄存器的数据串行输入。

数据输入在时钟引脚SH_CP上升沿的时候被寄存器读取。

在一系列上升沿时,数据将从DS引脚传输到寄存器的移位寄存器中。

3.时钟控制时钟引脚SH_CP用于控制数据输入和输出的时钟信号。

在上升沿时,移位寄存器中的数据将被更新。

时钟信号可以是单个脉冲或一个周期性的信号。

4.输出使能输出使能引脚ST_CP用于将并行输出的数据锁存并输出到输出引脚。

当输出使能为高电平时,移位寄存器中的数据被锁存,从而将并行输出的数据传递到输出引脚。

当输出使能为低电平时,输出引脚被禁用。

5.级联连接74HC595芯片具有级联连接的能力,这意味着可以连接多个芯片以扩展输出位数。

使用级联连接时,使用一个芯片作为主芯片,而其他芯片作为从芯片。

主芯片的移位寄存器的输出Q7'连接到从芯片的数据输入DS 上,从而将数据串联传输到从芯片的移位寄存器中。

6.清除清除引脚MR用于清除寄存器的内容,将所有位重置为低电平。

MR为低电平时,寄存器将被清除。

通常在Power-On Reset(POR)时使用该引脚,以确保寄存器的初始状态为低电平。

总结起来,74HC595的工作原理是通过串行输入数据,移位寄存器将数据从输入引脚传输到寄存器中。

通过时钟信号控制,数据逐位传送到并行输出引脚。

通过输出使能信号,输出可以锁存并输出到外部设备。

通过级联连接,可以扩展输出位数。

通过清除引脚,可以将寄存器内容重置为初始状态。

这种工作原理使得74HC595可用于控制大量数字输出,如LED 显示屏、继电器、数码管等。

74HC595简介

74HC595简介DS:串行数据输入,接Arduino的某个数字I/O引脚。

Q0~Q7:8位并行数据输出,可以直接控制8个LED,或者是七段数码管的8个引脚。

Q7′:级联输出端,与下一个74HC595的DS相连,实现多个芯片之间的级联。

SH_CP:移位寄存器的时钟输入。

上升沿时移位寄存器中的数据依次移动一位,即Q0中的数据移到Q1中,Q1中的数据移到Q2中,依次类推;下降沿时移位寄存器中的数据保持不变。

ST_CP:存储寄存器的时钟输入。

上升沿时移位寄存器中的数据进入存储寄存器,下降沿时存储寄存器中的数据保持不变。

应用时通常将ST_CP 置为低点平,移位结束后再在ST_CP端产生一个正脉冲更新显示数据。

MR:重置(RESET),低电平时将移位寄存器中的数据清零,应用时通常将它直接连高电平(VCC)。

OE:输出允许,高电平时禁止输出(高阻态)。

引脚不紧张的情况下可以用Arduino的一个引脚来控制它,这样可以很方便地产生闪烁和熄灭的效果。

实际应用时可以将它直接连低电平(GND)。

在一些不是很复杂的应用中,可以将MR和OE分别接VCC和地,只对DS、SH_CP和ST_CP三个引脚进行相关控制。

二 C语言程序#include<reg52.h>#include<intrins.h>#include<lcd.h>#define uchar unsigned char#define uint unsigned intsbit DS = P2^7;sbit SH_CP = P3^0;sbit ST_CP = P3^1;sbit duanx = P3^2;uchar disp_buffer[4];uchar const table[10]={48,49,50,51,52,53,54,55,56,57}; //1到9的ASCII码uchar const table2[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f,0x77,0x7c,0x39,0x5e,0x79,0x71};//共阴void remove_data(uchar Re_data);void lcd_init(void);void main(void){uint j = 0;uchar *s1 = "VALUE:",temp_data,disp_data,a;write_str(s1,0,0);write_str(s2,0,1);while(1){duanx = 0;a = table2[j++];remove_data(a);delay(100);disp_data = a;temp_data = disp_data/1000; writlcd();write_char(table[temp_data],7,0); temp_data = disp_data%1000/100; writlcd();write_char(table[temp_data],8,0); temp_data = disp_data%100/10; writlcd();write_char(table[temp_data],9,0); temp_data = disp_data%10;write_char(table[temp_data],10,0); if(j == 9 )j = 0;}}void remove_data(uchar Re_data){uint i;for(i=8; i>0; i--){if(Re_data&0x80)//判断高位是否为1 DS = 1;elseDS = 0;SH_CP = 0;_nop_();_nop_();SH_CP = 1;Re_data <<=1; //Re_data左移一位ST_CP = 0;_nop_();_nop_();ST_CP = 1; //上升沿将数据送到输出锁存器_nop_();_nop_();ST_CP = 0;}void lcd_init(void){lcd_rest();lcd_winst(0x01);set_cur(1);其中程序中红色部分便是对74HC595进移位和锁存操作。

74HC595详解

74HC595 详解

工作电压2-6V,推荐5V。

14 脚串行输入:595 的数据来源只有这一个口,一次只能输入一个位,那

幺连续输入8 次,就可以积攒为一个字节了。

13 脚OE 输出使能控制脚:如果它不工作,那幺595 的输出就是高阻态,595 就不受我们程序控制了,这显然违背我们的意愿。

OE 的上面画了一条线,表示他是低电平有效。

于是我们将他接GND。

10 脚SRCLR 位移寄存器清空脚:他的作用就是将位移寄存器中的数据

全部清空,这个很少用到,所以我们一般不让他起作用,也是低电平有效,于是我们给他接VCC。

12 脚RCLK 存储寄存器:数据从位移寄存器转移到存储寄存器,也是需要

时钟脉冲驱动的,这就是12 脚的作用。

它也是上升沿有效。

11 脚SRCLK 移位寄存器时钟输入:当一个新的位数据要进来时,已经进

入的位数据就在移位寄存器时钟脉冲的控制下,整体后移,让出位置。

分析下数据输入和输出过程:

假如,我们要将二进制数据0111 1111 输入到595 的移位寄存器中,下面。

74hc595 工作原理

74hc595 工作原理

74HC595是一种8位移位寄存器,它具有串行输入和并行输

出功能。

其工作原理如下:

1. 74HC595有三个重要的引脚,分别是:

- SER(串行输入):用于输入数据(位),在每个移位时

钟周期中,数据从该引脚输入到寄存器的最低有效位(LSB)。

- SRCLK(移位时钟):用于控制数据移位的时钟信号。

在

每个时钟上升沿,数据从SER输入到寄存器的下一个位。

- RCLK(存储时钟):用于控制数据存储的时钟信号。

在SRCLK完成所有位的移位之后,通过将RCLK引脚拉高,可

以将当前寄存器中的数据复制到并行输出引脚(Q0-Q7)上。

2. 移位操作:

- 在移位操作期间,首先将要存储的数据从SER输入到寄存

器的LSB位。

然后,通过对SRCLK引脚的脉冲上升沿进行计时,数据从SER依次移位到寄存器的每个位。

- 数据移位完成后,可以通过对RCLK引脚的脉冲上升沿进

行计时,将寄存器中的数据复制到并行输出引脚(Q0-Q7)上。

此时,这些引脚上的输出值与寄存器中的数据一致。

3. 并行输出:

- 在并行输出状态下,寄存器中的数据被复制到并行输出引

脚(Q0-Q7)上。

- 每个输出引脚都对应着寄存器中的一个位,输出高电平表

示该位为1,输出低电平表示该位为0。

通过控制移位和存储时钟信号,可以实现串行输入和并行输出之间的转换,使得74HC595能够灵活应用于各种数字逻辑电路和显示驱动电路中。

74LS595,74HC595引脚图,管脚图

74LS595,74HC595引脚图,管脚图74LS595,74HC595 引脚图,管脚图 ________ QB--1 16--Vcc QC--2 15--QA QD--314-- Ds QE--4 13--/ OE QF--5 12-- STcp QG--6 11-- SHcp QH--7 10--/ MR GND- 89--QH ________ 74595 的数据端: QA--QH: 八位并行输出端,可以直接控制数码管的 8 个段。

QH: 级联输出端。

我将它接下一个 595 的 SI 端。

Ds: 串行数据输入端。

74595 的控制端说明:/ MR 10 脚: 低点平时将移位寄存器的数据清零。

通常我将它接 Vcc。

SHcp 11 脚:上升沿时数据寄存器的数据移位。

QA--QB--QC--...--QH;下降沿移位寄存器数据不变。

(脉冲宽度:5V 时,大于几十纳秒就行了。

我通常都选微秒级)STcp 12 脚:上升沿时移位寄存器的数据进入数据存储寄存器,下降沿时存储寄存器数据不变。

通常我将 RCK 置为低电平,当移位结束后,在 RCK 端产生一个正脉冲(5V 时,大于几十纳秒就行了。

我通常都选微秒级),更新显示数据。

/ OE 13 脚: 高电平时禁止输出(高阻态)。

如果单片机的引脚不紧张,用一个引脚控制它,可以方便地产生闪烁和熄灭效果。

比通过数据端移位控制要省时省力。

注:74164 和 74595 功能相仿,都是 8 位串行输入转并行输出移位寄存器。

74164 的驱动电流25mA比 7459535mA的要小14 脚封装,体积也小一些。

74595 的主要优点是具有数据存储寄存器,在移位的过程中,输出端的数据可以保持不变。

这在串行速度慢的场合很有用处,数码管没有闪烁感。

与 164 只有数据清零端相比,595 还多有输出端时能/禁止控制端,可以使输出为高阻态。

74595 的数据端:QA--QH: 八位并行输出端,可以直接控制数码管的 8 个段。

74HC595

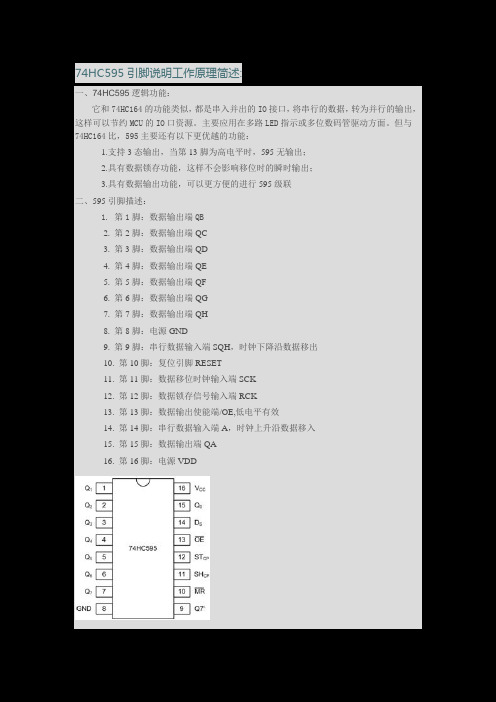

74HC595引脚说明工作原理简述:一、74HC595逻辑功能:它和74HC164的功能类似,都是串入并出的IO接口,将串行的数据,转为并行的输出,这样可以节约MCU的IO口资源。

主要应用在多路LED指示或多位数码管驱动方面。

但与74HC164比,595主要还有以下更优越的功能:1.支持3态输出,当第13脚为高电平时,595无输出;2.具有数据锁存功能,这样不会影响移位时的瞬时输出;3.具有数据输出功能,可以更方便的进行595级联二、595引脚描述:1. 第1脚:数据输出端QB2. 第2脚:数据输出端QC3. 第3脚:数据输出端QD4. 第4脚:数据输出端QE5. 第5脚:数据输出端QF6. 第6脚:数据输出端QG7. 第7脚:数据输出端QH8. 第8脚:电源GND9. 第9脚:串行数据输入端SQH,时钟下降沿数据移出10. 第10脚:复位引脚RESET11. 第11脚:数据移位时钟输入端SCK12. 第12脚:数据锁存信号输入端RCK13. 第13脚:数据输出使能端/OE,低电平有效14. 第14脚:串行数据输入端A,时钟上升沿数据移入15. 第15脚:数据输出端QA16. 第16脚:电源VDD三、74HC595工作原理简述:74HC595是一款具有8位移位寄存器和一个存储器,三态输出功能的驱动芯片。

移位寄存器和存储器分别具有独立的时钟信号。

数据在SHCP的上升沿输入,在STCP的上升沿进入到存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(DS),和一个串行输出(Q7’),和一个异步的低电平复位(MR),存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

四、74HC595实现LED静、动态显示基本原理2.1 静态显示每位LED显示器段选线和74HC595的并行输出端相连,每一位可以独立显示(见图1)。

74hc595工作原理

74hc595工作原理

74HC595是一种8位移位寄存器和输出锁存器。

它起到了扩展IO引脚的作用,通过串行输入数据来控制并行输出。

下面我们将介绍其工作原理。

74HC595由三个主要部分组成:串行输入、移位寄存器和并行输出。

它采用了串行输入并行输出的数据传输方式。

数据是逐位地通过串行输入引脚(SER)输入到移位寄存器(SHIFT REGISTER)中。

在上升沿时钟输入引脚(SRCLK)的控制下,数据逐位地从串行输入向移位寄存器移位。

接下来,通过锁存时钟引脚(RCLK)的上升沿,移位寄存器中的数据被并行锁存到输出寄存器中。

这意味着移位寄存器中的数据被“冻结”在输出寄存器中,不受后续的移位操作影响。

输出寄存器的并行输出引脚(Qa-Qh)可以连接到外部设备或其他电路中,用来控制各种不同的功能。

输出寄存器中的数据可以通过更新移位寄存器的内容来改变,并进一步通过移位寄存器的移位操作改变。

这种工作模式允许我们通过控制串行输入来逐步改变并行输出的状态。

总结一下,74HC595通过串行输入控制并行输出。

数据通过移位寄存器实现从串行输入到并行输出的转换,并通过锁存操作将数据冻结在输出寄存器中。

通过更新移位寄存器和移位操作,我们可以改变并行输出的状态,从而实现对外部设备或电路的控制。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

}

//write 2 bytes to 6b595 void shift_b595_out2(uchar *dat, uchar count1 , uchar count2) {

SRCK =0;

RCK =0; data_tp =dat[count1]; for(i=0; i<16; i++) { if(data_tp&0x80) SER_IN =1; else SER_IN =0; data_tp <<=1; if(i==7) data_tp =dat[count2]; SRCK =1; _nop_(); _nop_(); SRCK= 0; }

于74HC595的输入输出电平兼容LSTTL,NMOS,CMOS电平,且具有较强 的输出负载能力,而被广泛地运用于MCU(微控制器)、MPU(微处 理器)的I/O口扩展。 74HC595在5V供电的时候能够达到30MHz的时钟速度,每个并行输出端 口均能承受20mA的灌电流和拉电流。这个特点保证了不用增加额外的 扩流电路即可轻松的驱动LED。它输入端允许500nS的上升(下降)时 间,对严重畸形的时钟脉冲仍能检测。这样就可以容纳较大的传输线对 地电容,使本设计的抗干扰能力增强。 74HC595并行输出端与LED模块列线之间通过20Ω的电阻连接,这里电 阻起到分压,去除红色LED的并联嵌位作用。使红绿两组LED均能正常 发光。 由于LED显示屏的工作电流时刻在变化,造成了系统电压的波动。这种 电压波动有高频成分,也有低频成分。轻则对周围无线电环境造成电磁 污染,重则使系统时钟紊乱,逻辑错误。为避免此,在每个74HC595的 电源VCC和GND旁边都并联了两个电容,用于滤波和退耦。稳定系统 电压,旁路掉电源中的高频脉动成份。消除自激,减小对外杂散电磁辐 射,提高EMI电磁兼容性。 74HC595的引脚及逻辑功能如图4.2

74HC595N,8 位移位寄存器,具有三态输出锁存 型号标识 / 参数 74HC595N型号标识及主要参数: 74HC595N 型号标识 74HC 产品系列 595 基本型号 N 封装类型,DIP 74HC595N 主要参数 电压 2.0~6.0 V 驱动电流 +/- 7.8 mA 传输延迟 16 ns@5V 逻辑电平 CMOS

RCK= 1; _nop_(); _nop_(); RCK= 0;

}

595一般作行选,还有列选的芯片吧?一般是138.

在点阵屏 中, 74HC595 的主要作用应该为: 1、驱动,CMOS的74HC595 驱动LED点阵屏没有问题; 2、串转并,非常节约资源,从而可以降低对处理器的GPIO的需求量,一般点阵屏都需要串转 并的IC 3、具有三态输出锁存 4、多个级联,可以很方便的用于更大的LED点阵屏驱动

CPD决定动态的能耗, PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1= 输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压 [编辑本段]引脚说明

符号 引脚 描述 Q0…Q7 15, 1, 7 并行数据输出 GND 8 地 Q7’ 9 串行数据输出 MR 10 主复位(低电平) SHCP 11 移位寄存器时钟 输入 STCP 12 存储寄存器时钟输入 OE 13 输出有效(低电平) DS 14 串行数据输入 VCC 16 电源 [编辑本段]功能表

14

A

串行数据输入,数据从这个管脚移进内部的8位串 行移位寄存器

15

QA

16

VCC

锁存器输出,三态 电源正,2-6V DC

表4.1 74HC595的管脚功能描述

595貌似有很多功能的,点阵中用到的串行输入并行输出是其中的一个功能,是通过寄存器选折 的。在点阵中595用来做行的扫描,列扫描一般用译码器,74HC154或者138之类的。行扫描主 要处理字模,需要把整个字的字模都打入到595芯片,通过595来处理,通过子模各个位的移动 来实现要显示的字(该 情况用于动态的移动),静态直接就是把所有字模一次打入后直接显示

74HC595N封装信息:

类型:DIP 引脚:16 宽度:300 mil

74HC595 概述 74HC595是一款高速CMOS器件,74HC595引脚兼容低功耗肖特基TTL(LSTTL)系列。 74HC595遵循JEDEC标准no.7A。 74HC595是8阶串行移位寄存器,带有存储寄存器和三态输出。移位寄存器和存储寄存器分别采 用单独的时钟。 在SH_CP的上升沿,数据发生移位,而在ST_CP的上升沿,数据从每个寄存器中传送到存储寄 存器。如果两个时钟信号被绑定到一起,则移位寄存器将会一直领先存储寄存器一个时钟脉 冲。 移位寄存器带有一个串行输入(DS)端和一个串行标准输出(Q7')端,用于级联。74HC595还 为移位寄存器的8个阶提供了异步的复位(低有效)。存储寄存器带有8个三态总线驱动输出, 当输出使能(OE)端为低时,存储寄存器中的数据可被正常输出。 74HC595 参数 74HC595 基本参数 电压 2.0~6.0V 驱动电流 +/-7.8 mA(并行输出) 传输延迟 16 ns@5V 74HC595 其他特性 最大频率 108 MHz 逻辑电平 CMOS 功耗考量 低功耗或电池供电应用 74HC595 封装与引脚 SO16, SSOP16, DIP16, TSSOP16

产品类型:通用类电路

产品型号:74HC595

产品型号: 74HC595

产品名称: 8位带有输出锁存功能的移位寄存器

产品概述:

74HC595是一款低噪声、低功耗、高速的COMS移位寄存器,能够驱动15个LSTTL的负载。该器件包含一个8位串行输入,并行输出的移位寄存器及带有三态输出控制 的8位D型存储器。移位寄存器和存储器分别由独立的时钟提供信号。移位寄存器内置直

一下。

刚做过一个595的驱动,就是串行转并行,配合时序SCK,RCK,DATA就可以了 void shift_b595_out1(uchar *dat, uchar count) { SRCK =0; RCK =0; data_tp =dat[count]; for(i=0; i<16; i++) { switch(i) { case 3: case 4: case 5: case 8: case 9: if(data_tp&0x80) // Ensure the effecient bit is the higher 5 bits. SER_IN =1; else SER_IN =0; data_tp <<=1; SRCK =1; _nop_(); _nop_(); SRCK= 0; break; default: SER_IN =0; SRCK =1; _nop_(); _nop_(); SRCK =0; break; } } RCK= 1; _nop_(); _nop_(); RCK= 0;

● 移位时钟频率:DC-30MHz

图4.2 74HC595管脚图

74HC595逻辑图

74HC595的管脚功能描述见表4.1:

管脚号 管脚名称 管脚功能描述

1

QB

锁存器输出,三态

2

QC

锁存器输出,三态

3

QD

锁存器输出,三态

4

QE

锁存器输出,三态

5

QF

锁存器输出,三态

6

QG

锁存器输出,三态

7

QH

锁存器输出,三态

8

GND

电源地

9

SQH

串行输出,用于级联。无三态输出功能

10

Reset

低电平有效,当此管脚上出现低电平时,将复位 内部的移位寄存器,但不影响8位锁存器的值

11

Shift Clk

移位寄存器时钟输入,上升沿将把A脚上的数据 移入内部寄存器

12

Latch Clk

锁存时钟输入,上升沿将把内部移位寄存器的值 锁存起来

13

Output Enable

低电平有效,将锁存器的输出映射到输出并行口 (QA-QH)上。当输入高电平时,高阻态,同时 本芯片的串行输出无效

串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复 位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时 (为低电平),存储寄பைடு நூலகம்器的数据输出到总线。 8位串行输入/输出或 者并行输出移位寄存器,具有高阻关断状态。三态。

[编辑本段]特点 8位串行输入 /8位串行或并行输出 存储状态寄存器,三种状态 输出

描述

74HC59574HC595是硅结构的CMOS器件, 兼容低电压TTL电路,遵 守JEDEC标准。 74HC595是具有8位移位寄存器和一个存储器,三态 输出功能。 移位寄存器和存储器是分别的时钟。 数据在SHcp的上升沿 输入,在STcp的上升沿进入的存储寄存器中去。如果两个时钟连在一 起,则移位寄存器总是比存储寄存器早一个脉冲。 移位寄存器有一个

74HC595 特性 8位串行输入 8为串行或并行输出 存储寄存器带有三态输出 移位寄存器可直接清零 100 MHz(典型)移出频率 ESD保护 HBM EIA/JESD22-A114-A超过2000 V MM EIA/JESD22-A115-A超过200 V