数字逻辑综合练习

数字逻辑习题库含答案

For personal use only in study and research; not for commercialuse《数字逻辑》习题案例(计算机科学与技术专业、信息安全专业)2004年7月计算机与信息学院、计算机系统结构教研室一、选择题1.十进制数33的余3码为 。

A. 00110110B. 110110C. 01100110D. 1001002.二进制小数-0.0110的补码表示为 。

A .0.1010B .1.1001C .1.0110D .1.10103.两输入与非门输出为0时,输入应满足 。

A .两个同时为1B .两个同时为0C .两个互为相反D .两个中至少有一个为04.某4变量卡诺图中有9个“0”方格7个“1”方格,则相应的标准与或表达式中共有多少个与项 ?A . 9B .7C .16D .不能确定5. 下列逻辑函数中,与A F =相等的是 。

)(A 11⊕=A F )(B A F =2⊙1 )(C 13⋅=A F )(D 04+=A F6. 设计一个6进制的同步计数器,需要 个触发器。

)(A 3 )(B 4 )(C 5 )(D 67. 下列电路中,属于时序逻辑电路的是 。

)(A 编码器 )(B 半加器 )(C 寄存器 )(D 译码器8. 列电路中,实现逻辑功能n n Q Q =+1的是 。

)(A )(B)(C (D) 9. 的输出端可直接相连,实现线与逻辑功能。

)(A 与非门 )(B 一般TTL 门)(C 集电极开路OC 门 )(D 一般CMOS 门 10.以下代码中为无权码的为 。

A . 8421BCD 码B . 5421BCD 码C . 余三码D . 格雷码11.以下代码中为恒权码的为 。

A .8421BCD 码B . 5421BCD 码C . 余三码D . 格雷码12.一位十六进制数可以用 位二进制数来表示。

A . 1B . 2C . 4D . 1613.十进制数25用8421BCD码表示为。

数字逻辑复习题有答案

数字逻辑复习题有答案1. 什么是数字逻辑中的“与”操作?答案:在数字逻辑中,“与”操作是一种基本的逻辑运算,它只有当所有输入信号都为高电平(1)时,输出信号才为高电平(1)。

如果任何一个输入信号为低电平(0),则输出信号为低电平(0)。

2. 描述数字逻辑中的“或”操作。

答案:在数字逻辑中,“或”操作是另一种基本的逻辑运算,它只要至少有一个输入信号为高电平(1),输出信号就为高电平(1)。

只有当所有输入信号都为低电平(0)时,输出信号才为低电平(0)。

3. 如何理解数字逻辑中的“非”操作?答案:“非”操作是数字逻辑中最基本的逻辑运算之一,它将输入信号的电平状态取反。

如果输入信号为高电平(1),输出信号则为低电平(0);反之,如果输入信号为低电平(0),输出信号则为高电平(1)。

4. 解释数字逻辑中的“异或”操作。

答案:数字逻辑中的“异或”操作是一种逻辑运算,它只有在输入信号中有一个为高电平(1)而另一个为低电平(0)时,输出信号才为高电平(1)。

如果输入信号相同,即都是高电平或都是低电平,输出信号则为低电平(0)。

5. 什么是数字逻辑中的“同或”操作?答案:“同或”操作是数字逻辑中的一种逻辑运算,它只有在输入信号都为高电平(1)或都为低电平(0)时,输出信号才为高电平(1)。

如果输入信号不同,即一个为高电平一个为低电平,输出信号则为低电平(0)。

6. 什么是触发器,它在数字逻辑中的作用是什么?答案:触发器是一种具有记忆功能的数字逻辑电路,它可以存储一位二进制信息。

在数字逻辑中,触发器用于存储数据、实现计数、寄存器和移位寄存器等功能。

7. 简述D触发器的工作原理。

答案:D触发器是一种常见的触发器类型,它的输出状态由输入端D的电平决定。

当触发器的时钟信号上升沿到来时,D触发器会将输入端D的电平状态锁存到输出端Q,从而实现数据的存储和传递。

8. 什么是二进制计数器,它的功能是什么?答案:二进制计数器是一种数字逻辑电路,它能够按照二进制数的顺序进行计数。

数字逻辑综合练习上课讲义

2011数字逻辑综合练习数字逻辑综合练习一、选择题1.下列电路中属于数字电路的是( D )。

2. A. 差动放大电路 B. 集成运放电路3. C. RC振荡电路 D. 逻辑运算电路4.余3码10001000对应的2421码为( C )。

5. A. 01010101 B. 10000101C. 10111011D. 111010116.表示任意两位十进制数,需要( B )位二进制数。

7. A. 6 B. 7C. 8D. 98.n个变量可以构成( C )个最大项。

9. A. n B. 2n10.C. 2n D. 2n-111.下列触发器中,没有约束条件的是( C )。

12.A. 主从R-S触发器 B. 基本R-S触发器13.C. 主从J-K触发器 D. 以上均有约束条件14.组合逻辑电路中的险象是由于( C )引起的。

15.A. 电路未达到最简 B. 电路有多个输出16.C. 电路中的时延 D. 逻辑门类型不同17.实现同一功能的Mealy型同步时序电路比Moore型同步时序电路所需要的( B )。

18.A. 状态数目更多 B. 状态数目更少19.C. 触发器更多 D. 触发器一定更少20.用0011表示十进制数2,则此码为( D )。

21.A. 余3码 B. 5421码22.C. 余3循环码 D. 格雷码23.标准与或式是由( B )构成的逻辑表达式。

24.A. 与项相或 B. 最小项相或25.C. 最大项相与 D. 或项相与26.( B )的输出端可以直接相连,实现线与。

27.A. 一般TTL与非门 B. 集电极开路TTL与非门28.C. 一般CMOS与非门 D. 一般TTL或非门29.J-K触发器在CP时钟脉冲作用下,要使得Q(n+1) =Q n,则输入信号必定不会为( C )。

30.A. J = K = 0 B. J = Q, K =Q31.C. J = Q, K = Q D. J = Q, K = 032.设计一个五位二进制码的奇偶位发生器电路(偶校验码),需要( C )个异或门。

数字逻辑题目及其答案和解析(1)一共60道题

第一部分:1.在二进制系统中,下列哪种运算符表示逻辑与操作?A) amp;B) |C) ^D) ~解析:正确答案是 A。

在二进制系统中,amp; 表示逻辑与操作,它仅在两个位都为1时返回1。

2.在数字逻辑中,Karnaugh 地图通常用于简化哪种类型的逻辑表达式?A) 与门B) 或门C) 异或门D) 与非门解析:正确答案是B。

Karnaugh 地图通常用于简化或门的逻辑表达式,以减少门电路的复杂性。

3.一个全加器有多少个输入?A) 1B) 2C) 3D) 4解析:正确答案是 C。

一个全加器有三个输入:两个加数位和一个进位位。

4.下列哪种逻辑门可以实现 NOT 操作?A) 与门B) 或门C) 异或门D) 与非门解析:正确答案是 D。

与非门可以实现 NOT 操作,当且仅当输入为0时输出为1,输入为1时输出为0。

5.在数字逻辑中,Mux 是指什么?A) 多路复用器B) 解码器C) 编码器D) 多路分配器解析:正确答案是 A。

Mux 是指多路复用器,它可以选择输入中的一个,并将其发送到输出。

6.在二进制加法中,下列哪个条件表示进位?A) 0 + 0B) 0 + 1C) 1 + 0D) 1 + 1解析:正确答案是 D。

在二进制加法中,当两个位都为1时,会产生进位。

7.在数字逻辑中,一个 JK 触发器有多少个输入?A) 1B) 2C) 3D) 4解析:正确答案是 B。

一个 JK 触发器有两个输入:J 和 K。

8.下列哪种逻辑门具有两个输入,且输出为两个输入的逻辑与?A) 与门B) 或门C) 异或门D) 与非门解析:正确答案是 A。

与门具有两个输入,只有当两个输入都为1时,输出才为1。

9.在数字逻辑中,下列哪种元件可用于存储单个位?A) 寄存器B) 计数器C) 锁存器D) 可编程逻辑门阵列解析:正确答案是 C。

锁存器可用于存储单个位,它可以保持输入信号的状态。

10.一个带有三个输入的逻辑门,每个输入可以是0或1,一共有多少种可能的输入组合?A) 3B) 6C) 8D) 12解析:正确答案是 C。

数字逻辑试题及答案

数字逻辑试题及答案一、单项选择题(每题2分,共10分)1. 以下哪个是数字逻辑中的逻辑运算?A. 加法B. 减法C. 与运算D. 乘法答案:C2. 在数字逻辑中,一个逻辑门的输出是:A. 0B. 1C. 0或1D. 任意数字答案:C3. 以下哪个是组合逻辑电路的特点?A. 有记忆功能B. 无记忆功能C. 可以进行算术运算D. 可以进行逻辑运算答案:B4. 触发器的主要用途是:A. 逻辑运算B. 存储信息C. 放大信号D. 转换信号答案:B5. 一个4位二进制计数器可以计数到:A. 8B. 16C. 32D. 64答案:B二、多项选择题(每题3分,共15分)1. 下列哪些是数字逻辑中常用的逻辑门?A. 与门B. 或门C. 非门D. 异或门E. 与非门答案:ABCDE2. 在数字逻辑中,以下哪些可以作为信号的表示?A. 电压B. 电流C. 电阻D. 电容E. 电感答案:AB3. 以下哪些是数字电路的基本组成元素?A. 逻辑门B. 电阻C. 电容D. 触发器E. 运算放大器答案:ABD4. 在数字逻辑中,以下哪些是常见的电路类型?A. 组合逻辑电路B. 时序逻辑电路C. 模拟电路D. 混合信号电路E. 微处理器答案:ABD5. 以下哪些是数字电路设计时需要考虑的因素?A. 电路的复杂性B. 电路的功耗C. 电路的可靠性D. 电路的成本E. 电路的尺寸答案:ABCDE三、填空题(每题2分,共10分)1. 在数字逻辑中,一个逻辑门的输出状态取决于其_________。

答案:输入状态2. 一个D触发器的输出在时钟信号的_________沿触发。

答案:上升沿3. 一个4位二进制计数器的计数范围是从_________到_________。

答案:0000到11114. 一个逻辑电路的输出是其输入的_________。

答案:逻辑函数5. 在数字逻辑中,使用_________可以表示一个逻辑函数的真值表。

答案:卡诺图四、简答题(每题5分,共15分)1. 描述一个典型的组合逻辑电路的工作原理。

小学一年级综合算式练习题数字逻辑推理

小学一年级综合算式练习题数字逻辑推理

在小学一年级综合算式练习中,数字逻辑推理是一个重要的能力。

通过数字逻辑推理,学生可以培养他们的思维能力和分析能力。

下面,我们将介绍一些小学一年级综合算式练习中的数字逻辑推理题目。

1. 四个数字排列组合

请将数字1、2、3、4四个数字按照以下要求进行排列组合。

要求:

- 1不能在第一个位置;

- 2不能在最后一个位置;

- 3不能在第一个和最后一个位置;

- 4不能在第二个和倒数第二个位置。

2. 相邻数字的和

请找出下面排列中相邻数字之和最大的情况。

要求:

- 相邻数字不能是1 和9。

3. 完成算式

请根据逻辑推理,找出下面算式中缺少的数字。

要求:

4. 数字的位置

请根据提示,找出每个数字在排列中的位置。

要求:

- 数字2在第1位;

- 数字4在第3位;

- 数字3在第4位;

- 数字1在第5位。

5. 数字的排序

请根据提示,将下面数字按从小到大的顺序排列。

要求:

- 数字3在最后;

- 数字5在第一位;

- 数字1在数字5之后。

6. 数字的替换

请根据逻辑推理,找出使得下面等式成立的数字。

要求:

以上是一些小学一年级综合算式练习题中的数字逻辑推理题目。

通过这些题目,学生可以锻炼他们的思维能力和逻辑推理能力。

希望这些练习能够对学生们的数学学习有所帮助。

通过不断的练习和思考,相信他们在数字逻辑推理方面会取得进步。

数字逻辑总复习题答案

数字逻辑总复习题答案一、选择题1. 以下哪个选项是数字逻辑中的基本逻辑运算?A. 与运算B. 或运算C. 非运算D. 所有以上选项答案:D2. 在数字逻辑中,一个变量的真值表可以有多少行?A. 1B. 2C. 4D. 8答案:C3. 逻辑门电路中的输出状态取决于输入状态,以下哪个描述是正确的?A. 输出状态与输入状态相同B. 输出状态与输入状态相反C. 输出状态由输入状态的组合决定D. 输出状态与输入状态无关答案:C二、填空题1. 在数字逻辑中,逻辑或运算的符号通常表示为______。

答案:∨2. 一个三变量的逻辑函数,其真值表最多可以有______种不同的输出组合。

答案:83. 逻辑门电路中的与非门(NAND)可以看作是______和______的组合。

答案:与门,非门三、简答题1. 请简述数字逻辑中的布尔代数基本定理。

答案:布尔代数的基本定理包括交换律、结合律、分配律、幂等律、补余律等,这些定理是构建和简化逻辑表达式的基础。

2. 描述逻辑门电路中的异或(XOR)门的功能。

答案:异或门的输出仅在输入状态中奇数个为真时为真,其余情况下输出为假。

四、计算题1. 给定逻辑函数F(A, B, C) = Σ(0, 1, 2, 7),请写出其对应的真值表。

答案:| A | B | C | F ||||||| 0 | 0 | 0 | 0 || 0 | 0 | 1 | 1 || 0 | 1 | 0 | 1 || 0 | 1 | 1 | 0 || 1 | 0 | 0 | 1 || 1 | 0 | 1 | 0 || 1 | 1 | 0 | 0 || 1 | 1 | 1 | 1 |2. 利用卡诺图化简逻辑函数F(A, B, C, D) = Σ(0, 1, 2, 3, 8, 9,10, 11, 12, 13, 14, 15)。

答案:F(A, B, C, D) = A'C + BD请注意,以上内容仅为示例,实际的试题和答案应根据具体的课程内容和教学要求来制定。

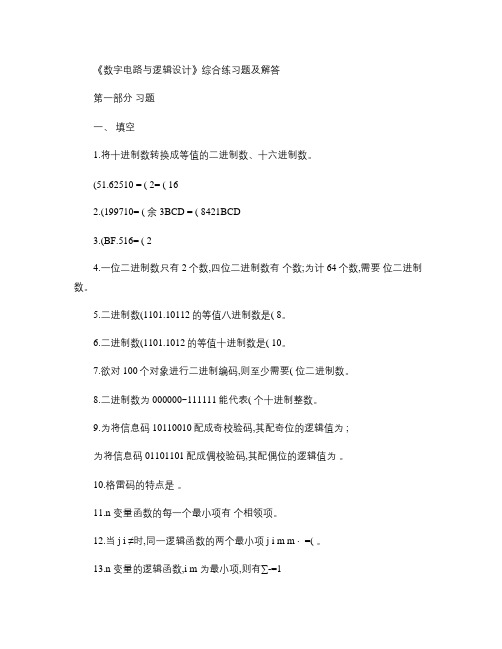

《数字电路与逻辑设计》综合练习题及解答

《数字电路与逻辑设计》综合练习题及解答第一部分习题一、填空1.将十进制数转换成等值的二进制数、十六进制数。

(51.62510 = ( 2= ( 162.(199710= ( 余3BCD = ( 8421BCD3.(BF.516= ( 24.一位二进制数只有2个数,四位二进制数有个数;为计64个数,需要位二进制数。

5.二进制数(1101.10112的等值八进制数是( 8。

6.二进制数(1101.1012的等值十进制数是( 10。

7.欲对100个对象进行二进制编码,则至少需要( 位二进制数。

8.二进制数为000000~111111能代表( 个十进制整数。

9.为将信息码10110010配成奇校验码,其配奇位的逻辑值为 ;为将信息码01101101配成偶校验码,其配偶位的逻辑值为。

10.格雷码的特点是。

11.n 变量函数的每一个最小项有个相领项。

12.当j i ≠时,同一逻辑函数的两个最小项j i m m ⋅=( 。

13.n 变量的逻辑函数,i m 为最小项,则有∑-=120n i i m =( 。

14.逻辑函数D C B A F ++=的反函数F = ( 。

15.逻辑函数(C B A F +=的对偶函数F '是 ( 。

16.多变量同或运算时, =0,则i x =0的个数必须为( 。

17.逻辑函数AB C B A F ⊕⊕=1,,(的最小项表达式为,,(C B A F =( 。

18. 逻辑函数14,12,0(10,8,4,3,2,1(,,,(∑∑Φ+=m D C B A F 的最简与或式为F =( 。

19.逻辑函数((,,(C B A C B A C B A F ++++=的最简与或式为( 。

20.巳知函数的对偶式BC D C B A D C B A F ++=',,,(,则它的原函数F =( 。

* * * * *21.正逻辑约定是( 、( 。

22.双极型三极管由截止状态过渡到饱和状态所需的过渡时间称为时间,它由时间和时间两部分组成,可用等式描述。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《数字逻辑》期末综合练习2015~2016第一学期一、单项选择1、表示任意一位十六进制数可以用( C )位二进制数来表示。

A. 1B. 2C. 4D. 162、逻辑代数中讨论的数为( D )。

A. 1B. 0C. 任意D. 0和13、常用情况下 BCD码是指( C ) 。

A.奇偶校验码B.格雷码C.8421码D.余三码4、以下代码中哪个是相邻编码只有1位二进制码不同 ( B )。

A. 8421BCD 码B. 格雷码C. 余三码D. 2421码5、以下表达式中符合逻辑运算法则的是( D )。

A. C·C=C2B.1+1=10C.0<1D.A+1=16、当逻辑函数有n个变量时,共有( B )个变量取值组合?A . nB . 2nC . n2D . 2n7、在何种输入情况下,“与非”运算的结果是逻辑0( D )。

A.全部输入是0 B.任一输入是0C.仅一输入是0D.全部输入是18、在何种输入情况下,“或非”运算的结果是逻辑1( D )。

A.任一输入为1 B.全部输入是1C.任一输入为0,其他输入为1D. 全部输入是09、在余3码编码中不允许出现的代码是( A )。

A、0000~0010和1101~1111B、0101~1010C、0011~1001D、无10、对于有3个逻辑变量的逻辑函数,它所对应的卡诺图小方格有( D )个。

A . 3B . 6C . 7D . 811、为了书写方便,逻辑函数的最小项可用( B )表示。

A . nB . mC .MD . N12、为了书写方便,逻辑函数的最大项可用( C )表示。

A . nB . mC .MD . N13、十进制6的格雷码是( C )A . 110B . 100C .101D . 01114、有一个三个变量X,Y,Z的逻辑函数,下列哪个是最小项( A )A . XYZB . XYXC .YZXD . XYZ15、组合逻辑电路的特征是( A )。

A . 输出与输入有关B . 输出与输入无关C .电路有记忆功能D . 以上都不是16、下列逻辑表达式是与或表达式( B )。

A . A(B+C)B . A+BC C .(AC+B)D D . 都不是17、在数字逻辑中下列表达式哪个是错误的( C )。

A.0=0 B.1=1 C.1>0 D.都不对18、图中所示逻辑电路图输出为“0”时,输入变量ABCD取值组合为( B )。

A.1101 B.0101 C.0111 D.101119-1、时序逻辑电路的一般由组合逻辑电路与( C )组成。

A.全加器B.译码器 C.触发器D.选择器19-2、5变量卡诺图中的卡诺圈包含的1方格的个数可能是( D )。

A.12 B.5 C.24 D.120、同步RS触发器接收信号是( A )。

A .CP=1B .CP ↑C .CP ↓D 任意值 21、若输入变量A 、B 全为0时,输出F=1,则其输入与输出的关系是( A )。

A .F=A⊙B B.B A F ⊕=C .F=A+BD .F=AB 22、时序电路中同步RS 触发器的特性表是( D )。

A .讨论输入R ,S 和输出Q 的关系 B .讨论输入R ,S 和输出Q n的关系C .讨论输入R ,S 和输出Q n+1的关系D .讨论输入R ,S ,Q n 和输出Q n+1的关系23、下列各组变量取值中,能使函数(,,,)(0,1,2,5,6,13)F A B C D m =∑的值为1的是( D )。

A .1100B .1110C . 0100D .0110 24、在74LS138译码器中输入端是3位,输出端为( C )位。

A .3 B .6 C .8 D .925、时序逻辑电路和组合逻辑电路比较,其差异在于( B )。

A .是否由基本门电路组成 B .是否具有记忆功能 C .是否有多个输入和多个输出 D .是否单个芯片的集成度更高26、常用芯片74LS32的引脚“7”是 ( D )。

A .输入 B .输出 C .电源 D .地 27、常用芯片74LS00是 ( C )门A .与门B .或门C .与非门D .或非门 28、常用芯片74LS138是( B )A .加法器B .译码器C .计数器D .都不是二、判断题(你认为下列命题是正确的,就在其题号的括号中加“√”,错误的加“×”)1、计算机中机器码表示中的“0”和“1”都是表示大小。

( × )2、数字电路中的“0”和“1”也是表示大小。

(×)3、因为逻辑表达式BABAA+=+成立,所以1=A成立。

(×)4、逻辑函数的标准与或表达式就是最小项表达式。

(√)5、卡诺图都是唯一的一个逻辑化简的工具。

()6、(12)10的余3码是(10101)2()7、逻辑函数F=A+B的反函数是BAF⋅=()8、逻辑函数F=A+B的对偶函数是BAF⋅='()9、对于逻辑函数的表示方式中,逻辑表达式、真值表、卡诺图和逻辑电路图都不是唯一的。

()10、组合逻辑电路没有反馈电路。

()11、触发器是存储电路。

()12、4个逻辑变量有16个最小项。

()13、(CF)16=(11011111)2。

()14、在卡诺图上,相邻的6个标1的最小项,可以合并为一项,并消去2个变量。

()15、逻辑函数对应的真值表是唯一的。

()16、JK触发器的输入信号J、K之间存在约束。

()17、余3码的1000代表十进制的5。

()18、A、B、C变量的一个最大项M2=A B C++。

()19、译码器有记忆功能。

()20、设M5和M6为函数F的两个最大项,对于任意输入组合,M5·M6=0。

()三、填空题1、在计算机中,常用的计数制除十进制外,还有________ 、________ 、________ 。

2、常用BCD码有___________ 、___________ 、____________任意列出3项。

3、(100)10=(___________)2=(________)8=(_______)16。

4、(123)10=(__________________)8421=(__________________)24215、(123)10=(__________________)格雷6、组成组合逻辑电路的基本门电路有________ 、________ 、________ 。

7、逻辑代数的反演规则是_____________ 、______________ 、______________。

8、逻辑代数的对偶规则是___________________ 、________________________、_________________________。

9、RS、JK、D和T四种触发器中,唯有__ __触发器对输入信号有约束。

10、组合逻辑电路中的真值表的构成是_______________________。

11、D触发器的特性方程是____________________________。

12、(010*********)8421BCD =(________________________)10。

13、使4变量A、B、C、D对应的最小项m14的二进制数是(___________)2。

14、4个变量的卡诺图中,任意一个方格都与其它的_____________个方格相邻。

15、“或”门的一个多余输入端接__________电平,将不影响门电路的逻辑功能。

16、“与”门的一个输入端接________电平,会使该门的其它输入不能改变“与”门的输出。

17、相同编号的最大项与最小项的关系是____________。

18、逻辑代数三个重要的规则是 _____________、反演规则、对偶规则。

19、组合逻辑电路的输入只和___________有关,信号_________传输。

20、时序电路中的触发器输出特点是_____________________________。

21、组合逻辑电路分析的步骤有____________________________、___________________、________________、________________。

22、时序逻辑电路的特点是_________________________________、_________________________________。

23、同步RS触发器的次态方程是________________,方程在_________ 有效。

24、主从JK触发器的次态方程是_________________,方程在_________ 有效。

25、维持阻塞D触发器的次态方程是_______________,方程在________ 有效。

四、计算题1、已知Y (A,B,C )=∏M (1,2,4)求最小项表达式。

2、求逻辑函数))((E D C C A AB F+++=的对偶函数。

3、求逻辑函数BC DE C A F++=)(的反函数。

4、用卡诺图法将F(A,B,C)=A B +(A+B)C 化简成或与式。

五、逻辑化简、证明(要求写出步骤及引用的公式) 1、代数法化简、证明(1)AB BCD B A F ++=(2)CD D AC ABC C A F +++=(3)求证:1=⋅+⋅++B A B A B A AB(4)求证D B B AD C B D D BC +=++++))((2、分别求下列逻辑函数的最小项和最大项表达式。

(1)BC C A B A C B A F +⋅+=),,((2)))((),,,(CD B D C A D C B A F +⋅+=3、用卡诺图化简下列逻辑函数,写出最简与或表达式。

(1)C B A B A C B A F )(),,(++⋅= (2)∑=)7,6,5,3,1(),,(m C B A F (3)∑∏+=)4,0()5,3,1(),,(d M C B A F (4))15,13,11,10,7,6,5,2,1,0(),,,(∑=m D C B A F 六、分析题1、分析下列逻辑电路图的逻辑功能。

(1)(2)(3)已知同步同步D触发器和维持D触发器的CP及输入波形如下图所示,请分别绘制出输出波形,初始值为均0。

(4)已经知道如图所示触发器和输入信号,写出触发器的特性方程,绘制出输出波形。

触发器的初始值为0(5)、根据给出的CP和A,作出如下电路的输出波形。

(设触发器的初始值为0)(6)已知JK触发器的CP及输入波形如下两图所示,请分别绘制出同步JKFF 和主从JKFF的输出波形,初始值为均0(7)已知如图的T’触发器的CP及输入波形如下图所示,请绘制出输出波形,初始值为均0。