北京邮电大学 数字逻辑期末模拟试题3

院校资料-北京邮电大学 数字逻辑期末模拟试题1 -2

北京邮电大学数字逻辑期末模拟试题1 -2本科试题(一)一、选择题(每小题2分,共20分。

)1.,A 、B 、C 取何值时,F =1()。

A.011B.100C.101D.000 2.下列三个数对应的十进制数最大的是()。

A. (30)8B. (10110)2C. (00101000)8421D.27 3.图1所示电路中描述错误的是()。

A .状态变化发生在CP 脉冲下降沿B .C .D.CP 脉冲下降沿输出状态翻转4.二进制加法器自身()。

A .只能做二进制数加运算B .只能做8421BCD 码加运算C .A 和B 均可D. 只能做补码加法运算5.用方程式表示时序电路的逻辑功能,需()。

A .一个方程B .二个方程C .三个方程D. 四个方程6.五个D 触发器构成的扭环计数器,计数器的模是()。

A .10B .25C .5D .25 7.八路数据选择器如图2所示,该电路所实现的逻辑函数是()。

A. B.C. D. 8.判断以下三组VHDL 语言描述中()意义相同。

A. z <= not X and not Y ;和z <= not (X or Y);B. z <= not (X or Y);和z <= not X or not Y ;C. z <= not X and Y ;和z <= not (X and Y);D. z <= not X and not Y ;和z <= not (X and Y);9. 多路选择器构成的数据总线是()。

A. 双向的B. 单向的C. A 和B 都对D.多路的10.断电之后,能够将存储内容保存下来的存储器是()。

A .只读存储器ROM ;B .随机存取存储器RAM ;C .动态存取存储器DRAM D. SDRAM二、简答题(每小题5分,共15分)1、化简(5分)2、分析如图3所示的逻辑电路图,写出输出逻辑函数表达式。

(5分)。

3、画出01011序列检测器的状态转移图,X 为序列输入,Z 为检测输出。

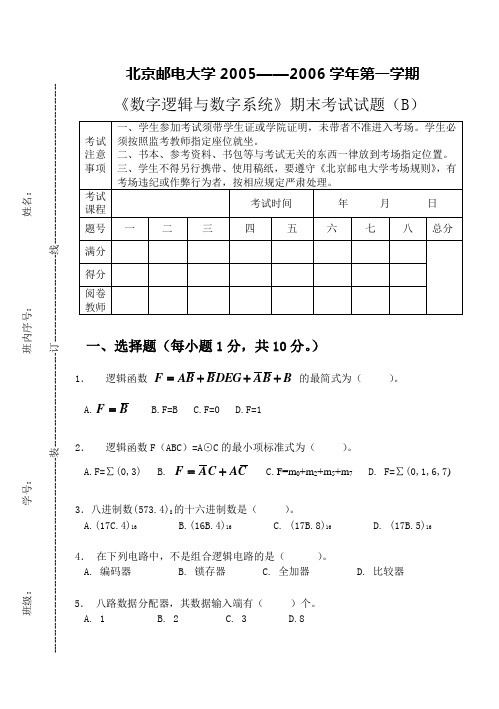

05—06学年《数字逻辑与数字系统》期末考试试题

北京邮电大学2005——2006学年第一学期 《数字逻辑与数字系统》期末考试试题(B )一、选择题(每小题1分,共10分。

) . 逻辑函数 B B A DEG B B A F +++= 的最简式为( )。

A.B F = B.F=B C.F=0 D.F=1 . 逻辑函数F (ABC )=A ⊙C 的最小项标准式为( )。

A.F=∑(0,3) B. C A C A F += C.F=m 0+m 2+m 5+m 7 D. F=∑(0,1,6,7) .八进制数(573.4)8的十六进制数是( )。

A.(17C.4)16 B.(16B.4)16 C. (17B.8)16 D. (17B.5)16 . 在下列电路中,不是组合逻辑电路的是( )。

A. 编码器 B. 锁存器 C. 全加器 D. 比较器 . 八路数据分配器,其数据输入端有( )个。

A. 1 B. 2 C. 3 D.86.n 个触发器构成的扭环计数器中,无效状态有( )个。

A.nB.2nC.2n-1D. 2n -2n7.构成数字系统必不可少的逻辑执行部件为( )。

A. 控制器B. 计数器C. 基本子系统D. 逻辑门8.电路如图1所示,其中完成A Q Q n 1n +=+电路是( )。

9. 使用256×4位EPROM 芯片构成2K ×32位存储器,共需EPROM 芯片( )片。

A.64B.32C.48D.1610.在ispLSI1032中,巨块是( )。

A.逻辑宏单元B.输出布线C.时钟设置网络D.GLB 及其对应的ORP ,IOC 等的总称二、填空题(每小题2分,共20分)1. 用卡诺图判断函数AC BC AB F ++=和C A C B B A G ++=之间的逻辑关系是______________________。

2. 一个逻辑函数如果有n 个变量,则有__________个最小项。

任何一个逻辑函数可以化成一组________________之和表达式。

数电期末考试题及答案

数电期末考试题及答案一、单项选择题(每题2分,共20分)1. 在数字电路中,最基本的逻辑运算是()。

A. 与运算B. 或运算C. 非运算D. 异或运算答案:C2. 一个触发器可以存储()位二进制信息。

A. 1B. 2C. 3D. 4答案:A3. 以下哪个不是组合逻辑电路的特点?()A. 输出只依赖于当前输入B. 输出与输入之间存在时延C. 没有记忆功能D. 任何时刻输出仅由该时刻的输入决定答案:B4. 一个4位二进制计数器可以计数到()。

A. 8B. 16C. 15D. 14答案:B5. 一个D触发器的特点是()。

A. 有两个稳定状态B. 只有一个稳定状态C. 没有稳定状态D. 以上都不是答案:A6. 在数字电路中,以下哪个不是基本的门电路?()。

A. 与门B. 或门C. 非门D. 异或门答案:D7. 一个3线-8线译码器可以译码()种不同的输入。

A. 3B. 8C. 6D. 7答案:B8. 一个8位寄存器可以存储()位二进制数。

A. 8B. 16C. 32D. 64答案:A9. 以下哪个是同步时序电路的特点?()A. 电路的输出仅依赖于当前的输入B. 电路的输出依赖于当前的输入和电路的历史状态C. 电路的输出不依赖于输入D. 电路的输出仅依赖于电路的历史状态答案:B10. 一个JK触发器可以表示()种不同的状态。

A. 1B. 2C. 3D. 4答案:B二、填空题(每题2分,共20分)1. 在数字电路中,一个基本的与门电路有_____个输入端和一个输出端。

答案:22. 一个4位二进制计数器的计数范围是从0到_____。

答案:153. 一个D触发器在时钟信号的上升沿到来时,其输出Q将与输入D保持_____。

答案:一致4. 在数字电路中,一个3线-8线译码器的输出是_____进制的。

答案:二5. 一个8位寄存器可以存储的最大十进制数是_____。

答案:2556. 一个JK触发器在J=0,K=0时,其状态将保持_____。

北京邮电大学数字逻辑期末模拟试题3

本科试题(三)一、选择题(每小题2分,共20分。

)1.与最小项表达式F(A,B,C)=m 0+m 3+m 4+m 7相等的逻辑函数为(相等的逻辑函数为()。

A.F =B F=B ⊙C B. C. D.F=∑(0,4) 2.证明成立的最简单方法是依据以下哪种定律或规则?(或规则?( ) A. 对偶规则对偶规则 B. B. 分配律分配律 C. C.反演规则D.D.多余项定律多余项定律多余项定律3.2421BCD 码为(码为(101111111011111110111111))2421BCD ,与其相等的十进制数是(,与其相等的十进制数是( )。

A.(277)10 B.(82)10 C. (59)10 D. (1115)10 4. 一个四输入端与非门,使其输出为0的输入变量取值组合有(的输入变量取值组合有( )种。

)种。

A. 15B. 8C. 7D. 1 5. ( )电路在任何时刻只能有一个输入端有效。

)电路在任何时刻只能有一个输入端有效。

A.A.普通二进制编码器普通二进制编码器普通二进制编码器 B. B.优先编码器优先编码器 C. C.七段显示译码器七段显示译码器 D. D. 二进制译码器二进制译码器6.中规模集成计数器都具有规定的模值,但可以用(.中规模集成计数器都具有规定的模值,但可以用( )来构成任意进制计数。

)来构成任意进制计数。

A.A.复复0和复9 B.置数法和复位法置数法和复位法 C. C.改变输入法改变输入法 D. D. 控制CP 脉冲脉冲 7.数字系统级的设计与逻辑部件级设计分别采用(.数字系统级的设计与逻辑部件级设计分别采用( )的设计方法。

)的设计方法。

A. 自上而下、自上而下自上而下、自上而下 B. B. 自下而上、自下而上自下而上、自下而上 C. 自上而下、自下而上自上而下、自下而上 D. D. 自下而上、自上而下自下而上、自上而下8.使用ROM 和PLA 实现组合逻辑时,要将逻辑表达式分别写成(实现组合逻辑时,要将逻辑表达式分别写成( )。

北京邮电大学网络教育《数字通信原理》期末考试大题汇总

第1章1.数字信号和模拟信号的区别是什么?答:数字信号和模拟信号的区别在于表征信号的参量〔例如幅值〕是否离散。

2.什么是多进制数字信号?答:假设信号幅度取值可能有多种〔例如4或8种〕,这种数字信号叫多进制数字信号。

4.数字通信占用的带宽比模拟通信大,能举例吗?答:一路模拟所占频带仅4kHz,而一路数字的频带为64kHz,而后者是前者的16倍。

5.为什么使用分贝表示两功率之比?答:主要有如下两个原因:①读写、计算方便。

如多级放大器的总放大倍数为各级放大倍数相乘,用分贝可改用相加。

②能如实地反映人对声音的感觉。

实践证明,声音的分贝数增加或减少一倍,人耳听觉响度也提高或降低一倍。

即人耳听觉与声音功率分贝数成正比。

例如蚊子叫声与大炮响声相差100万倍,但人的感觉仅有60倍的差异,恰好分贝。

第2章1.什么是语音信号编码?答:模拟语音信号数字化称为语音信号编码〔简称语音编码〕。

同理,图像信号的数字化称为图像编码。

2.PAM信号是模拟信号还是数字信号?答:我们要考察受调参量的变化是否离散。

PAM调制的受调参量是脉冲的幅度,而调制后PAM信号在幅度上仍然是连续的,所以PAM信号是模拟信号。

3.产生折叠噪声的原因是什么?答::如果抽样频率选得不适宜,以低通型信号为例,假设,那么会产生折叠噪声。

4.对于话音通信产生折叠噪声的后果是什么?答:有折叠噪声就意味着一次下边带与原始频带重叠,造成的后果是收端无法用低通滤波器准确地恢复原模拟话音信号。

5.为了产生折叠噪声,抽样频率是不是越高越好?答:抽样频率不是越高越好,太高时会增加占用的带宽,使信道利用率降低。

6.PCM通信系统中发端低通的作用是什么?答:发端低通的作用是予滤波,即防止高于3.4KHz的信号通过,防止PAM信号产生折叠噪声。

7.PCM通信系统中收端低通的作用是什么?答:收端低通的作用是恢复〔或重建〕原模拟信号。

8.为了提高小信号的量化信噪比,仍然采用均匀量化行不行?答:不行。

北京邮电大学网络教育《数字通信原理》期末考试(小抄版)

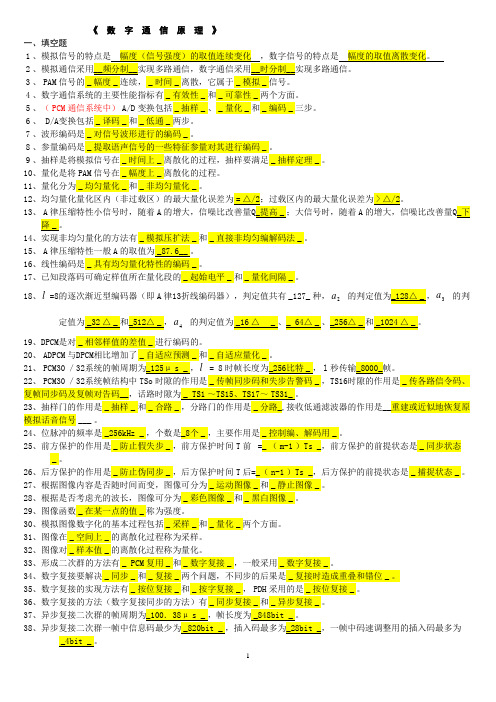

《数字通信原理》一、填空题1、模拟信号的特点是幅度(信号强度)的取值连续变化,数字信号的特点是2、模拟通信采用__频分制__实现多路通信,数字通信采用__时分制__实现多路通信。

3、PAM信号的_幅度_连续,_时间_离散,它属于_模拟_信号。

4、数字通信系统的主要性能指标有_有效性_和_可靠性_两个方面。

5、(PCM通信系统中)A/D变换包括_抽样_、_量化_和_编码_三步。

6、 D/A变换包括_译码_和_低通_两步。

7、波形编码是_对信号波形进行的编码_。

8、参量编码是_提取语声信号的一些特征参量对其进行编码_。

9、抽样是将模拟信号在_时间上_离散化的过程,抽样要满足_抽样定理_。

10、量化是将PAM信号在_幅度上_离散化的过程。

11、量化分为_均匀量化_和_非均匀量化_。

12、均匀量化量化区内(非过载区)的最大量化误差为=△/2;过载区内的最大量化误差为13、A律压缩特性小信号时,随着A的增大,信噪比改善量Q_提高_;大信号时,随着A的增大,信噪比改善量14、实现非均匀量化的方法有_模拟压扩法_和_直接非均匀编解码法_。

15、A律压缩特性一般A的取值为_87.6__。

16、线性编码是_具有均匀量化特性的编码_。

17、已知段落码可确定样值所在量化段的_起始电平_和_量化间隔_。

18、l=8的逐次渐近型编码器(即A律13折线编码器),判定值共有_127_种,2a3a的判a419、DPCM是对_相邻样值的差值_进行编码的。

20、ADPCM与DPCM相比增加了_自适应预测_和_自适应量化_。

21、PCM30/32系统的帧周期为_125μs _,l= 8时帧长度为_256比特_,l秒传输_8000_帧。

22、PCM30/32系统帧结构中TSo时隙的作用是_传帧同步码和失步告警码_,TS16时隙的作用是_传各路信令码、复帧同步码及复帧对告码__,话路时隙为_ TS1~TS15、TS17~TS31_。

23、抽样门的作用是_抽样_和_合路_,分路门的作用是_分路_,接收低通滤波器的作用是__重建或近似地恢复原模拟话音信号___。

(完整word版)数字逻辑期末考试题

数字逻辑考试题数字逻辑考试题(一)一、填空(共17分,每空1分)1。

(1011。

11)B =( ) D =( )H 2. (16)D =( )8421BCD 码。

3。

三态门的输出有 、 、 三种状态。

6。

ABC C B A C AB C B A Y ++=),,( 的最简式为Y= 。

7. 由n 位寄存器组成的扭环型移位寄存器可以构成 进制计数器。

10. 四位环型计数器初始状态是1000,经过5个时钟后状态为 。

11. 在RS 、JK 、T 和D 触发器中, 触发器的逻辑功能最多。

12。

设一个包围圈所包围的方格数目为S ,消去的变量数目为N ,那么S 与N 的关系式应是 。

13. 在卡诺图化简逻辑函数时,圈1求得 的最简与或式,圈0求得 的最简与或式。

二、选择(共10分,每题1分)1。

DE BC A Y +=的反函数为Y =( )。

A 。

E D CB A Y +++⋅= B 。

E DC B A Y +++⋅=C 。

)(ED C B A Y +++⋅= D 。

)(E D C B A Y +++⋅= 3. 十进制数25用8421BCD 码表示为( )。

A 。

10101B 。

0010 0101C 。

100101 D. 101014。

若用1表示高电平,0表示低电平,则是( )。

A 。

正逻辑B 。

负逻辑C 。

正、负逻辑 D. 任意逻辑 5. 下逻辑图的逻辑表达式为( ).A. AC BC AB Y = B 。

BC AC AB Y ++= C. BC AC AB Y ++= D. BC AC AB Y = 6. 三态门的逻辑值正确是指它有( )。

A. 1个B. 2个C 。

3个D. 4个 9。

组合逻辑电路在电路结构上的特点下列不正确的是( )。

A 。

在结构上只能由各种门电路组成B. 电路中不包含记忆(存储)元件C. 有输入到输出的通路 D 。

有输出到输入的反馈回路10. 已知74LS138译码器的输入三个使能端(E 1=1,022==B A E E )时,地址码A 2A 1A 0=011,则输出07~Y Y 为( ).A. 11111101B 。

数字电路与逻辑设计期末模拟题及答案

数字电路与逻辑设计期末模拟题一、 选择题1、(36.7)10 的8421BCD 码为。

() A 、(0110110.101)8421BCD B 、(0011110.1110)8421BCD C 、(00110110.0111)8421BCD D 、(110110.111)8421BCD2、与(6B.2)16相对应的二进制数为() A 、(1101011.001)2 B 、(01101010.01)2 C (11101011.01)2 D 、(01100111.01)23、在BCD 码中,属于有权码的编码是()A 、余3码B 、循环码C 、格雷码D 、8421码 4、如图1-1所示门电路,按正逻辑体制,电路实现的逻辑式F=()5、如果1-2所示的波形图,其表示的逻辑关系是()6、下列器件中,属于组合电路的有()A 、计数器和全加器B 、寄存器和比较器C 、全加器和比较器D 、计数器和寄存器7、异或门F=A ⊕B 两输入端A 、B 中,A=0,则输出端F 为() A 、A ⊕B B 、B C 、B D 、08、已知4个组合电路的输出F1~F4的函数式非别为:F 1=AB+A C ,F 2=AB+A CD+BC ,F 3=A B +B C ,F 4=(A+B )·(A +C ),则不会产生竞争冒险的电路是( ) A 、电路1 B 、电路2 C 、电路3 D 、电路4 9、边沿触发JK 触发器的特征方程是() A 、θ1+n =Jn θ+k n θ B 、θ1+n =J n θ+k n θC 、θ1+n =J nθ+k nθ D 、θ1+n =J n θ+K nθA 、CB A •• B 、C B A •• C 、A+B+CD 、C B A ++A 、F=A ·B B 、F=A+BC 、F=B A ⋅D 、F=B A +A 、nB 、2nC 、n 2D 、2n11、(011001010010.00010110)8421BCD 所对应的十进制数为() A 、(652.16)10 B 、(1618.13)10 C 、(652.13)10 D 、(1618.06)1012、八进制数(321)8对应的二进制数为() A 、(011010001)2 B 、(110011)2 C 、(10110111)2 D 、(1101011)213、与(19)10相对应的余3BCD 码是() A 、(00101100)余3BCD B 、(01001100)余3BCDC 、(00110101)余3BCD D 、(01011010)余3BCD 14、如图1-3所示门电路,按正逻辑体制,电路实现的逻辑关系F=() A 、C B A ⋅⋅ B 、C B A ⋅⋅ C 、A+B+C D 、C B A ++图1-315、如图1-4所示的波形图表示的逻辑关系是() A 、F=B A ⋅ B 、F=A+B C 、F=B A ⋅ D 、F=B A +16、已知逻辑函数的卡诺图如图1-5所示能实现这一函数功能的电路是()17、组合逻辑电路的特点是()C 、电路输出与以前状态有关D 、全部由门电路构成18、函数F=C B AB C A ⋅++,当变量取值为(),不会出现冒险现象。

《数字逻辑与数字系统》期末考试试题

--北京 XX 大学 2006 —— 2007-学年第一学期------A )-《数字逻辑与数字系统》期末考试试题(- -----一、学生参加考试须带学生证或学院证明,未带者不准进入考场。

学生必---- 考试 须按照监考教师指定座位就坐。

-- -- 注意二、书本、参考资料、书包等与考试无关的东西一律放到考场指定位置。

--- 事项 三、学生不得另行携带、使用稿纸,要遵守《北京邮电大学考场规则》,有- :---考场违纪或作弊行为者,按相应规定严肃处理。

名--:- 考试姓-名 -数字逻辑与数字系统考试时间2007 年 1 月 26日-- 课程姓---- 题号一二三四五六七八总分--线----线满分1020101010121414----- 得分----: -- 阅卷号-- 教师:-序-- 号 -内--序-班-订内-班- 一、选择题(每小题 1 分,共 10 分。

)订 ----- --AB- 1.卡诺图如图 1 所示,电路描述的逻辑表达式F=()。

00011110CD---001- A.∑ m(1,2,4,5,9,10,13,15)--- 011111-- B.∑ m(0,1,3,4,5,9,13,15)-111-- C.∑ m(1,2,3,4,5,8,9,14)--1011--装- D.∑ m(1,4,5,8,9,10,13,15)图 1--装-: --- 2.在下列逻辑部件中,不属于组合逻辑部件的是()。

号--: - A. 译码器B.锁存器C.编码器D. 比较器学-号--学----- 3.八路数据选择器,其地址输入端(选择控制端)有()个。

---- A. 8B. 2C. 3D. 4------ 4.将 D 触发器转换为 T 触发器,图 2 所示电路的虚框Q Q-- :-- 内应是()。

D-级--: -班 - A. 或非门B.与非门-级-CP-班- C. 异或门D.同或门-T--图 2-----5.用 n 个触发器构成计数器,可得到的最大计数模是()。

北京邮电大学数据结构期末考试试题

北京邮电大学数据结构期末考试试题(A卷)一.单项选择题(2分/题)1.一个栈的输入序列为12345,则下列序列中是栈的输出序列的是(A)。

A.23415B.54132C.31245D.142532.设循环队列中数组的下标范围是1~n,其头尾指针分别为f和r,则其元素个数为(D)。

A.r-fB.r-f+1C.(r-f) mod n +1D.(r-f+n) mod n3.二叉树在线索化后,仍不能有效求解的问题是(D)。

A.先序线索二叉树中求先序后继B. 中序线索二叉树中求中序后继 C.中序线索二叉树中求中序前驱 D. 后序线索二叉树中求后序后继4.求最短路径的FLOYD算法的时间复杂度为(D)。

A.O(n)B.O(n+e)C.O(n2)D.O(n3)5.一棵左右子树不空的二叉树在先序线索化后,其空指针域数为(B)。

A.0B.1C.2D.不确定6.数组A[1..5,1..6]的每个元素占5个单元,将其按行优先顺序存储在起始地址为1000的连续的内存单元中,则元素A[5,5]的地址为(A)。

A.1140B.1145C.1120D.11257.在下列排序算法中,在待排序的数据表已经为有序时,花费时间反而最多的是(A)。

A.快速排序B.希尔排序C.冒泡排序 D.堆排序8.对有18个元素的有序表做折半查找,则查找A[3]的比较序列的下标依次为(C)。

A.1-2-3B.9-5-2-3C.9-5-3D. 9-4-2-39.下列排序算法中,某一趟结束后未必能选出一个元素放在其最终位置上的是(D)。

A.堆排序B.冒泡排序C.快速排序 D.直接插入排序10.在平衡二叉树中插入一个结点后造成了不平衡,设最低的不平衡点为A,并已知A的左孩子的平衡因子为-1,右孩子的平衡因子为0,则做(B)型调整以使其平衡。

A.LLB.LRC.RLD.RR二.判断题(1分/题)1.线性表的长度是线性表所占用的存储空间的大小。

F2.双循环链表中,任意一结点的后继指针均指向其逻辑后继。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

五、时序电路设计(12 分)

西 010 北 011 +: 100 -: 101 南 001 东 000 用 D 触发器设计同步五进制计数器。已知状态转换过程的编码是 110→011→100→001 图7 →101→110。 1、列出状态转移表。 2、写出状态方程。 3、写出激励方程。 4、画出逻辑电路图。 5、画出允许自启动的状态转移图。

三、时序电路分析题(10 分)

试分析如图所示电路的功能 (1)写出电路的输出函数、激励函数、状态方程。

(2)写出状态表、画出状态图。 (3)写出电路的功能。

0

1

2

Z

四、组合电路设计(10 分)

设计一个如图 7 所示六段显示的驱动译码器。它是为了显示图 7 所示的六个符号中的 一个,实线表示亮,虚线表示不亮(图中 e 是垂直线,f 是水平线) 。设计的器件有三个输 入 A、B、C 及六个输出 a、b、c、d、e、f。图中表示的三位数是输入码,即译码器接收三 位码,使适当的段亮。每一段的驱动电位是高电平。没有给出的码作为无关项。 1、列真值表。 2、求最简逻辑表达式。 (卡诺图) b a 3、画出实现的驱动 d 段和 f 段的电路图。可以用与非门和异或门。 f d e c

D. 二进制译码器

6.中规模集成计数器都具有规定的模值,但可以用( )来构成任意进制计数。 A.复 0 和复 9 B.置数法和复位法 C.改变输入法 D. 控制 CP 脉冲 7.数字系统级的设计与逻辑部件级设计分别采用( )的设计方法。 A. 自上而下、自上而下 B. 自下而上、自下而上 C. 自上而下、自下而上 D. 自下而上、自上而下 8.使用 ROM 和 PLA 实现组合逻辑时,要将逻辑表达式分别写成( ) 。 A. 最小项之和、最小项之和 B. 最简与-或式、最简与-或式 C. 最简与-或式、最小项之和 D. 最小项之和、最简与-或式 9. 下列时序电路状态转移表中,具有自启动功能的是( A. 表 1

六、硬件描述语言设计(14 分)

采用 VHDL 语言设计一个时序状态机如图所示。

七、小型控制器设计(14 分)

图 9 所示为数字累加系统的数据通路图, 设计定序型控制器。 寄存器 A 从数据总线上接 收一系列输入数据,寄存器 B 保存它们的累加结果,加法器完成求和运算,控制器指挥执行 部件自动完成上述运算。其中 LDA,LDB 为打入寄存器的控制信号,ADD 为三态门使能信号。 假设累加系统启动之前寄存器 A、B 已清零。控制器的状态变化发生在 T1 节拍脉冲时间,打 入寄存器操作发生在 T2 节拍脉冲时间,控制器状态周期为 T=T1+T2。 1、画出控制器的 ASM 图。 2、列出状态转移真值表。 数据输入 3、写出激励方程和控制信号表达式。 LDA 4、画出定序型控制器电路图。

本科试题(三)

一、选择题(每小题 2 分,共 20 分。 )

1.与最小项表达式 F(A,B,C)=m0+m3+m4+m7 相等的逻辑函数为( A. ) 。

F=B⊙C

B. F AB C AB C

C. F B C B C

D.F=∑(0,4)

2.证明 F A( BC B C ) A( BC B C ) A 成立的最简单方法是依据以下哪种定律 或规则?( ) A. 对偶规则 B. 分配律 C.反演规则 D.多余项定律 3.2421BCD 码为(10111111)2421BCD,与其相等的十进制数是( ) 。 A.(277)10 B.(82)10 C. (59)10 D. (1115)10 4. 一个四输入端与非门,使其输出为 0 的输入变量取值组合有( A. 15 B. 8 C. 7 D. 1 5. ( )电路在任何时刻只能有一个输入端有效。 A.普通二进制编码器 B.优先编码器 C.七段显示译码器 )种。

NS Q1 0 1 1 1 0 Q3 0 0 1 1 0 Q2 0 1 1 0 0 Q1 1 1 1 0 0

1 1 116K 1×80的 RAM 0 1 10. 寻址容量为 需要

1根地址线。 1 0 0 (

A.14

1

0

0

B.16

0

0

0

C.18

1Байду номын сангаас

D.20

0

0

0

0

二、简答题(各 5 分,共 10 分)

1、简单描述 VHDL 语言程序基本结构所包含的五个部分。 (5 分) 2、 简单描述 SRAM 和 DRAM 存储元的存储机理。 (5 分)

PS Q3 0 0 0 Q2 1 0 1 Q1 0 1 1 Q3 0 0 1 NS Q2 0 1 1 Q1 1 1 1 Q3 0 0 0 PS Q2 1 0 1 1 0 Q1 0 1 1 Q3 0 0 1

) 。 C. 表 3

B. 表 2

NS Q2 0 1 1 Q1 1 1 1 Q3 0 0 0 1 ) 1 PS Q2 1 0 1 1 0

寄存器 A

控 制 器 ADD LDB 图9

加 法 器 寄存器 B