数字逻辑模拟试题

数字逻辑与逻辑设计模拟卷及答案

《数字电路与逻辑设计》模拟卷(考试时间 120分钟)姓名 学号 班级一.填空题(每空2分,共20分)1.(A2.C)16=( )102.(110001000001)2421码=( )103.已知[X]反=1.1010,那么[X]真值=( )。

4.)13,11,10,5,1()15,14,9,8,6,2,0(),,,(d D C B A F ∑∑+=,其最简与或式=F ( )。

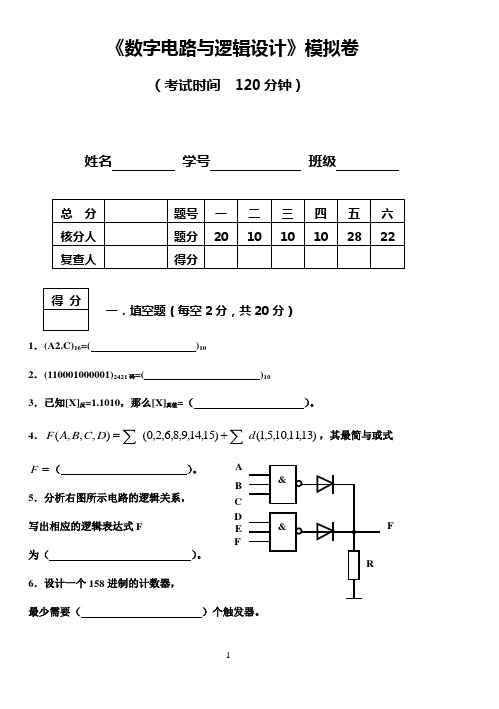

5.分析右图所示电路的逻辑关系, 写出相应的逻辑表达式F为()。

6.设计一个158进制的计数器,最少需要( )个触发器。

7.当用D 触发器实现T ’触发器功能时,则D 端应接( )端。

8.模为2n 的扭环形计数器,其无用状态数为( )。

A B CD E FF9.如下图所示逻辑部件,其中各方框中采用模N 的计数器作N 次分频器,则Z 输出的频率是( )。

10.时序逻辑电路使用时钟脉冲CP 上升沿更新状态的边沿触发器,已知CP 及输入X 的波形如下图所示,则X 的取值(从左向右)是( )。

二.单项选择题(每小题1分,共10分)1.与二进制0101等值的余3码是( )。

(1)1010 (2)1000 (3)0001 (4)0011 2.二进制数011001的典型格雷码是( )。

(1)011011 (2)101101 (3)010111 (4)010101 3.表达式F=AB 可用来表示( )。

(1)A<B (2)A>B (3)A>B (4)A<B4.如将TTL “与非”门仅作为“非”门使用,则多余输入端应做( )处理。

(1)全部挂高 (2)其中一个接地 (3)全部接地 (4)部分接地 5.标准与或式是由( )构成的逻辑表达式。

(1)与项相或 (2)最小项相或 (3)最大项相与 (4)或项相与 6. 如图所示由两个”与非”门构成的基本触发器,欲使该触发器保持现态,则该触发器输入信号应为( )。

(1)S=R=0 (2)S=R=1 (3)S=1 R=0 (4)S=0 R=17.n 位二进制译码器与门阵列中,共有( )个二极管。

数字逻辑模拟试卷附答案

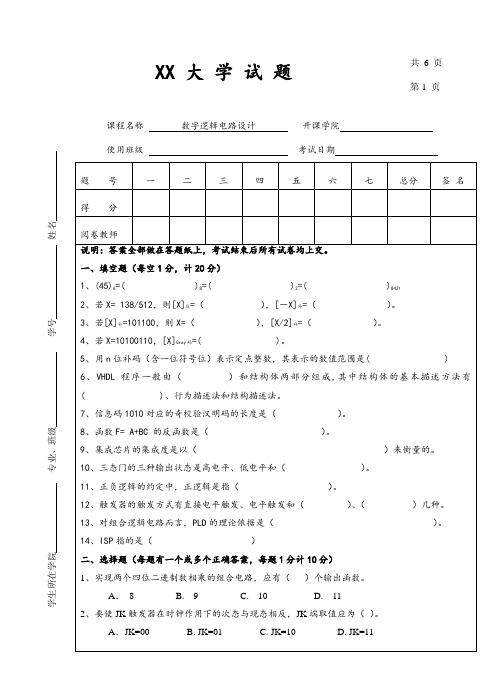

XX 大 学 试 题课程名称 数字逻辑电路设计 开课学院使用班级 考试日期苏 大 学 试题 第3 页苏大 学 试题第4 页四、根据下图波形写出其逻辑关系表达式Z=F(A,B,C) (10分)A B C Z五、分析题:某同步时序逻辑电路如图所示。

(12分)(1) 写出该电路激励函数和输出函数; (2) 画出输出矩阵和激励矩阵; (3) 画出状态表和状态图;(4)设各触发器的初态均为0,试画出下图中Q1、Q2和Z 的输出波形。

数字逻辑模拟试卷2答案一、填空题(每空1分,计20分) 1、(45)6=(35)8=(11101)2=(00101001)84212、若X= 138/512,则[X]反=(0.01000101),[-X]补=(1.10111011)。

3、若[X]补=101100,则X=(-100100),[X/2]补=(110110)。

4、若X=10100110,[X]Gray 码=(11110101)。

5、用n 位补码(含一位符号位)表示定点整数,其表示的数值范围是(-2n-1~2n-1-1)6、VHDL 程序一般由(实体)和结构体两部分组成,其中结构体的基本描述方法有(数据流描述法)、行为描述法和结构描述法。

7、信息码1010对应的奇校验汉明码的长度是(7位)。

8、函数F= A+BC 的反函数是()(C B A )。

9、集成芯片的集成度是以(等效门电路的数量)来衡量的。

10、三态门的三种输出状态是高电平、低电平和(高阻状态)。

11、正负逻辑的约定中,正逻辑是指(高电平表示1;低电平表示0)。

12、触发器的触发方式有直接电平触发、电平触发和(脉冲触发)、(边沿触发)几种。

13、对组合逻辑电路而言,PLD 的理论依据是(任何组合逻辑函数都可以用与-或式表示)。

14、ISP 指的是(在系统可编程技术)二、选择题(每题有一个或多个正确答案,每题1分计10分)1、A2、D3、B ,C4、A ,D5、A ,B ,D6、A ,B ,C7、A ,B ,C8、B9、B ,D 10、C 三、按要求化简下列函数(14分)1.用代数法求函数 F = A B + A B C + B C 的最简“与-或”表达式。

数字逻辑10套题

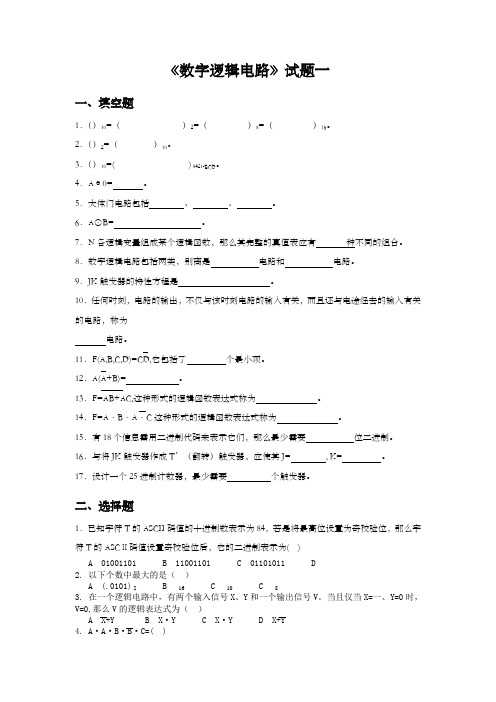

《数字逻辑电路》试题一一、填空题1.()10=()2=()8=()16。

2.()2=()10。

3.()10=( ) 8421-BCD。

4.A⊕0= 。

5.大体门电路包括、、。

6.A⊙B= 。

7.N各逻辑变量组成某个逻辑函数,那么其完整的真值表应有种不同的组合。

8.数字逻辑电路包括两类,别离是电路和电路。

9.JK触发器的特性方程是。

10.任何时刻,电路的输出,不仅与该时刻电路的输入有关,而且还与电途经去的输入有关的电路,称为电路。

11.F(A,B,C,D)=CD,它包括了个最小项。

12.A(A+B)= 。

13.F=AB+AC,这种形式的逻辑函数表达式称为。

14.F=A·B·A·C这种形式的逻辑函数表达式称为。

15.有18个信息需用二进制代码来表示它们,那么最少需要位二进制。

16.与将JK触发器作成T’(翻转)触发器,应使其J= , K= 。

17.设计一个25进制计数器,最少需要个触发器。

二、选择题1.已知字符T的ASCII码值的十进制数表示为84,若是将最高位设置为奇校验位,那么字符T的ASCⅡ码值设置奇校验位后,它的二进制表示为( )A 01001101B 11001101C 01101011 D2. 以下个数中最大的是()A (.0101) 2B 16C 10 C 83. 在一个逻辑电路中,有两个输入信号X、Y和一个输出信号V。

当且仅当X=一、Y=0时,V=0,那么V的逻辑表达式为()A X+YB X·YC X·YD X+Y4. A·A·B·B·C=( )A ABC C 1D 05. A+BC+AB+A=( )A AB AC 1D 06. F(A,B,C)=ABC+ABC+ABC=( )A ∑m(0,2,4)B ∑m(3,5,7)C ∑m(1,3,5)D ∑m(4,5,7)7. A⊕B=( )A AB+ AB B AB + ABC A BD A B8. 对正逻辑而言,某电路是与门,那么对负逻辑而言是()A 与门B 与非门C 或非门D 或门触发器在同步工作时,假设现态Q n=0,要求抵达次态Q n+1=1,那么应使JK=( )A 00B 01C 1XD X110.图(1)中要求输出F=B,那么A应为( )A 0B 1 A =1 FC B BD B 图(1)三、化简以下函数表达式一、代数化简:Y=(AB+A B+A B)(A+B+D+A B D)二、Y=AB+A B+A B3、卡诺图化简:F=(A,B,C,D)=∑m(0,1,2,3,4,6,8,9,10,11,12,14)四、芯片的应用1.别离用74138和74153实现逻辑函数表达式F=AB+BC+AC2.用1.用与非门设计一个组合电路,用来检测并行输入的四位二进制数B4B3B2B1当其值大于或等于5时,输出F=1,反之F=0。

数字逻辑考试题

二、选择(5分)

1. 的反函数为 =( )。

A. B.

C. D.

2.下列哪个元件是CMOS器件( )。

A. 74S00B. 74LS00C. 74HC00D. 74H00

3.十进制数25用8421BCD码表示为()。

A.10101 B.0010 0101 C.100101 D.10101

5.数字电路按照是否有记忆功能通常可分为两类:、。

A.变量译码器B.加法器C.数码寄存器D.数据选择器

6.GAL是指( )。

A.专用集成电路B.可编程阵列逻辑

C.通用集成电路D.通用阵列逻辑

7.RAM与ROM二者不同的是( )。

A.存储容量B.输出位数C.读操作D.写操作

8.子程序的重载不包括以下( )类型的重载。

A.参数类型的重载B.参数目的的重载

11.AB+ C+ C的最简与或表达式为。=AB+( + )C=AB+ C=AB+C

12.对于共阴极显示器,可以用输出的七段译码器7448来进行译码驱动。

13.将特定的信息表示成二进制代码的过程称为。

二、选择题(每题1分,共10分)

1.下列各门电路中,( )的输出端可直接相连,实现线与。

A.一般TTL与非门B.集电极开路TTL与非门

A. 01B. 11C. 00 D. 10

5.余3码10001000对应的2421码为( )。

A. 01010101B. 10000101

C. 10111011D. 11101011

6.RAM与ROM二者不同的是( )。

A.存储容量B.输出位数C.读操作D.写操作

数字逻辑自测题参考答案

Q3

Q2

Q1

DQ >CP

DQ >CP

DQ >CP

CLK

module exam (clk, q) ; input clk ; output [3:1] q ; reg [3:1] q ; always @ (posedge clk) case (q) 3’b001 : q<=3’b100 ; 3’b100 : q<=3’b010 ; 3’b010 : q<=3’b001 ; default : q<=3’b001 ; endcase

12. 已知某组合电路的输出表达式为 F ( a ,b,c ) a • b b c ,用Verilog

HDL的数据流描述方式建模。

module M1(a,b,c,F); input a,b,c; output F; assign F=~(a&b)|(b^c); endmodule

第6页/共41页

s2=x3⊕x2⊕x1 s1=x3 x2 +(x3⊕ x2) x1

Verilog 模型: module CT (x3,x2,x1,s2,s1); input x3,x2,x1; output s2,s1; assign {s1,s2}=x3+x2+x1; endmodule

第14页/共41页

功能:

若 将 x3 、 x2 作 为两个加数,

X Q1 Q0 000 001 010 011 100 101 110 111

J1 K1 J0 K0 Q1(t+1) Q0(t+1) Z

00 00

00

0

00 00

01

0

00 00

10

0

数字逻辑考题及答案

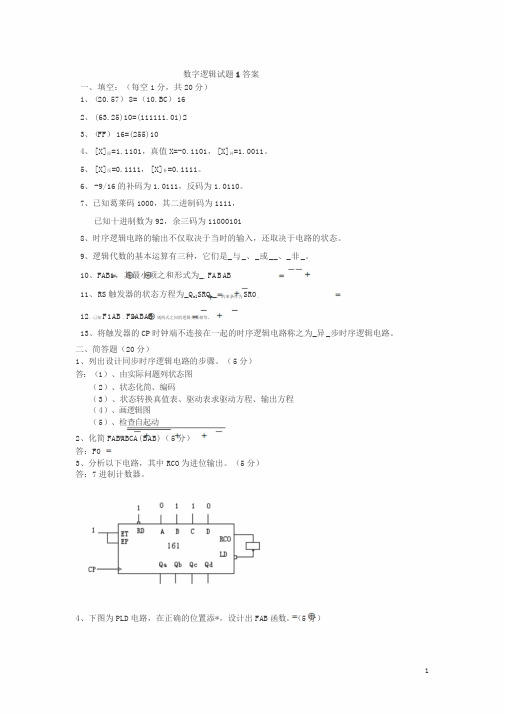

数字逻辑试题1答案一、填空:(每空1分,共20分)1、(20.57)8=(10.BC)162、(63.25)10=(111111.01)23、(FF)16=(255)104、[X]原=1.1101,真值X=-0.1101,[X]补=1.0011。

5、[X]反=0.1111,[X]补=0.1111。

6、-9/16的补码为1.0111,反码为1.0110。

7、已知葛莱码1000,其二进制码为1111,已知十进制数为92,余三码为110001018、时序逻辑电路的输出不仅取决于当时的输入,还取决于电路的状态。

9、逻辑代数的基本运算有三种,它们是_与_、_或__、_非_。

10、FAB1,其最小项之和形式为_。

FA B AB11、RS触发器的状态方程为_Q n1SRQ n_,约束条件为SR0。

12、已知F1AB、F2ABAB,则两式之间的逻辑关系相等。

13、将触发器的CP时钟端不连接在一起的时序逻辑电路称之为_异_步时序逻辑电路。

二、简答题(20分)1、列出设计同步时序逻辑电路的步骤。

(5分)答:(1)、由实际问题列状态图(2)、状态化简、编码(3)、状态转换真值表、驱动表求驱动方程、输出方程(4)、画逻辑图(5)、检查自起动2、化简FABABCA(BAB)(5分)答:F03、分析以下电路,其中RCO为进位输出。

(5分)答:7进制计数器。

4、下图为PLD电路,在正确的位置添*,设计出FAB函数。

(5分)15分注:答案之一。

三、分析题(30分)1、分析以下电路,说明电路功能。

(10分)解:XY m(3,5,6,7)m(1,2,4,7)2分ABCiXY0000000101010010111010001101101101011111该组合逻辑电路是全加器。

以上8分2、分析以下电路,其中X为控制端,说明电路功能。

(10分)解:FXA B C XABCXABCXABCXABCXABC4分FX(ABC)X(A B C ABC)4分所以:X=0完成判奇功能。

数字逻辑考题及答案

数字逻辑试题1答案一、填空:(每空1分,共20分) 1、(20.57)8 =( 10.BC )16 2、(63.25) 10= ( 111111.01 )2 3、(FF )16= ( 255 )104、[X]原=1.1101,真值X= -0.1101,[X]补 = 1.0011。

5、[X]反=0.1111,[X]补= 0.1111。

6、-9/16的补码为1.0111,反码为1.0110 。

7、已知葛莱码1000,其二进制码为1111, 已知十进制数为92,余三码为1100 01018、时序逻辑电路的输出不仅取决于当时的输入,还取决于电路的状态 。

9、逻辑代数的基本运算有三种,它们是_与_ 、_或__、_非_ 。

10、1⊕⊕=B A F ,其最小项之和形式为_ 。

AB B A F += 11、RS 触发器的状态方程为_n n Q R S Q +=+1_,约束条件为0=SR 。

12、已知B A F ⊕=1、B A B A F +=2,则两式之间的逻辑关系相等。

13、将触发器的CP 时钟端不连接在一起的时序逻辑电路称之为_异_步时序逻辑电路 。

二、简答题(20分)1、列出设计同步时序逻辑电路的步骤。

(5分) 答:(1)、由实际问题列状态图 (2)、状态化简、编码 (3)、状态转换真值表、驱动表求驱动方程、输出方程 (4)、画逻辑图 (5)、检查自起动2、化简)(B A B A ABC B A F +++=(5分) 答:0=F3、分析以下电路,其中RCO 为进位输出。

(5分) 答:7进制计数器。

4、下图为PLD 电路,在正确的位置添 * , 设计出B A F ⊕=函数。

(5分)5分 注:答案之一。

三、分析题(30分)1、分析以下电路,说明电路功能。

(10分)解: ∑∑==)7,4,2,1()7,6,5,3(m Y m X 2分A B Ci X Y 0 0 0 0 0 0110 1 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1该组合逻辑电路是全加器。

数字逻辑与数字系统模拟试题2

数字逻辑与数字系统模拟试题2一、填空题(每空一分)1、位置计数法三个要素是、和。

2、数字信号的特点是在上和上都是断续变化的,其高电平和低电平常用和来表示。

3、( 35.4)8 =()2 =( )10=( )164、单稳态触发器特点之一是:有一个和一个。

5、描述脉冲波形的主要参数有、、、、、、。

6、TTL OC门(集电极开路门)的输出端可以直接相连,实现。

二、判断题(正确打√,错误的打×;每题2分)1、十进制数具有两个特点:计数基数为10,逢“十”进位。

2、与逻辑关系是指只有当决定一件事情的全部条件具备之后,结果才能发生。

3、实现两个二进制数相加的电路称为半加。

4、单稳态触发器一般用于定时、整形和产生方波。

5、将模拟量转换为数字量的过程称为数/模转换。

三、选择题(在给定的四个答案中选择一个正确答案,每题2分)1、在何种输入情况下,“与非”运算的结果是逻辑0。

A.全部输入是0 B.任一输入是0 C.仅一输入是0 D.全部输入是12、以下电路中常用于总线应用的有 A 。

A.三态门B.O C门C.漏极开路门D.C M O S与非门3、N个触发器可以构成二进制寄存器的位数为。

A.N-1位B.N位C.N+1位D.2N位4、多谐振荡器可产生。

A.正弦波B.矩形脉冲C.三角波D.锯齿波5、石英晶体多谐振荡器的突出优点是。

A.速度高B.电路简单C.振荡频率稳定D.输出波形边沿陡峭6、以下各电路中,可以产生延时的电路是。

A.多谐振荡器B.单稳态触发器C.施密特触发器D.石英晶体多谐振荡器7、若在编码器中有50个编码对象,则要求输出二进制代码位数至少应为 位。

A.5 B.6 C.10 D.508、一个16选一的数据选择器,其地址输入端有 个。

A.1B.2C.4D.169、一个16选一的数据选择器,其数据输入端有 个。

A.1B.2C.4D.1610、用RAM2114(1024×4位)构成4096×8位RAM ,需A 、4片;B 、8片;C 、24片;D 、12片四、按要求解答下列问题(每题10分)1、试用公式化简法化简逻辑函数为最简与或表达式。

山东科技大学数字逻辑期末考试题3

《数字逻辑》模拟试题1班级 姓名 成绩一、已知[x]反=1.0110求[x]原= [x]补= x= 各为多少?(6分)二、已知逻辑函数∑∑+=)12,6,1,0()15,13,8,7,5,4(),,,(d m D C B A F1. 将函数移植到卡诺图上2.求F 的最简“与-或”表达式3.求F 的最简“或-与”表达式。

(10分) 三、化简CD D AC ABC C A F +++= (10分)四、真值表证明下列等式(10分)))((B A B A B A B A ++=+五、用卡诺图判断下列函数F 和G 有何关系?(10分)1.A C BC B A G C B A C AB F ++=+=,2.C A C B B A G AC BC AB F ++=++=,3.∑∑==)7,4,2,0(),7,4,2,0(m G m F六、用卡诺图求函数.(10分)∑=)15,13,11,10,7,4,3,2(),,,(m D C B A F的最简"与-或"表达式。

七、设21x x X =和21y y Y =是两个二进制正整数,试用"与-非"门设计一个判断X>Y的逻辑电路。

(10分)八、用T触发器作为存储元件,设计一个两位二进制减1计数器.电路工作状态受输入信号X的控制.当X=0时,电路状态不变;当X=1时,在时钟脉冲作用下进行减1计数.计数器有一个输出Z,当产生借位时Z为1,其他情况下Z为0。

(10分)九、简述组合逻辑电路、同步时序逻辑电路、异步时序逻辑电路的特点,并画出其结构框图。

为使异步时序逻辑电路能按预定的要求工作,应对其输入作些什么规定?为什么?(10分)十、用3-8译码器和与非门实现全加器的功能。

(10分)一、解: 101001][=x 原 ][x 补=1.0111 x= -0.1001 三、解:(1)(2)BD D C F +=(3)D C D B F += ))((D C D B F ++=。

数字逻辑试题及答案

数字逻辑试题及答案一、选择题(每题2分,共20分)1. 以下哪个是数字逻辑电路中的基本逻辑运算?A. 加法B. 减法C. 乘法D. 与运算2. 一个3输入的与门,当所有输入都为高电平时,输出为:A. 低电平B. 高电平C. 浮空D. 不确定3. 一个D触发器的Q端在时钟信号上升沿触发时,其状态变化为:A. 保持不变B. 从0变到1C. 从1变到0D. 从D输入端状态变化4. 在数字电路中,以下哪个不是布尔代数的基本定理?A. 幂等律B. 交换律C. 反演律D. 分配律5. 一个4位二进制计数器在计数到31后,下一个状态是:A. 00000B. 00001C. 11111D. 不能确定6. 以下哪个不是数字逻辑电路设计中的优化方法?A. 布尔代数简化B. 逻辑门替换C. 增加冗余D. 逻辑划分7. 一个异或门的真值表中,当输入相同,输出为:A. 0B. 1C. 无法确定D. 无输出8. 在数字电路中,同步计数器与异步计数器的主要区别在于:A. 计数范围B. 计数速度C. 电路复杂度D. 计数精度9. 以下哪个不是数字逻辑电路中的存储元件?A. 触发器B. 寄存器C. 计数器D. 逻辑门10. 一个简单的数字逻辑电路设计中,如果需要实现一个2输入的或门,至少需要几个与门?A. 1B. 2C. 3D. 4答案:1. D2. B3. D4. C5. B6. C7. A8. B9. D10. A二、填空题(每空2分,共20分)1. 数字逻辑电路中最基本的逻辑运算包括______、或运算、非运算。

2. 一个2输入的与门,当输入都为高电平时,输出为______。

3. 布尔代数的基本定理包括______、结合律、分配律等。

4. 一个D触发器的Q端在时钟信号上升沿触发时,Q端状态与______相同。

5. 4位二进制计数器的计数范围是从______到1111。

6. 数字逻辑电路设计中的优化方法包括布尔代数简化、逻辑门替换、______等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字逻辑模拟试题一.单项选择题1.表示任意两位无符号十进制数至少需要()二进制数。

A.6 B.7 C.8 D.92.余3码10001000对应的2421码为()。

A.01010101 B.10000101 C.10111011 D. 111010113.下列四个数中与十进制数(72)10相等的是( ) A.(01101000)2 B.(01001000)2C.(01110010)2D.(01001010)24.某集成电路芯片,查手册知其最大输出低电平U OLmax=0.5V,最大输入低电平U ILmax=0.8V,最小输出高电平U OHmin=2.7V,最小输入高电平U IHmin=2.0V,则其高电平噪声容限U NH=( )A .0.3V B.0.6V C.0.7V D.1.2V5.标准或-与式是由( )构成的逻辑表达式。

A .与项相或 B. 最小项相或 C. 最大项相与D.或项相与6.根据反演规则,的反函数为( )。

A. B. C. D. 7、对于TTL 或非门多余输入端的处理,不可以( )。

A 、接电源B 、通过0.5k Ω电阻接地C 、接地D 、与有用输入端并联8.下列四种类型的逻辑门中,可以用( )实现三种基本逻辑运算。

A. 与门B. 或门C. 非门D. 与非门9. 将D 触发器改造成T 触发器,图1所示电路中的虚()()E DE C C A F ++⋅+=E )]E D (C C [A F ⋅++=E)E D (C C A F ⋅++=E )E D C C A (F ⋅++=E )(D A F ⋅++=E C C线框内应是()。

A. 或非门B. 与非门C. 异或门D. 同或门10.以下电路中可以实现线与功能的有()。

A.与非门B.三态输出门C.传输门D.漏极开路门11.要使JK触发器在时钟作用下的次态与现态相反,JK 端取值应为()。

A.JK=00 B. JK=01 C. JK=10 D. JK=11 12.设计一个四位二进制码的奇偶校验器,需要()个异或门。

A.2 B. 3 C. 4 D. 513.相邻两组编码只有一位不同的编码是( ) A.2421BCD码 B.8421BCD码 C.余3码 D.循环码14.下列电路中,不属于时序逻辑电路的是( ) A.计数器 B.全加器 C.寄存器 D.RAM15.一个4位移位寄存器,现态为0111,经右移1位后其次态为( )A.0011或1011 B.1101或1110C.1011或1110D.0011或111116.为了将正弦信号转换成与之频率相同的脉冲信号,可采用( )A.多谐振荡器 B.移位寄存器C.单稳态触发器D.施密特触发器17.一个6位地址码、8位输出的ROM,其存储矩阵的容量为( )bit.A.64×8 B.48 C.256 D.818.某8位DAC,当输入全为1时,输出电压为5.10V,当输入D=(10000000)2时,输出电压为( ) A.5.10V B.2.56V C.1.28V D.都不是19.PROM 是一种__________可编程逻辑器件。

( )A .与阵列可编程、或阵列固定的B.与阵列固定、或阵列可编程的C.与、或阵列固定的D.与、或阵列都可编程的20、ROM 不能用于_________。

A. 函数运算表B. 存入程序C. 存入采集的动态数据D. 字符发生器二.多项选择题1.逻辑函数F=A⊕B 和G=A⊙B 满足关系( )。

A. G F = B. G F =' C. G F =' D. 1G F ⊕=2.函数 则F 和G 相“与”的结果是( )。

A .32m m +B . 1C . B AD . AB3.设两输入或非门的输入为x 和y ,输出为z ,当z 为低电平时,有( )。

∑∑==5,7),m(0,2,3,4,C)B ,G(A,,m(1,2,3,6)C)B ,F(A,A.x和y同为高电平;B.x为高电平,y为低电平;C.x为低电平,y为高电平;D.x和y同为低电平. 4.组合逻辑电路的输出与输入的关系可用()描述。

A.真值表 B. 流程表C.逻辑表达式 D. 状态图5. TTL电路在正逻辑系统中,以下输入中()相当于接1。

A.悬空 B. 通过3kΩ电阻接电源C.通过3kΩ电阻接地 D. 通过510Ω电阻接地三.填空题1.数字逻辑电路可分为组合和__________两大类。

2.用与、或、非等运算表示函数中各个变量之间逻辑关系的代数式叫__________。

3.四变量逻辑函数的标准与或式为F(a,b,c,d)=∑m(0,2,3,4,6,8,9,11,13) ,其标准或与式为__________,它的反函数的标准与或式为________________。

4.三态逻辑门输出有三种状态:0态、1态和__________。

5.在组合逻辑电路中,当输入信号改变状态时,输出端可能出现的虚假过渡干扰脉冲的现象称为__________。

6.根据需要选择一路信号送到公共数据线上的电路叫__________。

7、16个触发器构成计数器,该计数器可能的最大计数模值是__________。

8.触发器按功能分可分为RS、D、JK、T和__________。

9.某计数器的输出波形如图1所示,该计数器是__________进制计数器。

10.Moore型时序逻辑电路的输出仅仅取决于__________,而不受电路当时的输入信号影响或没有输入变量。

11.对于一个频率有限的模拟信号,设其最高频率分量的频率为f max,在取样后为了无失真地恢复原始输入信号频谱,取样时必须满足取样频率:f s≥__________。

12.为了构成8K×16bit的RAM,需要_____片1K×8bit的RAM,地址线的高_____位作为地址译码的输入,地址译码使用的是___线-___线译码器。

13.在A/D转换中,最小量化单位为Δ,如果使用四舍五入法,最大量化误差为___,如果使用只舍不入法,最大量化误差为___。

14、10位A/D转换器中,已知输出为258H时,对应的输入电压为1.2V,则当输入的电压为1.8V时,输出的数字量是__________H。

15.74LS138是3线-8线译码器,译码输出为低电平有效,若输入A2A1A0=100时,输出01234567Y YYY=__________。

YYYY16.8线—3线优先编码器74LS148的优先权顺序是I7,I6,⋯⋯I1,I0 ,输入低电平有效,输出Y2 Y1 Y0为二进制反码输出。

当I7I6I5I4I3I2I1I0 为11010101时,输出Y2 Y1 Y0=______。

四、分析题1.用图形法将下列逻辑函数化成最简“与或”式。

F(A,B,C,D)=∑m(0,2,4,5,6,7,12)+∑d(8,10)2.分析图中所示电路的逻辑功能。

列出真值表,写出电路输出函数S的逻辑表达式。

3、分析图中所示的组合逻辑电路,要求:(1)写出输出Y1、Y2的表达式。

(2)列出真值表(3)说明电路逻辑功能4.根据图中所示4选1数据选择器实现的组合电路,写出输出E表达式并化成最简“与或”表达式。

5、时序电路如图所示,写出各触发器的驱动方程、该电路的状态方程,并画出状态转换图,说明电路功能(设各触发器的初态均为0)。

6、电路如图所示,已知CP端输入脉冲的频率为10kHz,试分析当输入控制信号A,B,C,D,E,F,G,H,I分别为低电平时,Y 端输出的脉冲频率各为多少?并说明电路的逻辑功能。

五、设计题B I1.在举重比赛中,有甲、乙、丙三位裁判,其中甲为主裁判,当两位或两位以上裁判(其中必须包括主裁判在内)认为运动员上举合格,才可发出合格信号,用最少的与非门设计满足上述要求的组合逻辑电路。

2、试用PLA设计一个满足以下要求的译码电路。

该电路输入信号DCBA为4位二进制码。

输出信号Y1、Y2、Y3在下列几种情况下有确定的状态:①当DCBA所对应的十进制数为1~3时,Y1=1,Y2=Y3=0;②当DCBA所对应的十进制数为6~8时,Y2=1,Y1=Y3=0;③当DCBA所对应的十进制数为11~13时,Y3=1,Y1=Y2=0。

3.用同步四位二进制计数器74161构成初始状态为0100的七进制计数器。

画出状态转换图和连线图。

4.用同步四位二进制计数器74160构成48进制的计数器。

画出状态转换图和连线图。

5、用八选一数据选择器74HC151设计一个函数发生器电路,S1、S2为控制端,A、B为逻辑变量输入端,Y 为函数发生器输出端,要实现的功能如图所示。

6、图(a)是一个序列信号产生电路的框图,其输出L 与时钟脉冲CP的波形如图(b)所示。

试用边沿D触发器和中规模组合逻辑器件设计该时序电路。

六、作图题1、图中(d)所示A、B、C信号为图(a)、(b)、(c)各电路的输入波形。

分析电路,试对应画出L1、L2和L3的输出波形。

(d)2、触发器电路及输入信号的波形如图所示,试分别画出D触发器的Q和Q1的波形。

3.由集成定时器555的电路如图7所示,请回答下列问题。

(1)构成电路的名称;(2)已知输入信号波形u I,画出电路中u O的波形(标明u O波形的脉冲宽度);。