第2节 8086总线的工作周期

80868088 CPU的工作时序

微机原理第2章8086/8088系统结构8086/8088 的工作时序1. 时钟周期、总线周期、指令周期微机原理时钟周期:是CPU的基本时间单位,记为T,其值为计算机主频的倒数。

微机原理时钟周期:是CPU 的基本时间单位,记为T ,其值为计算机主频的倒数。

总线周期:CPU 通过总线对存储器或I/O 进行1次访问所需要的时间。

它至少包含4个T ,记为T 1,T 2,T 3,T 4.1. 时钟周期、总线周期、指令周期1. 时钟周期、总线周期、指令周期微机原理的时间,它包含一个或多个总线周期。

常采用MIPS(Million Instructions Per Second)作单位。

微机原理(1) 8086读总线周期T 1T 2T3T 4一个总线周期CLK A 19~A 16S 6~S 3A 19/S 6 ~ A 16/S 3DATA INAD 15 ~ AD 0ALE 低=I/O ,高=MM/IORD DT/R DENA 15~A 02. 读/写工作时序微机原理(2) 8086写总线周期T 1T 2T 3T 4一个总线周期CLK A 19 ~ A 16S 6 ~ S 3A 19/S 6 ~ A 16/S 3DATA OUTAD 15 ~ AD 0ALE 高=I/O ,低=MM/IOWRDT/R DENA 15~A 0微机原理(3)8086具有等待状态的读总线周期T 1T 2T 3T W 一个总线周期CLK A 19~A 16A 19/S 6 ~ A 16/S 3DATA INAD 15 ~ AD 0ALE 低=I/O ,高=MM/IORD DT/RDEN A 15~A 0T 4READYWAITREADYS 6~S 3微机原理(4) 8088读总线周期T 1T 2T 3T 4一个总线周期CLK A 19~A 16S 6~S 3A 19/S 6 ~ A 16/S 3DATA INAD 7 ~ AD 0ALE 高=I/O ,低=MIO/MRD DT/R DENA 7~A 0A 15 ~ A 8A 15~A 8微机原理例1:在8088 CPU 中对存储器进行读操作时,CPU 引脚的IO/M 、RD 、WR 、DT/R 的输出电平分别是什么?例2:在若在1个总线周期中,插入了3个T W ,请问在该总线周期中对READY 信号进行了几次采样?低电平低电平高电平低电平4微机原理下次课见。

8086的总线操作和时序及工作模式

READY

RESET

GND A14 A13 A12 A11 A10 A9 A8 AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0 NMI

INTR CLK GND

8088

1

40

2

39

3

38

4

37

5

36

6

35

7

34

8

33

9

32

10

31

11

30

12

29

13

28

14

27

15

26

16

25

17

24

状态Ti

总线操作与时序

➢ 时序(Timing)是指信号高低电平(有效或无效)变化及 相互间的时间顺序关系

➢ 总线时序描述CPU引脚如何实现总线操作

5.1 时钟周期、总线周期和指令周期

描述总线操作的CPU时序有三级 ◦ 指令周期 → 总线周期 → 时钟周期 指令周期(Instruction Cycle) 1、 8086CPU执行一条指令所需要的时间称为指令周期 (Instruction Cycle) 。 2、一个指令周期由一个或若干个总线周期组成,不同指令 的指令周期不是等长的,最短为一个总线周期,长的指令周 期,如乘法指令周期,长达124个时钟周期。

地址总线

数据总线

数据总线

控制总线

第二章 8086 CPU[2-3]

![第二章 8086 CPU[2-3]](https://img.taocdn.com/s3/m/e08657c3da38376baf1faef3.png)

应用例子:发光二极管接口

+5V

D0~D7 A0~A15

IOW

20:49

D|0 Q0

1

R

D7

...

...

...

...

译

码

CP

器

R

Q7

1

74LS273

12

§2-4 8086的工作模式和总线操作

3、时钟发生器8284A

产生CLK信号,作为8086CPU的内部和外部的时间基准信号 提供系统时钟(CLK)、READY同步和RESET同步信号

第二章 8086 CPU

内容提要

引言 8086 CPU的内部结构 8086/8088 CPU的引脚功能 8086的存储器组织 8086的工作模式和总线操作

20:49

2

§2-4 8086的工作模式和总线操作

1、电源要求

8086/8088微处理器都是用+5.0V电源电压,其允许偏差为±10%。

OE

地址总线

存储器

I/O芯片

20:49

T 74LS245 /8286/82 87

OE

数据总线

15

§2-4 8086的工作模式和总线操作

2.4.3 总线操作时序

相关概念介绍

➢时钟周期

➢总线周期

➢指令周期

➢时序 ➢时序图

时序就是指系统中各总线信号(即地址、 数据和控制信号)产生的先后次序。

20:49

16

在8086/8088CPU中,一个总线周期至少包括4个时钟周期。

1~2个

若干个

T1 T2 T3 T4 Ti Ti T1 T2 T3 Tw Tw Tw T4 Ti Ti

【教学课件】第2章 8086微处理器

控制 电路

局部总线 接口

SYSB/RESB

1

20

2

19

3

18

4

17

5

8289 16

6

15

7

14

8

13

9

12

10

11

INIT

BCLK BREQ BPRN BPRO BUSY CBRQ

总线仲裁 信号

AEN

V CC S1 S0 CLK

LOCK

CRQLCK ANYRQST

AEN CBRQ BUSY

2021/8/17

DEN CEN

INTA IORC AIOWC IOWC

2021/8/17

23

2.总线仲裁控制器8289

仲裁电路

状态

S2

信号

S1

S0

状态 译码器

多路总线 接口

控制 输入

LOCK CLK

CRQLCK

RESB ANYRQST

IOB

S2 IOB

RESB BCLK INIT BREQ BPRO BPRN

GND

数据总线

2021/8/17

S0

S1

S2

INTR R Q / G T0

R Q / G T1

8288 总线控制器

IN T A

8259A 及有关电路

控制总线 中 断 请 求

22

1.总线控制器8288

状态

S2

信号

S1

S0

状态 译码器

控制 输入

CLK

AEN CEN IOB

控制 电路

命令 信号 发生器

控制信号 发生器

2.3.1 最小模式和最大模式的概念

8086CPU系统、总线操作和时序

8086CPU系统、总线操作和时序8086CPU系统、总线操作和时序第⼀节 8086的引脚信号与功能回顾:8086/8088微型计算机的组成、结构及微机系统的⼯作过程,微机系统的存储器组织及相关概念。

本讲重点:8086/8088CPU的两种⼯作模式,8086/8088CPU的外部结构,即引脚信号及其功能。

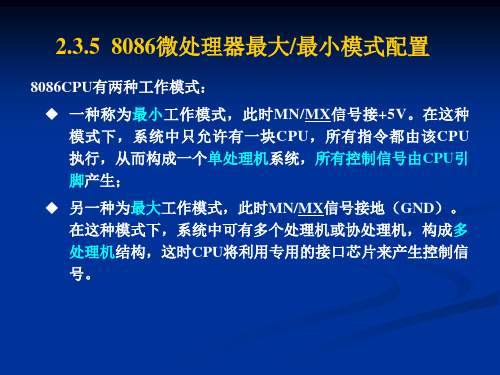

讲授内容:⼀、 8086/8088微处理器⼯作模式及外部结构1.8086/8088CPU的两种⼯作模式为了适应各种使⽤场合,在设计8088/8086CPU芯⽚时,就考虑了其应能够使它⼯作在两种模式下,即最⼩模式与最⼤模式。

所谓最⼩模式,就是系统中只有⼀个8088/8086微处理器,在这种情况下,所有的总线控制信号,都是直接由8088/8086CPU 产⽣的,系统中的总线控制逻辑电路被减到最少,该模式适⽤于规模较⼩的微机应⽤系统。

最⼤模式是相对于最⼩模式⽽⾔的,最⼤模式⽤在中、⼤规模的微机应⽤系统中,在最⼤模式下,系统中⾄少包含两个微处理器,其中⼀个为主处理器,即8086/8086CPU,其它的微处理器称之为协处理器,它们是协助主处理器⼯作的。

与8088/8086CPU配合⼯作的协处理器有两类,⼀类是数值协处理器8087 另⼀类是输⼊/输出协处理器8089。

8087是⼀种专⽤于数值运算的协处理器,它能实现多种类型的数值运算,如⾼精度的整型和浮点型数值运算,超越函数(三⾓函数、对数函数)的计算等,这些运算若⽤软件的⽅法来实现,将耗费⼤量的机器时间。

换句话说,引⼊了8087协处理器,就是把软件功能硬件化,可以⼤⼤提⾼主处理器的运⾏速度。

8089协处理器,在原理上有点像带有两个DMA通道的处理器,它有⼀套专门⽤于输⼊/输出操作的指令系统,但是8089⼜和DMA控制器不同,它可以直接为输⼊/输出设备服务,使主处理器不再承担这类⼯作。

所以,在系统中增加8089协处理器之后,会明显提⾼主处理器的效率,尤其是在输⼊/输出操作⽐较频繁的系统中。

8086总线周期时钟周期

2. 总线接口部件 BIU 负责CPU与存储器、I/O设备之间传送数据、地址、 状态及控制信息。 组成:

● 4个段地址寄存器(CS、DS、ES、SS) ● 16位的指令指针寄存器IP(Instruction Pointer) ● 20位的地址加法器 ● 6字节的指令队列缓冲器 ● 总线控制逻辑

注意:一个存储单元的物理地址是惟一的,而它对应 的逻辑地址是不惟一的。

30

(3)指令指针寄存器IP—— 16位

功能:用来存放将要执行的下一条指令在代码段中的 偏移地址。在程序运行过程中,BIU自动修改 IP中的内容,使它始终指向将要执行的下一条 指令。

注意:程序不能直接访问IP,但是可通过某些指令修 改IP的内容。例如, 执行转移指令时,会将转 移的目标地址送入IP中,以实现程序的转移。

19

在8086存储空间中,把16字节的存储空间称作一内存节 (paragraph)。要求各个逻辑段从节的整数边界开始,即段 首地址低4位应该是“0”,把段首地址的高16位存放在段寄 存器DS或CS或SS或ES中。

00000H 00010H 00020H …… FFFF0H

20

允许段在整个存储空间浮动,即段与段之间可以 部分重叠、完全重叠、连续排列。在整个存储空间中 可设置若干个逻辑段。

地址指针自动增量;DF=1,表示地址指针自动减量。DF 可通过STD指令置位,也可通过CLD指令复位。

● IF(Interrupt Flag) 中断允许标志位 ----- 用于控制CPU是否允许响应可屏蔽中断请求。 IF=1,表示允许CPU响应可屏蔽中断请求。 IF=0, 表示禁止CPU响应可屏蔽中断请求。 IF可通过STI指令置 位(置1),也可通过CLI指令复位(清零)。

第2章28086工作模式、基本时序

8086有3个空闲周期,8088中无

T1

T2

T3

T4

Ti

Ti

Ti

T1

T2

T3

T4

CLK

ALE

INTA AD7-AD0

中断类型码

4.总线响应周期 当系统中有其它的总线主设备请求总线控制时, CPU进入

总线响应周期。

CLK HOLD

T1或T4下降沿

...

...

...

HLDA

... ...

...

数据、地址总线

... AD15-0、A9-16、S6-3

... 8086使用总线

...

... 3)8087,8089使用总线

5)8086重新控制总线

课后作业: 2.4 2.14 2.19 2.20 2.21

READY RDY2

5 6

READY,当外部器件准备好后向CPU AEN2 7

发出就绪信号。

CLK 8 GND 9

8284A

18 VCC 17 X1 16 X2 15 ASYNC

14 EFI 13 E/C 12 OSC 11 RES 10 RESET

(2)地址锁存电路

8086为了实现AD0-15引脚的复用功能,须 使用地址锁存电路。

I/O

I/O 设备

系 统

控制器产生。

CPU 245

(3)用于构成多处理机和

总

DB 线

数学协处理器大型系统。

8288

CB

2.4 8086微处理器的基本工作时序

2.4.1 时钟周期、总线周期和指令周期

时钟周期 T:CPU工作的时间脉冲。由时钟发生电路提供,每个时间脉冲 的间隔时间为时钟周期。 总线周期: 每4个时钟周期完成一次总线操作,即一个操作数的读/写操 作,称为总线周期。

2-3 8086系统总线时序

如果在一个总线周期后不立即执行下一个总线周期 即总线上无数据传输操作 系统总线处于空闲状态,则执行空闲周期T 系统总线处于空闲状态,则执行空闲周期 i 空闲周期 Ti也以时钟周期 为单位 也以时钟周期T为单位 两个总线周期之间插入几个Ti与 两个总线周期之间插入几个 与8086CPU执行的指令有关 执行的指令有关 如8086执行一条乘法指令时,需要 执行一条乘法指令时, 执行一条乘法指令时 需要124个T周期 个 周期 而其间使用总线的时间极少,大部分时间用于 而其间使用总线的时间极少,大部分时间用于CPU内部运算 内部运算 故指令周期中插入的T 多达100多个 故指令周期中插入的 i多达 多个

一个总线周期完成一次数据传送,至少包含两个过程: 一个总线周期完成一次数据传送,至少包含两个过程: (1)传送地址 ) (2)传送数据 ) CPU在T1周期将要访问的存储器或 端口的地址送上总线 将要访问的存储器或I/O端口的 在 周期将要访问的存储器或 端口的地址送上总线 周期通过总线 通过总线传送数据 在T2~T4周期通过总线传送数据 即数据传送必须在T 即数据传送必须在 2~T4这3个周期内完成 个周期内完成 否则在T 过后CPU将开始下一个总线周期。 将开始下一个总线周期。 否则在 4过后 将开始下一个总线周期 如果存储器或外设由于本身速度或其他原因,无法在3个 周期中 如果存储器或外设由于本身速度或其他原因,无法在 个T周期中 完成与CPU的数据交换,则 的数据交换, 完成与 的数据交换 发出请求延长总线周期的低电平信号到CPU的READY引脚 的 发出请求延长总线周期的低电平信号到 引脚 CPU检测到 检测到READY为低时,就在 3与T4之间插入等待周期 TW 为低时, 之间插入等待周期 检测到 为低时 就在T 插入T 插入 W的个数与外设请求信号的持续时间长短有关 通过插入T 周期,以降低系统的速度为代价,实现了高速CPU 通过插入 W周期,以降低系统的速度为代价,实现了高速 与低速的存储器或外设同步工作。 与低速的存储器或外设同步工作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

T1

T2 T3 Tw Tw Tw T4

READY

前沿检测

一条指令的执行包括取指令、分析指令和执行指令。 一条指令的执行包括取指令、分析指令和执行指令。 从取指令开始到指令执行完毕所花费的时间称为一个指令周期 从取指令开始到指令执行完毕所花费的时间称为一个指令周期 。 一个指令周期由一个或若干个总线周期组成

总线周期

1~2个 T1 T2 T3 T4 Ti Ti T1

若干个 T2 T3 Tw Tw Tw T4 Ti Ti

总线周期

总线周期

空闲时钟周期Ti, 空闲时钟周期 ,在两个总线周期之间插入 等待时钟周期Tw,在总线周期的 和 之间插入 等待时钟周期 ,在总线周期的T3和T4之间插入

返回

等待状态 CLK

个时钟周期T为 个时钟周期 例如: 的主频f为 例如 8086的主频 为5MHz 则1个时钟周期 为 的主频

1/f =1/(5*106) =200ns 8086CPU与其它部件交换信息都是通过总线进行的。 与其它部件交换信息都是通过总线进行的。 与其它部件交换信息都是通过总线进行的 CPU从存储器或外设存或取一个字节或字所需的时间称为总线周期。 从存储器或外设存或取一个字节或字所需的时间称为总线周期。 从存储器或外设存或取一个字节或字所需的时间称为总线周期 一个基本的总线周期由四个时钟周期组成

本节重点: 本节重点 1.时钟周期、总线周期、指令周期的含义,三者之间的关系。 时钟周期、总线周期、指令周期的含义,三者之间的关系。 时钟周期 2.时钟周期的计算 时钟周期的计算