数字电路第五版(康华光)5__锁存器和触发器

数电6.5(第五版)—康华光

如考虑每个触发器都有1t 的延时,电路会出现什么问题? 如考虑每个触发器都有 pd的延时,电路会出现什么问题?

1 CP Q0 0 Q1 0 Q2 0 Q3 0 1 0 0 0 0 1 0 0 1 1 0 0 0 0 1 0 1 0 1 0 0 1 1 0 1 1 1 0 2 3 4 5 6 7 8 9 1tpd 0 1 2tpd 0 0 3tpd 0 0 4tpd 1 1 10 11 12 13 14 15 16

21

二进制计数器 加计数器 非二进制计数器 任意进制计数器 •同步计数器 同步计数器 减计数器 可逆计数器 二进制计数器 加计数器 非二进制计数器 •异步计数器 异步计数器 任意进制计数器 减计数器 可逆计数器

22

十进制计数器 ……

十进制计数器 ……

1、 二进制计数器 、 (1) 异步二进制计数器 异步二进制计数器---4位异步二进制加法计数器 位异步二进制加法计数器 ① 工作原理

6.5 若干典型的时序逻辑集成电路

6.5.1 寄存器和移位寄存器 6.5.2 计数器

1

6.5 若干典型的时序逻辑集成电路 6.5.1 寄存器和移位寄存器

1、 寄存器 寄存器:是数字系统中用来存储代码或数据的逻辑部 寄存器 是数字系统中用来存储代码或数据的逻辑部 它的主要组成部分是触发器。 件。它的主要组成部分是触发器。 一个触发器能存储1位二进制代码, 一个触发器能存储 位二进制代码,存储 n 位二进 位二进制代码 个触发器组成。 制代码的寄存器需要用 n 个触发器组成。寄存器实际 上是若干触发器的集合。 上是若干触发器的集合。

FF m + 1 D m +1 1D C1

CP Q m –1 Qm Q m +1

数电第五版_部分课后答案(清晰pdf康光华主编).txt

解:由图知该电路属于漏极开路门的线与输出

L E L4 E L1 L2 L3 E AB BC D

3.1.9 图题 3.1.9 表示三态门作总线传输的示意图,图中 n 个三态门的输出接到数据传 输总线,D1、D2、…、Dn 为数据输入端,CS1、CS2、…、CSn 为片选信号输入端。试问: (1)CS 信号如何进行控制,以便数据 D1、D2、…、Dn 通过该总线进行正常传输;(2)CS 信 号能否有两个或两个以上同时有效?如果 CS 出现两个或两个以上有效,可能发生什么情 况?(3)如果所有 CS 信号均无效,总线处在什么状态?

2 / 31

(3) A ABC ACD (C D) E A CD E

A ABC ACD (C D) E A(1 BC ) ACD (C D) E A(1 CD) ACD CDE A CD CDE A CD(1 E ) CDE A CD E

解: L ACD BCD ABCD ACD( B B) ( A A) BCD ABCD

ABCD ABCD ABCD ABCD ABCD m13 m9 m10 m 2 m15

(2) L A( B C )

L A( B C ) A ( B C ) A( BC BC ) BC ABC ABC BC ( A A) ABC A( B C ) ABC ABC ABC ABC ABC AB (C C ) AC ( B B ) ABC ABC ABC ABC ABC ABC ABC ABC ABC ABC ABC ABC m 7 m 5 m1 m 4 m 6

数电第05章锁存器和触发器(康华光)PPT课件

D Qn Qn+1 功能 0 0 0 置0 01 0

1 1

0 1

1 置1 1

简化的功能表

D

Qn+1

00

11

(1-30)

②逻辑式

Q n+1 = D

③状态转换图

D=0

D=1

0

1

D=1

2021/3/12

D=0

D Qn Qn+1 功能

0 0

0 1

0 0

置0

1 1

0 1

1 1

置1

④驱动表

Qn →Qn+1

00 01 10 11

基本R-S触发器 SD

Q & G1

导引电路

反 馈

—

Q,Q

为输出端

线

D为输入端

CP为时钟脉冲控制端

—

RD

,2—0S21D/3/分12 别为直接置0,1端

& G3 & G5

Q

& G2 RD

& G4 CP

& G6

D

(1-39)

2.逻辑功能 (1)D=0

当CP=0时

触发器状态不变

Q0

& G1

SD

1

1Q

& G2 10 RD

000 0 0 0 000 0 1 1

条件:SR=0

000 1 0 0 000 1 1 0

注意:CP=1期间Qn+1随Qn、 S、R的变化按真值表变化。 CP=0时Qn+1维持原态。

001 0 0 001 0 1

001 1 0 001 1 1

1 1

不 定

R=S=1,CP=1时: Q= —Q= 0

数字电路-康华光-05锁存器和触发器

2)逻辑符号与逻辑功能

逻辑功能表

SR

Qn

Qn?1

00

0

00

1

01

0

01

1

0

不变

1

0 置0

0

10

0

1

置1

10

1

1

11

0

不确定 不确定

11

1

不确定

SS Q

RR Q

S为置1端 R为置0端 且都是高电平有效

数字电子技术

4)工作波形(设初态为0)

画工作波形方法:

1. 根据锁存器信号敏感电平,确定状态转换时间 S S

0 G1

R

≥1

01

Q

0

G1

R

≥1

11

Q

G2 ≥1 S

1

Q0

若初态 Q n = 0

G2

≥1 S

1

Q

0

若初态 Q n = 1

数字电子技术

R=1 、 S=0

无论初态Q n为0或1,锁存器的次态为0态。 信号消失后 新的状态将被记忆下来。

1 G1

R

≥1

10

Q

1 G1

R

≥1

00

Q

G2 ≥1 S

0

Q

01

若初态 Q n = 1

开关转接A, R = 1 S =0 Q=1 S悬空时S =X R =1 Q不变

开关接 B振动

数字电子技术

2. 逻辑门控SR锁存器

电路结构 简单SR锁存器

R

G4

G2

& Q4 ≥1

Q

国标逻辑符号

E

R 1R

Q

≥1 &

《电子技术基础》考试大纲

《电子技术基础》考试大纲个人整理精品文档,仅供个人学习使用《电子技术基础》考试大纲(包括模拟电路、数字电路两部分)一、参考书目.康华光,电子技术基础——模拟部分,第五版,高等教育出版社,.康华光,电子技术基础——数字部分,第五版,高等教育出版社,二、考试内容与基本要求《模拟电子技术》考试大纲一、半导体器件结、半导体二极管、稳压二极管的工作原理;晶体三极管与场效应管的放大原理;.熟悉半导体二极管的伏安特性,主要参数及简单应用。

.熟悉稳压二极管的伏安特性,稳压原理及主要参数。

理解双极性三极管的电流放大原理,伏安特性,熟悉主要参数。

二、放大器基础放大电路的性能指标和电路组成及静态分析;稳定静态工作点的偏置电路;放大电路的动态分析,三种基本组态放大电路;场效应管放大电路性能指标分析;运算放大器放大电路性能指标分析。

.理解放大电路的组成原则。

.理解静态、动态、直流通路、交流通路的概念及放大电路主要动态指标的含义。

.熟悉放大电路的静态和动态分析方法。

掌握调整静态工作点的方法。

.掌握计算三种组态放大电路的静态工作点和动态指标。

三、放大器的频率参数频率特性的基本概念与分析方法;放大器频率分析,三极管的频率参数;共射极接法放大电路的频率特性;场效应高频等效电路,运算放大器的高频等效电路。

.理解阻容耦合共射放大电路的频率特性。

.理解三极管的频率参数。

.了解多级放大电路频率特性的概念。

四、放大电路中的负反馈负反馈的基本概念;负反馈对放大器性能的影响;深度负反馈的计算;反馈放大电路的稳定性分析。

.理解反馈,正反馈,负反馈,直流反馈,交流反馈,开环,闭环,反馈系数,反馈深度,电压反馈,电流反馈,串联反馈,并联反馈等概念。

.熟悉负反馈类型的判断。

.掌握各种基本组态负反馈对放大电路性能的影响。

1/3个人整理精品文档,仅供个人学习使用.掌握深度负反馈放大电路增益的估算方法。

五、功率放大器功率放大器的原理;互补推挽功率放大器();功率放大器的其它电路;集成功率应用电路。

《电子技术基础数字部分》第五版(康华光)第5章锁存器及触发器

R撤销后仍为0

5.2.1 SR 锁存器

RS锁存器功能表

RS 00 10 01 11

Qn+1 功能说明

Q

保持

0

置0

1

置1

d

不定

5.2 锁存器 用与非门构成的基本SR锁存器

逻辑图 逻辑符号

5.2.1 SR 锁存器

RS锁存器功能表

RS 11 01 10 00

Qn+1 功能说明

Q

保持

0

置0

1

简单SR锁存器

5.2.1 SR 锁存器

封锁概念

从另一个角度看:L = 1有效,B:控制信号, A:输入信号。 B=0,L=0(无效), 门被封锁,输入信号不能 通过; B=1,L=A ,门被打开,输入信号能通过。

使能信号 控制门电 路

E=0,G3、G4门被封锁, Q3=Q4 =0,锁存器状态不变; E=1,G3、G4门被打开, Q3=S ,Q4=R,锁存器状态随输入信号R、S变化而变化。与 简单SR锁存器功能一致。

Q功n+1能

0

保持

1

0

置0

0

1

置1

1

S信号有效,置1。 信号消失后,记忆1

5.2 锁存器 工作原理 ②. R = 1、S = 1

0

0

0

0

1

1

Q

Q

Q

≥1

≥1

≥1

R

S

R

1

1

1

R、S信号都有效后同时撤销,状态不确定。

5.2.1 SR 锁存器

0 0

Q

≥1

S 1

工作原理 QRS

0 00 1 00 0 10 1 10 0 01 1 01 0 11 1 11

康华光《电子技术基础-数字部分》配套题库-课后习题(锁存器和触发器)

图 5-9

5 / 20

圣才电子书 十万种考研考证电子书、题库视频学习平台

5.2.6 试用 1 片八 D 锁存器 74HC373 设计一个能锁存 2 位 BCD 码信号的锁存电路。

假定三态输出使能端 OE =0,锁存器原输出 Q7Q6Q5Q4=1001(9D),Q3Q2Q1Q0=0100

变。 (3)当 CP 由 1 跳变到 0 后,则再次重复(1)的过程。

5.3.2 触发器的逻辑电路如图 5-12 所示,确定其应属于何种电路结构的触发器。

7 / 20

圣才电子书 十万种考研考证电子书、题库视频学习平台

图 5-12 解:该电路是由两个逻辑门控 SR 锁存器级联构成的主从 SR 触发器。 5.3.3 触发器的逻辑电路如图 5-13 所示,确定其应属于何种电路结构的触发器。

圣才电子书 十万种考研考证电子书、题库视频学习平台

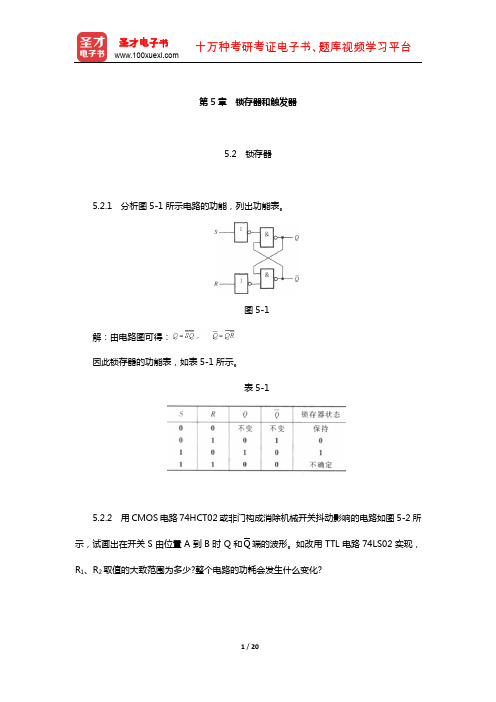

第 5 章 锁存器和触发器 5.2 锁存器

5.2.1 分析图 5-1 所示电路的功能,列出功能表。

图 5-1 解:由电路图可得: 因此锁存器的功能表,如表 5-1 所示。

表 5-1

5.2.2 用 CMOS 电路 74HCT02 或非门构成消除机械开关抖动影响的电路如图 5-2 所

示,试画出在开关 S 由位置 A 到 B 时 Q 和 Q 端的波形。如改用 TTL 电路 74LS02 实现,

R1、R2 取值的大致范围为多少?整个电路的功耗会发生什么变化?

1 / 20

圣才电子书 十万种考研考证电子书、题库视频学习平台

图 5-2

解:开关接通 A 点时,Q=0, Q=1 。当开关触点拨离 A 点瞬间,由于 Q=1 的作用,

数字电子技术基础第5章锁存器与触发器PPT课件

分立元件触发器和集成触发器。

按工作方式分类

边沿触发器和电平触发器。

触发器的工作原理

触发器在输入信号的作用下,通过内部逻辑门电路的开关特性,实现状态的翻转。

触发器的状态翻转通常发生在时钟脉冲的边沿,此时触发器的输出状态将根据输入 信号和内部状态而改变。

触发器具有置位、复位和保持三种基本功能,这些功能可以通过组合不同的逻辑门 电路来实现。

存储器

触发器还可以用于构建更复杂的存储器,如静态随机存取存储器(SRAM)等。在这些存储器中,触发器 用于存储二进制数据,并在需要时提供数据输出。

两者结合的应用实例

• 数字系统:在数字系统中,锁存器和触发器经常结合使用。 例如,在微处理器或数字信号处理系统中,锁存器和触发器 用于实现数据的存储、传输和控制。这些系统中的锁存器和 触发器通常以大规模集成(LSI)或超大规模集成(VLSI) 的形式存在。

VS

中规模集成电路

在中规模集成电路中,我们将学习一些常 见的数字集成电路,例如译码器、编码器 和比较器等。这些集成电路在数字系统中 有着广泛的应用,例如在计算机、通信和 控制系统等。我们将学习这些集成电路的 工作原理、特性和应用。

THANKS

感谢观看

04

锁存器与触发器的比较

工作原理比较

锁存器

在时钟信号的控制下,实现数据的存 储和传输。当控制信号处于高电平时 ,数据被写入锁存器;当控制信号处 于低电平时,数据保持不变。

触发器

具有记忆功能的基本逻辑单元,能够 在时钟信号的控制下,实现数据的存 储和传输。在时钟脉冲的上升沿或下 降沿时刻,数据被写入触发器。

锁存器和触发器在数字电路中有着广 泛的应用,例如在寄存器、计数器和 时序逻辑电路中。在本章中,我们学 习了这些应用的具体实现和原理。