低噪放资料

关于低噪放的研制总结

关于Ku波段PDRO锁相频率源的研制总结

新年伊始,一年之计在于春,大家都在忙着开展工作,回顾过去,展望今年,以期有个更大的提高,我这里结合今年我设计的二款低相噪频率源,针对PDRO这个专题,简要叙述一下,希望与各位共勉!

一、先介绍一下这二种频率源的设计方案和研制过程:

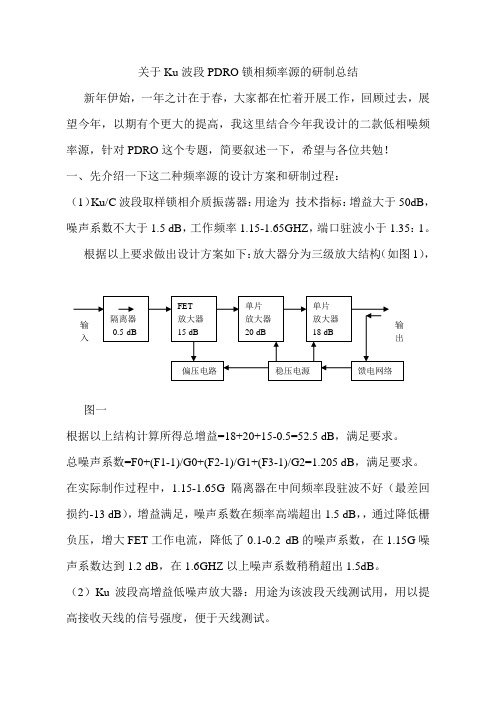

(1)Ku/C波段取样锁相介质振荡器:用途为技术指标:增益大于50dB,噪声系数不大于1.5 dB,工作频率1.15-1.65GHZ,端口驻波小于1.35:1。

根据以上要求做出设计方案如下:放大器分为三级放大结构(如图1),

图一

根据以上结构计算所得总增益=18+20+15-0.5=52.5 dB,满足要求。

总噪声系数=F0+(F1-1)/G0+(F2-1)/G1+(F3-1)/G2=1.205 dB,满足要求。

在实际制作过程中,1.15-1.65G隔离器在中间频率段驻波不好(最差回损约-13 dB),增益满足,噪声系数在频率高端超出1.5 dB,,通过降低栅负压,增大FET工作电流,降低了0.1-0.2 dB的噪声系数,在1.15G噪声系数达到1.2 dB,在1.6GHZ以上噪声系数稍稍超出1.5dB。

(2)Ku波段高增益低噪声放大器:用途为该波段天线测试用,用以提高接收天线的信号强度,便于天线测试。

技术指标:增益大于40dB,噪声系数不大于2 dB,工作频率12-16GHZ,端口驻波小于1.5:1。

根据以上要求做出设计方案如下:放大器分为三级放大结构(如图2),

图二

乔彦宾于二O一O年元月。

低噪放内部结构

低噪放内部结构摘要:一、低噪放内部结构简介1.低噪放概念2.内部结构组成二、低噪放内部结构详解1.输入匹配网络2.输出匹配网络3.噪声源4.放大器三、低噪放内部结构的作用1.降低噪声2.提高信号质量四、内部结构对低噪放性能的影响1.输入匹配网络的影响2.输出匹配网络的影响3.噪声源的影响4.放大器的影响五、结论正文:一、低噪放内部结构简介低噪放,即低噪声放大器,是一种电子放大器,主要用于放大微弱信号。

在通信系统、射频放大器、音频放大器等领域有着广泛应用。

低噪放的性能优劣,很大程度上取决于其内部结构的设计。

本文将对低噪放的内部结构进行详细解析。

二、低噪放内部结构详解1.输入匹配网络输入匹配网络是低噪放内部结构中的重要组成部分,其作用是使输入信号与放大器之间的阻抗匹配,从而提高信号传输效率,降低信号反射,减少噪声产生。

输入匹配网络通常由电感、电容等元器件组成。

2.输出匹配网络输出匹配网络的作用与输入匹配网络类似,也是为了提高信号传输效率和降低噪声。

不同的是,输出匹配网络需要将放大器的输出阻抗与负载阻抗进行匹配。

输出匹配网络通常也包括电感、电容等元器件。

3.噪声源噪声源是低噪放内部结构中产生噪声的部分。

它包括热噪声、闪烁噪声等。

噪声源的设计对于降低噪声、提高信号质量具有重要意义。

4.放大器放大器是低噪放的核心部分,负责对输入信号进行放大。

放大器的性能直接影响到低噪放的总体性能。

在设计放大器时,需要考虑其增益、带宽、噪声系数等因素。

三、低噪放内部结构的作用1.降低噪声低噪放的内部结构设计主要目的是降低噪声。

通过合理的元器件选择和参数配置,可以减少噪声源产生的噪声,降低信号反射产生的噪声,从而提高信号质量。

2.提高信号质量除了降低噪声外,低噪放的内部结构还需提高信号质量。

通过优化输入匹配网络、输出匹配网络以及放大器的设计,可以提高信号的传输效率,降低信号失真,从而提高信号质量。

四、内部结构对低噪放性能的影响1.输入匹配网络的影响输入匹配网络的设计对低噪放的性能有重要影响。

低噪放内部结构

低噪放内部结构摘要:1.低噪放内部结构的概述2.低噪放内部结构的主要组成部分3.低噪放内部结构的工作原理4.低噪放内部结构的应用领域5.低噪放内部结构的发展趋势正文:【1.低噪放内部结构的概述】低噪放内部结构,是指在电子设备中用于降低噪声、放大信号的一种电路结构。

它在各种电子设备中都有广泛的应用,如通信设备、音响设备、计算机等。

低噪放内部结构的主要作用是放大输入信号,并降低噪声,从而提高输出信号的质量。

【2.低噪放内部结构的主要组成部分】低噪放内部结构主要由以下几个部分组成:(1)放大器:是低噪放内部结构的核心部分,用于放大输入信号。

(2)滤波器:用于滤除噪声,保证输出信号的纯净度。

(3)负反馈电路:用于稳定放大器的工作状态,防止自激振荡。

(4)偏置电路:为放大器提供稳定的偏置电压,保证放大器的工作稳定性。

【3.低噪放内部结构的工作原理】低噪放内部结构的工作原理是:输入信号经过滤波器滤除噪声后,进入放大器进行放大,然后再进入滤波器滤除噪声,如此反复,直到输出信号达到所需的质量。

在这个过程中,负反馈电路和偏置电路起着关键的作用,它们可以稳定放大器的工作状态,保证输出信号的质量。

【4.低噪放内部结构的应用领域】低噪放内部结构在各种电子设备中都有广泛的应用,如通信设备、音响设备、计算机等。

在这些设备中,低噪放内部结构可以提高信号的质量,降低噪声,从而使设备能够更好地工作。

【5.低噪放内部结构的发展趋势】随着科技的发展,低噪放内部结构也在不断地发展。

未来的低噪放内部结构将会更加高效、小巧,并且能够更好地适应各种环境。

关于航天的低噪放,功放,变频器的说明

关于航天的低噪放,功放,变频器的说明摘要:1.航天领域中的低噪放、功放和变频器的作用2.低噪放的原理与技术要求3.功放的工作原理及技术指标4.变频器的功能及其在航天通信中的应用5.我国在航天电子设备领域的发展与挑战正文:航天科技在我国的发展已经取得了举世瞩目的成就,其中航天电子设备的技术水平在很大程度上决定了航天器的性能。

在航天领域中,低噪放、功放和变频器等电子设备起着关键作用。

首先,低噪放(Low-Noise Amplifier, LNA)是一种用于放大微弱信号的电子器件。

在航天通信系统中,低噪放被广泛应用于卫星接收地面站发射的微弱信号。

其原理是在放大信号的同时,降低噪声的干扰,从而提高信号质量。

低噪放的技术要求主要包括低噪声系数、高增益、高线性度等。

其次,功放(Power Amplifier, PA)是一种能够将输入信号的功率放大到较高水平的电子设备。

在航天通信系统中,功放用于驱动卫星发射天线,从而实现地面站与卫星之间的通信。

功放的工作原理主要是通过控制输入信号的幅度和相位,使得输出信号具有所需的功率。

功放的技术指标主要包括输出功率、增益、效率、线性度等。

再者,变频器(Frequency Converter, FC)是一种能实现信号频率转换的电子设备。

在航天通信系统中,变频器用于实现不同频段之间的信号传输。

例如,将C 波段信号转换为Ku 波段信号,以提高信号传输的效率。

变频器的功能主要包括频率变换、信号放大、滤波等。

我国在航天电子设备领域已经取得了显著的成就,但在低噪放、功放和变频器等核心技术的研发方面,与国际先进水平仍存在一定差距。

低噪放

(一) 国际发展现状

国际上的一些著名大学、研究机构以及 IC公司都己对多模多频段低噪声放大器的设 计做了广泛的研究,并且己经有了相当多的 成果。 2011年8月,日本的Lime Microsystems 公司推出了一款多模多频无线收发芯片 LMS6002,该芯片的工作频率为375MHz--4GHz,可用于3GPP ( WCDMA,HSPA和LTE), 3GPP2 (CDMA2000)以及WiMAX的应用上,其低噪声放大器的噪声系数不超过3dB。 2012年3月,富士通半导体公司推出了单芯片的2G13G/4G收发芯片MB86L1A,该芯 片支持LTE ( FDD和TDD), EDGE, EDGE-EVO, WCDMA,GSM, HSPA+, CDMA以及TD-SCDMA等多 种通信模式。 2013 年1 月,MTK 推出MT3332/MT3333 SoC(片上系统)芯片如图所示,可支持 GPS、北斗、GLONASS、伽利略及QZSS 等5 种全球卫星导航系统的信号,藉由多系统的 相互辅助,能大幅提升导航定位的精度和可靠性,避免误差随时间推移及行程增加而 累积。

传统的单频段LNA技术已趋于成熟,具有源级电感负 反馈结构的LNA由于其低噪声低功耗的特点而得到广泛应 用。 但是,面对多模多频段的需求,基于这种结构的LNA 设计遇到新的困难。首先,其窄带的输入阻抗匹配特点。 源级电感退化LNA输入阻抗只匹配在一个频点上,而多模 多频段需要低噪声放大器在多个频段都能实现匹配。虽然 二阶乃至高阶的输入阻抗匹配以及负载谐振网络能够支持 相隔比较远的两个或多个频带的低噪声放大,但是其在低 噪声放大方面的优势被削弱。

(一) 国际发展现状

2013 年11 月,高通与三星合作推出支持北斗卫星定位功能的旗舰智能手机 GALAXY Note 3(配备高通骁龙800 移动处理器MSM8974),成为首批支持北斗系统 的智能手机。 2013 年12 月,博通公司宣布推出一款支持北斗系统的卫星导航芯片BCM47531 (见图6),它能够同时使用从5 个卫星系统(GPS、GLONASS、QZSS、SBAS 和北斗 卫星)发出的信号来产生定位数据,提高 了导航定位精度,尤其是在性能受建筑和 掩体影响的城区,效果更为明显。 2014 年2 月,MTK 发布了全球首款支 持4G LTE 网片——MT6630,支持20/40/80 MHz 频道带宽,支持低功耗蓝牙,整合了 ANT +(蓝牙健康与健身聚合器套件)技 术,可广泛应用于运动健身配件/ 可穿戴 设备,同时支持GPS、北斗、GLONASS、 伽利略、QZSS 系统。

低噪放的优化技术

CMOS射频集成电路设计2009年4月1日唐长文副教授zwtang@/Courses.htm复旦大学专用集成电路与系统国家重点实验室版权©2005-2009, 版权所有,侵犯必究低噪声放大器的设计优化技术z MOS管噪声模型z经典二端口网络的噪声分析z窄带低噪声放大器的设计优化经典二端口网络噪声匹配噪声和阻抗同时匹配有效跨导约束和功率约束的噪声匹配功率约束的噪声和阻抗同时匹配(自学)z宽带低噪声放大器的设计优化噪声抵消技术电容交叉耦合技术电阻负反馈技术复旦大学专用集成电路与系统国家重点实验室唐长文电阻热噪声唐长文bulkbulkkTR243γ=≈( g−2 ndcopt minin m m g m S 2G R g L =S l gndg do减小时,宽W减小,电容C gs减小,要使输入回路的谐振频率保持不变,L必须相应增大。

g为了得到好的噪声性能和降低功耗,需要提高输入串联回路值。

的QL增大ωT/ω0值能够减小噪声系数NF,因此CMOS工艺的不断不断提高对降低噪声系数有一定的好处。

进步,ωT噪声系数NF没有最小极限值。

很小的MOS管,消耗极少量的功率就能够获得0dB的噪声系数。

这和实际测试结果是不符的,造成这种问题的原因在于没有考虑MOS管的栅极感应噪声。

复旦大学专用集成电路与系统国家重点实验室唐长文ngngungu nd ()ngu ndd m D L TDmmDDD2nd 专用集成电路与系统国家重点实验室2nd 专用集成电路与系统国家重点实验室宽带低噪声放大器的设计优化z噪声抵消技术单端单端转差分z电容交叉耦合技术z电阻负反馈技术复旦大学专用集成电路与系统国家重点实验室唐长文A Wide-band CMOS Low-Noise Amplifier for TV Tuner Applications Youchun Liao, Zhangwen Tang and Hao Min ASIC & System State Key Laboratory, Fudan UniversityShanghai, 201203 P.R.COutlinez CMOS TV tuner architecture and the demand for wide-band LNAz LNA with noise-canceling technique –Basic principle–Noise analysis–Linearity analysis–Parameter relationshipz Chip and measurementz ConclusionCOB PackageNo extra matching-network neededConclusionz A LNA with noise-canceling technique z Noise canceling under input/output impedance matchingz Linearity analysisz Relationship of characteristics depend on RFz Chip and measurement results。

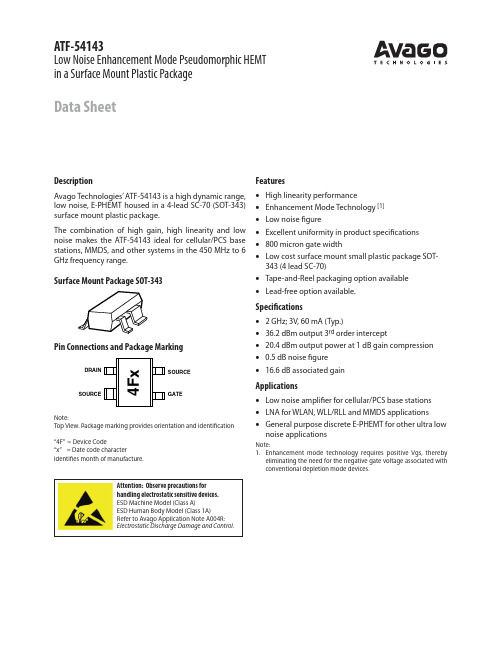

atf-54143低噪放芯片资料

Surface Mount Package SOT-343

Specifications

2 GHz; 3V, 60 mA (Typ.) 36.2 dBm output 3rd order intercept 20.4 dBm output power at 1 dB gain compression 0.5 dB noise figure 16.6 dB associated gain

Pin Connections and Package Marking

4Fx

DRAIN

SOURCE

Applications

GATE

SOURCE

Note: Top View. Package marking provides orientation and identification “4F” = Device Code “x” = Date code character identifies month of manufacture.

ቤተ መጻሕፍቲ ባይዱ

Parameter and Test Condition

Operational Gate Voltage Threshold Voltage Saturated Drain Current Transconductance Gate Leakage Current Noise Figure[1] Associated Gain[1] Output 3rd Order Intercept Point[1] 1dB Compressed Output Power[1] f = 2 GHz f = 900 MHz f = 2 GHz f = 900 MHz f = 2 GHz f = 900 MHz f = 2 GHz f = 900 MHz Vds = 3V, Ids = 60 mA Vds = 3V, Ids = 4 mA Vds = 3V, Vgs = 0V

低噪放Word

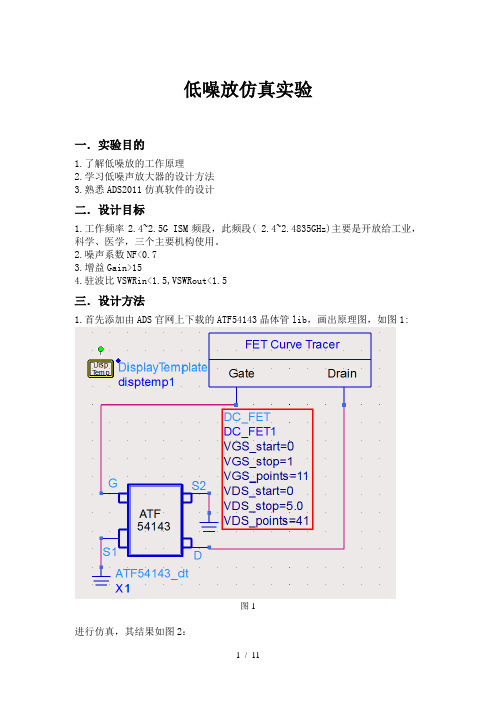

低噪放仿真实验一.实验目的1.了解低噪放的工作原理2.学习低噪声放大器的设计方法3.熟悉ADS2011仿真软件的设计二.设计目标1.工作频率2.4~2.5G ISM频段,此频段( 2.4~2.4835GHz)主要是开放给工业,科学、医学,三个主要机构使用。

2.噪声系数NF<0.73.增益Gain>154.驻波比VSWRin<1.5,VSWRout<1.5三.设计方法1.首先添加由ADS官网上下载的ATF54143晶体管lib,画出原理图,如图1:图1进行仿真,其结果如图2:图22.偏执电路设计从ATF54143数据手册中得Fmin 接近最小值,增益大约为16.3dB ,所以晶体管的直流工作点就设为V 3=ds V ,mA 20=ds I 。

然后画偏执电路,设置参数Vdd=5V ,Vds=3V ,Ids=20mA ,增加DC 模块,可看到仿真结果如图4:图4参考值Vds=3V ,Id=40mA ,仿真做出来Vds=3.11V ,Id=37.7mA ,存在误差。

3.稳定性分析新建原理图如图5:图5设置好参数后仿真,添加MaxGain1和Stabfact1两条曲线,如图6:图6观察到最大增益为19.811dB,稳定系数为0.897,小于1,而只有系数大于1时才是稳定,所以不稳定。

使用负反馈可以让系统稳定,在源极添加小电感作为负反馈,如图7:图7仿真结果如图8:图84.DC_Feed改成实际器件添加murata的lib,用murata里的LQG18和GRM18代替DC_Feed。

电路如图1.9:图9其中设置旁路电容为 1.2pF ,旁路电感为 3.9nH ,输出端的电路串联电感值为22nH ,旁路电容为10pF ,分装都是0603。

仿真图如图10:图10然后将晶体管源极的两个电感换成微带线。

计算公式如下:rZ L l ε081.11=,其中L 为电感值,Z0为特征阻抗,这里用的PCB 板是FR4射频板。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

低噪放培训材料

1、低噪放的组成及其工作原理。

2、低噪放性能指标的分析。

3、典型低噪放电路图讲解。

4、电路的调试及维修。

1.1、低噪放的作用

所谓低噪放就是噪声系数很低的放大器,它位于射频接收链路的第一级。

射频接收

系统的一个基本设计目标就是要让整个接收链路的噪声系数最小。

而整个接收链路的很大基本由第一级放大器决定。

第一级放大器的噪声系数越小,增益越大则整个接收链路的噪声系数就越小。

而噪声系数的大小直接影响到接收机的灵敏度的好坏。

目前公司低噪放设计采取两种方案: 1、平衡式(早期)

2、单链路式(降成本)

模块类型: 1、单入单出 2、单入双出

1.2、低噪放的组成部分

该电路可划分为三个小单元:电源处理电路、CPU 处理电路、射频(RF)链路。

● 实现与上位机的RS485通信接口、输入信号功率检测、模块增益调节和自动电平控

制(ALC)。

● 变频器的基本组成部分 ● 低噪放方框示意图:

1.3、低噪声设计部分

● 系统总的噪声系数可以通过单级噪声系数和增益计算。

● 根据噪声系数的级连公式:

Fsys=F1+(F2-1)/G1+(F3-1)/G1G2+...(Fn-1)/G1G2...Gn-1

(其中Fsys 为n 级串联成的系统的总噪声系数、Fn 为第n 级的噪声系数、Gn 为第n 级的增益。

)

R F O U T

d e t e c t o r

由此可见,整个放大器的噪声系数主要由第一级和第二级所决定。

具有低噪声和高增益的第一级和第二级放大器的设计是整个低噪声放大器设计的难点。

所以,各类低噪放模块在第一级采用噪声系数好的放大器,ALC 限制必须放在第二级放大器后面.

1.4、ALC 部分

● 所谓的ALC 就是自动增益电平控制 ,是针对由于器件本身变化,环境引起工作点变

化等,在电路中加入的稳定电平的电路.在一定范围内,ALC 电路自动纠正偏移的电平回到要求的数值。

● ALC 在低噪放上的应用:调整低噪声放大器的增益,在保证信噪比的情况下,自动调

整接收通道的增益,使得在大信号电平环境下接收机不至于饱和造成性能下降,小信号的时候又能保证信噪比并能正确的解调。

防止输入信号过大,从而限制功放的输出功率,保证线性指标不会恶化的同时避免过大的激励使功放损坏。

1.4.1、ALC 实现电路 ● ALC 实现电路框图:

1.5、ATT 和输入功检的实现

ATT 的实现:

ATT 的实现主要是有数控衰减芯片实现,有串行和并行控制两类芯片。

目前低噪放采用的并行芯片HMC273,通过设置各控制脚位高低电平进行控制。

(另外,比如衰减器采用串行芯片PE4306)。

输入功检实现方法:

由于对成本的考虑,输入功检的实现数据直接由末级输出功检采集。

通过采集到输出信号功率扣掉模块增益从而得到模块的输入功率。

(当ALC 起控或ATT 由衰减时,cpu 会相应将该数据进行运算处理)

提纲

1、低噪放的组成及其工作原理。

2、低噪放性能指标的分析。

3、典型低噪放电路图讲解。

A D 8314

4、电路的调试及维修。

3.1、低噪放链路前级链路

3.2、 ATT电路

3.3、 ALC及功检电路

4、电路调试及维修

①电路调试:

调试过程是射频电路设计中极其重要的环节,也是电路设计的难点问题。

通过测试仪器观察并完成各级电路的性能改善。

调试前准备:

1、首先,判断模块电流是否正常;(排除短路、虚焊等现象)

2、其次,程序的烧写;(CPU,RS-485通信是否正常)

完成这几个步骤就可以开始进行指标的测试。

调试步骤:(针对生产模块)

可以通过频谱仪测量的指标:

1、增益测试,(基础,必须增益测试正常后方可进行下一步测试,增益出现异常时,应逐级排查)

2、三阶互调测试,(确保信号源自身互调较指标好上-5dBc,当该指标恶化时,应逐级排查);

3、ATT测试;

4、带内平坦度测量;

5、锁上盖板,进行带内杂散发射测量,输入功检测量;

●反映变频器性能的主要指标测试:

可以通过矢量网络分析仪测量的指标:

带内平坦度

可以通过频谱仪测量的指标:

增益

三阶互调

杂散发射

ATT

功率检测

几款常用低噪声放大管

ATT衰减芯片

并行

串行。