Altera提供经过全面验证的EtherCAT协议IP,前端许可免费

Altera发布通过AQEC认证的FPGA

加入 A C工作组是Ak r O S QE e a C T  ̄强策略的关键一 步。 该策略包括提供支持更广 阔温度 范围的器件 、 管芯业务

支持 、长期 过 时 保 护 以及 连 续 供 应 链 等 。Srt P A 系 tai F G x

讲解特点及使用方法 。

T PC m的双模协议栈 已经集成 到多个芯 片供应商 的多种 T O

平台上 ,并 已经可 以开 放授 权使 用 。 T PC m在开发 和授 权使 用3 M系 列设备的协议软 T O GS 件方 面巳拥有 十多年的经验 ,使其能够开 发出高效 且占用 很少 存储 器空 间的蜂窝 电话协议栈 。其一 致的代码 库也 巳 发展成 包含GS M、G R 、 DG W C MA和 HS A协 P S E E、 D DP 议,并 正向覆 盖 HS A和 L E扩充 。 UP T Asse utk表示 ,基 于 T PC m G协 议栈编译 软件和 T o 3 微软集成代码进行的软件开发为他们的整个3 G手机发展路 线图提供 了一 个极好的基础 ,而且它 紧凑 并占用很 小存储

平台数 量。

列的数 字信号处理( P 性能和密度特性 ,以及 C co e DS ) y ln F GA系列的低成本 和低功耗特 性 , P 使军事和航空航天领域 的制 造商能够 以更低的 风险开发高度可靠的设计。 tr的 Al a e Srt I C co e I F GA,以及 MAX I C L 目前 tai I和 y ln I P x I P D 正在 申请 AQ C认证 。 tai IF G E S rt I P A使用了 1 8 x 2 位高级 加密标准( S设计安全密钥 ,支持防篡 改设 计安全特性 。 AE )

Altera三速以太网IP核使用(上篇)之快速仿真

Altera三速以太⽹IP核使⽤(上篇)之快速仿真对于⽐较⾼级的ip核,altera⼀般都会提供仿真案例,⽹上有关于这个IP核的各种仿真⽅法,但都⽐较繁琐,前⼏⽇,朋友跟我分享了⼀个⽐较快速⾼效的仿真⽅法,这个⽅法也是他摸索折腾了⼀段时间才总结出来的,在此,也谢谢他这种毫⽆保留的分享奉献精神,估计此套⽅法可以针对Altera 的⼤多数复杂ip核仿真。

新建⼯程,⽣成ip核的步骤我就省略了,直接进⼊ip核调⽤仿真部分。

在⽣成的⼯程⾥找到“testbench”⽂件夹,⾥⾯有⼀个README.txt,打开按照⾥⾯的步骤操作即可。

根据上⾯的步骤,⾸先是打开“testbench”⽂件夹⾥的"generate_sim.qpf"⼯程然后运⾏ “generate_sim_verilog.tcl”或者“generate_sim_vhdl.tcl”,到这⾥可以关闭quartus这个⼯程了,然后去打开modelsim,将路径“Change Directory”到“run_irene_tb.tcl”所在的路径接着在modelsim运⾏命令框输⼊“do run_irene_tb.tcl”,按回车键接下来就不⽤⼈为⼲预了,modelsim 会⾃动执⾏直到仿真波形⾃动输出可以重点关注下它的“control interface”时序以及它的⽤户侧时钟,MAC IP的⼯作时钟。

⾄于control interface接⼝时序⽐较简单,通过仿真我们可以看到在waitrequest拉低的时候可以进⾏读写操作。

接下来简单说⼀下它的⼯作时钟:1)ff_tx_clk:⽤户侧发送端时钟,2)ff_rx_clk:⽤户侧接收端时钟;MAC IP核⼯作时钟是125M,接⼝是8 bit,但是由于IP核内部fifo的隔离,因此ff_tx_clk与ff_rx_clk⽆须配置为125M,只要满⾜125M X 8bit = 1G的速率即可。

MegaWizardPlug-In工具生成altera三速以太网IP核并编译仿真

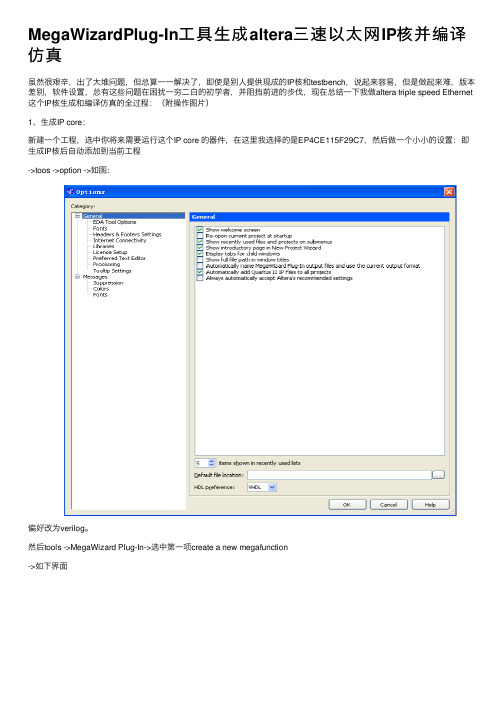

MegaWizardPlug-In⼯具⽣成altera三速以太⽹IP核并编译仿真虽然很艰⾟,出了⼤堆问题,但总算⼀⼀解决了,即使是别⼈提供现成的IP核和testbench,说起来容易,但是做起来难,版本差别,软件设置,总有这些问题在困扰⼀穷⼆⽩的初学者,并阻挡前进的步伐,现在总结⼀下我做altera triple speed Ethernet 这个IP核⽣成和编译仿真的全过程:(附操作图⽚)1、⽣成IP core:新建⼀个⼯程,选中你将来需要运⾏这个IP core 的器件,在这⾥我选择的是EP4CE115F29C7,然后做⼀个⼩⼩的设置:即⽣成IP核后⾃动添加到当前⼯程->toos ->option ->如图:偏好改为verilog。

然后tools ->MegaWizard Plug-In->选中第⼀项create a new megafunction->如下界⾯注意⼀般应⽤IP核选择第⼀项Installed Plug-Ins,不要选中第⼆项IP MegaStore,原因在于第⼆项中多是altea合作伙伴开发的IP核,⼀般需要license 才能仿真试⽤,⽐较⿇烦,第⼀项⼏乎全都是随quartus II装好的IP核,所以可以⽀持opencore-plus功能,这样⽅便试⽤和仿真,只要通过下载电缆和相应⽀持的开发板连接就可以再开发板上⾯运⾏IP核,⼀般⽀持1⼩时的有效时间,已经够⽤。

接下来指定IP核输出路径,并指定IP核⽂件输出名称(加在路径后⾯),例如命名为tri_megacore,点击next->如图是我的设置,因FPGA内部MAC与PHY连接接⼝选⽤RGMII,故选⽤该设置,使⽤内部FIFO,点击next->⼀般按照默认设置既可,因仿真或者设计需要,另外选中第⼆项、第四项(包括64-bit counter)、第七项,同时选中包含MDIO module,将时钟分频改为50,MAC使⽤125MHz时钟,分频50得到2.5MHz时钟,极为MDIO的⼯作时钟。

第四章 Altera 的IP工具

片内存 储器

在FPGA中,片内存储器是十分重要的资源。利用 片内存储器,可以在FPGA中实现RAM、ROM、 CAM等存储单元。存储单元的设计有其自身的规 律和特点: RAM是根据地址读、写数据的存储单元; 在FPGA中没有专用的ROM硬件资源,实现ROM 的方法是:对RAM赋初值,并保持该初值; CAM和RAM恰恰相反,它返回的是与端口数据相 匹配的内部地址。CAM的应用非常广泛,如在路 由器中的地址表等。

硬核

硬核在EDA 设计领域指经过验证 的设计版图;具体在FPGA 设计中指 布局和工艺固定、经过前端和后端验 证的设计,设计人员不能对其修改。 不能修改的原因有两个:首先是系统 设计对各个模块的时序要求很严格, 不允许打乱已有的物理版图;其次是 保护知识产权的要求,不允许设计人 员对其有任何改动。IP 硬核的不许 修改特点使其复用有一定的困难,因 此只能用于某些特定应用,使用范围 较窄。

例 FIFO

1 调用MegaWizard 管理器 Tools MegaWizard Plug-In Manager

2 宏功能模块选择

输出语言的选择 可供选 择的宏 功能 输出文件路径和文件名

白盒 模式

用户库

3 F件选择

MegaWizard输出的文件类型

Altera的IP工具—MegaWizard管理器

MegaWizard管理器可以帮助用户建立或修改包含自定义宏功 能 模块变量的设计文件,而后可以在用户自己的设计文件中对这 些IP模块文件实例化。通常这些自定义宏功能模块变量基于 Altera提供的基本宏功能、MegaCore以及AMPP IP核。通过 运 行向导,MegaWizard管理器能帮助用户方便的为自定义宏功 能 模块变量指定选项,产生所需功能。 缺省状态下,MegaWizard输出HDL 封装文件,同时还提 供 HDL实例化模块、VHDL元件声明(CMP)、Quartus II符号

合信 ethercat设定方法

合信ethercat设定方法合信是一款以太坊上的去中心化应用(DApp),为用户提供了一个安全、不可变的信任框架。

本文档将详细介绍如何设置合信的方法,帮助用户轻松开始使用和体验合信的功能。

1. 了解合信2. 下载并安装合信应用程序3. 创建合信账户4. 导入/导出合信账户5. 设置合约管理6. 添加信任人1. 了解合信:合信是基于以太坊区块链技术的去中心化应用程序,通过智能合约实现信任的建立和管理。

合信的核心功能包括创建和分享信任合约,验证和记录信任的行为,以及提供信任评估和奖励机制。

2. 下载并安装合信应用程序:在手机应用商店搜索“合信”并下载安装应用程序。

也可以在合信官方网站上找到相应的下载链接并进行安装。

3. 创建合信账户:打开合信应用程序,并点击“创建账户”。

根据提示,输入个人信息并设置密码来创建一个新的合信账户。

确保密码强度足够高,以确保账户的安全性。

4. 导入/导出合信账户:如果您已经在其他设备上创建了合信账户,可以通过“导入账户”选项将其导入到当前设备。

在合信应用程序中选择相应选项,并按照提示执行相应步骤。

另外,如果您希望在不同设备之间迁移合信账户,可以选择“导出账户”选项,生成一个安全的备份文件。

将备份文件保存在安全的地方,并在另一设备上选择“导入账户”,并使用备份文件进行恢复。

5. 设置合约管理:在合信应用程序中,点击“合约管理”选项,并进入合约管理页面。

在此页面,可以查看已创建的合约,添加新的合约,以及设置合约的属性和权限。

5.1 查看已创建的合约:在合约管理页面,可以查看已创建的合约并了解其基本信息。

可以查看合约的名称、地址、创建者、创建时间等重要信息。

5.2 添加新的合约:点击“添加合约”按钮,根据提示填写合约的相关信息。

包括合约名称、参与方信息、合同条款等。

在合约创建成功后,将在合约管理页面看到新添加的合约。

5.3 设置合约属性和权限:在合约管理页面,可以编辑已创建的合约的属性和权限。

ALTERA阿尔特拉代理

万联芯城-电子元器件采购网专业一站式配单业务,满足终端客户的物料需求,节省采购成本,万联芯城优势供应ALTERA原装进口芯片,价格便宜,质量优秀,采购电子元器件就上万联芯城!点击进入万联芯城ALTERA代理,阿尔特拉代理公司是美国可编程逻辑器件(PLD)制造商,可重构复杂数字电路。

[1] ALTERA代理,阿尔特拉代理于1984年发布了个PLD。

[2] ALTERA代理,阿尔特拉代理的主要产品是Stratix,Arria和Cyclone系列FPGA,[1] MAX系列CPLD,[1] Quartus II设计软件,[3] [4]和Enpirion PowerSoC DC-DC电源解决方案。

ALTERA代理,阿尔特拉代理和英特尔于2015年6月1日宣布,他们已同意英特尔将以全部现金交易收购ALTERA代理,阿尔特拉代理,价值约为167亿美元。

[5] 截至2015年12月28日,收购已完成。

Stratix系列FPGA是ALTERA代理,阿尔特拉代理大,带宽高的器件,具有高达110万个逻辑单元,高达28 Gbit / s的集成收发器,高达1.6 Tbit / s的串行开关能力,高达1,840 GMAC的信号处理能力性能,以及800 MHz时多7 x72 DDR3内存接口。

[8] Cyclone系列FPGA 和SoC FPGA是ALTERA代理,阿尔特拉代理成本低,功耗低的FPGA,其变体提供高达5 Gbit / s的集成收发器。

在这两个器件系列之间是Arria系列FPGA,可为中端应用(如远程无线电头,视频会议设备和有线接入设备)提供性能,功耗和成本之间的平衡。

Arria FPGA 集成了高达10 Gbit / s的收发器。

自2012年12月以来,ALTERA代理,阿尔特拉代理一直在发售SoC FPGA 器件。

[9] 根据ALTERA代理,阿尔特拉代理的说法,完全耗尽的绝缘体上硅(FDSOI)芯片制造工艺对FPGA是有益的。

第6章Altera公司FPGA的配置

图6.4 JTAG模式单个器件的配置电路

(1)JTAG模式单个器件的配置电路设计

图6.4中,器件的配置是通过JTAG引脚端TCK、 TMS、TDI和TDO完成的。上拉电阻应该连接到电 缆的电源,APEX20KE、APEX20KC系列器件所有的 上拉电阻均为10kΩ。采用144引脚TQFP封装的 FLEX10K器件没有TRST信号脚,此时TRST信号可 以忽略。nCONFIG、MSELO、MSEL1引脚端应采用 支持非JTAG配置模式的方式连接,如果仅仅使用 JTAG配置模式,则nCONFIG引脚端应连接到VCC, MSELO和MSELI引脚端应连接到地。 MasterBlaster电缆驱动器的参考电压VIO应与器 件的VCCIO匹配。

ByteBlaster与PC机并口相连的是25针插头,在PS模 式下和在JTAG模式下的引脚信号名称是不同的,如表6.1 所示。

图6.1 ByteBlaster与PC并口连接示意图

ByteBlaster与FPGA应用电路PCB电路板相连 的是10针插座,在PS模式下和在JTAG模式下的引 脚信号名称如表6.2所示。注意:PCB板必须给下 载电缆提供电源VCC和信号地GND。

(3)电缆线

ByteBlaster的电缆线一般使用扁平电缆, 长度不超过30cm,否则带来干扰、反射及信号过 冲问题,引起数据传输错误,导致下载失败。如 果PC机并行口与PCB电路板距离较远,需要加长 电缆,则可在PC机并行口和ByteBlaster电缆之 间加入一根并行口连接电缆。

(4)PCB电路板上的10针连接插头

第一部分 EtherCAT 协议系统整体组成

从站控制器:从站控制器(ESC)主要有 ASIC 芯片、IP-Core 和 ESC20。ASIC 芯片主要由德国倍福公司提供,主要有 ET1100 和 ET1200 ;IP-Core 可以从德国倍福公司、Xilinx 公司和 Altera 公司获得。每种形式的ESC都由MII/EBUS接口、逻辑管理单元 FMMU(Fielldbus MemoryManagement Unit)、同步存储管理 SM(SyncManager)、双端口 RAM、分布时钟、过程数据 PDI(Process Data Interface)接口等组成

第一部分 EtherCAT 协议系统整体组成

德国倍福公司提出了以太网控制自动化技术,即 EtherCAT 技术,在数据链路层使用实时性调度的软核,并采用了双端口 RAM 传输过程数据传输,提高了系统的实时性. 主站由带有普通网卡的计算机组成,主要负责向从站的发送 EtherCAT 数据帧,从而进行与从站的互动。主站向从站发送数 据帧经过所有的从站设备,每个从站设备在数据帧经过时,处理寻址到本站的数据,根据报文头中的命令从报文中指定的位置 读或写数据,并且从站硬件把该报文的工作计数器(WKC)加 1,表示该 数据被从站处理;数据帧访问完整个系统的最后一个从站时,该从站把经过处理的数据帧发送给主站。主站收到从站处理的 数据帧后(10G 以太网)

2 EtherCAT 协议系统从站组成

从层次上划分,EtherCAT 协议一般划分为三层,即物理层、数据链路层和应用层;其中,物理层的主要器件有物理层 PHY(Port Physical Layer)芯片、网络变压器和 RJ45 接口组成。数据链路层的主要器件是 ESC(EtherCATSlave Controller)专用器件。应用层主要根据需要选择合适的微处理器芯片 ESC 物理层使用的接口模式分为两种:一种是 MII (Media IndependentInterface)接口,另一种是 EBUS 接口。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Altera 提供经过全面验证的EtherCAT 协议IP,前

端许可免费

2013 年7 月30 号,北京Altera 公司(NASDAQ:ALTR)今天宣布,开始为Altera FPGA 提供经过全面验证的EtherCAT(控制自动化技术以太网)协议知识产权(IP)。

此次发布是Altera、EtherCAT 技术集团(ETG)以及SofTIng 工业自动化有限公司合作推出最新产品,其许可结构支持开发

人员使用前沿的工业以太网协议,而且没有前端许可费用,没有单片版税报

告或者延期协商,最终简化了基于FPGA 的工业以太网设计集成。

Altera 工业业务部总监Brian Jentz 评论说:客户一直希望能够在FPGA 中发挥EtherCAT 协议IP 的性能优势,但总是受到许可成本的限制。

通过消除这一障碍,Altera 客户可以发挥这一性能优势,以很少的投入,充

满信心的在现有FPGA 中集成分立EtherCAT 器件。

Altera 的工业以太网解决方案使用可编程逻辑和软核嵌入式处理器,在一片FPGA 中实现了协议IP 和软件堆栈。

通过这种方式,具有相同Altera FPGA 的一块电路板能够适应多种协议,不需要改动硬件。

相同的FPGA 还能够用于实现各种工业自动化功能,例如,传感器接口、加速器和定制控制

逻辑,以及通信功能等。