CMOS集成电路设计第一、二章作业

CMOS模拟集成电路习题集1

目录例1:估算参数的求取_________________________________________________________2 例2:单级CS放大器的设计——————————————————————————6 例3:单级CS-CG放大器的设计———————————————————————12 例4:基本差分对(图4.1)设计————————————————————————16 例5:套筒式(Cascade)放大器的设计—————————————————————24 例6:基本无缓冲两级运放设计————————————————————————33 例7:高增益无缓冲运放设计—————————————————————————49 例8:高增益、高CMRR无缓冲运放设计———————————————————64例9:β乘法型参考电压源——————————————————————————91例1:估算参数的求取1.Kn 、Kp 的求取图1.1表1.1 思考题1.1:从表1.1中可以看出沟道调制效应系数λ是否为常数?为什么?.上试中:22ox n(p)D on DS onn(p)n(p)μC W W I =V (1+λV )=K V 2L L oxn(p)DS n(p)μC (1+λV K =)22.λn、λp的求取图1.2图1.3图1.4表1.2*比较上面求得的λn、λp与上学期所学教材中λ∝1/L的差异。

MOSFET的简化版图如图1.5所示,其中L1表示MOS管源漏区接触孔与多晶硅之间的最小距离,L2表示接触孔的最小尺寸,L3表示接触孔与源漏区边缘间的最小距离。

寄生电容可按表1.3估算:图1.5表1.3 MOS管寄生电容的计算公式MOSFET的寄生电容C GS C GD C DB(C SB)饱和区C GSO W eff +0.67 C OX W eff L eff C GDO W eff WE C j +2(W+E) C jsw 表1.3中E=L1 + L2 + L3 , L1、L2、L3这些规则尺寸可以很容易在技术资料上找到(对于“懒惰”的工程师们而言,一个也许更高效的办法是从晶元厂提供的版图库中直接通过测量获得)。

拉扎维模拟CMOS集成电路设计第二章作业答案详解完整版中文

IX

1 2

nCOX

W L

[2 0.2(VX

1) (VX

1)

2

]

1 2

nCOX

W L

(1.4 VX )(VX

1)

gm

nCOX

W L

VDS

nCOX

W L

(Vx

1)

Copyright for zhouqn

③ 当VX≥1.2V时,MOS管工作在饱和区

IX

+

IX

1 2

nCOX

IX

1 2

PCox

W L

(0.1)2

gm

PCox

W L

(0.1)

+ 1.9V

-

② 当1.8V<VX≤1.9V时,MOS管工作在线性区

IX

1 2

PCox

W L

[2 (0.1) (VX

1.9) (VX

1.9)2 ]

gm

PCox

W L

(VX

1.9)

Copyright for zhouqn

第二章 作业答案

Copyright for zhouqn

2.1、W/L=50/0.5,假设|VDS|=3V,当|VGS|从0上升到 3V时,画出NFET和PFET的漏电流VGS变化曲线

解:

a) NMOS管: 假设阈值电压VTH=0.7V,不考虑亚 阈值导电

① 当VGS<0.7V时,NMOS管工作在截止区,则ID=0 ② 当VGS>0.7V时, NMOS管工作在饱和区,NMOS管

0 8.854 1012 F / m sio2 3.9

集成电路版图设计习题答案第二章集成电路制造工艺

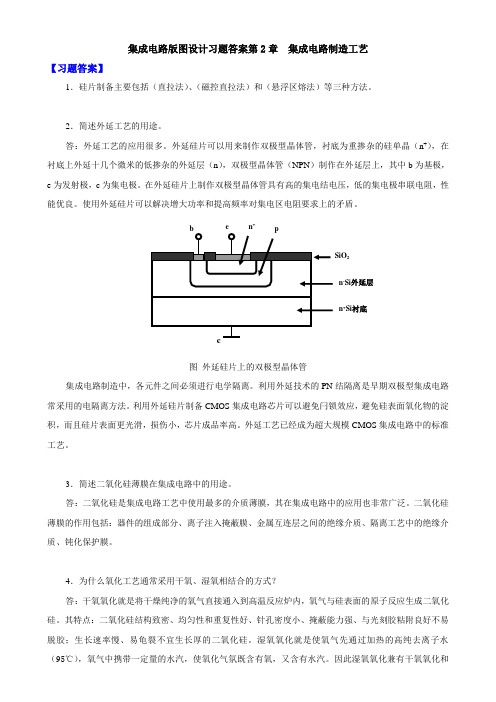

集成电路版图设计习题答案第2章 集成电路制造工艺【习题答案】1.硅片制备主要包括(直拉法)、(磁控直拉法)和(悬浮区熔法)等三种方法。

2.简述外延工艺的用途。

答:外延工艺的应用很多。

外延硅片可以用来制作双极型晶体管,衬底为重掺杂的硅单晶(n +),在衬底上外延十几个微米的低掺杂的外延层(n ),双极型晶体管(NPN )制作在外延层上,其中b 为基极,e 为发射极,c 为集电极。

在外延硅片上制作双极型晶体管具有高的集电结电压,低的集电极串联电阻,性能优良。

使用外延硅片可以解决增大功率和提高频率对集电区电阻要求上的矛盾。

图 外延硅片上的双极型晶体管集成电路制造中,各元件之间必须进行电学隔离。

利用外延技术的PN 结隔离是早期双极型集成电路常采用的电隔离方法。

利用外延硅片制备CMOS 集成电路芯片可以避免闩锁效应,避免硅表面氧化物的淀积,而且硅片表面更光滑,损伤小,芯片成品率高。

外延工艺已经成为超大规模CMOS 集成电路中的标准工艺。

3.简述二氧化硅薄膜在集成电路中的用途。

答:二氧化硅是集成电路工艺中使用最多的介质薄膜,其在集成电路中的应用也非常广泛。

二氧化硅薄膜的作用包括:器件的组成部分、离子注入掩蔽膜、金属互连层之间的绝缘介质、隔离工艺中的绝缘介质、钝化保护膜。

4.为什么氧化工艺通常采用干氧、湿氧相结合的方式?答:干氧氧化就是将干燥纯净的氧气直接通入到高温反应炉内,氧气与硅表面的原子反应生成二氧化硅。

其特点:二氧化硅结构致密、均匀性和重复性好、针孔密度小、掩蔽能力强、与光刻胶粘附良好不易脱胶;生长速率慢、易龟裂不宜生长厚的二氧化硅。

湿氧氧化就是使氧气先通过加热的高纯去离子水(95℃),氧气中携带一定量的水汽,使氧化气氛既含有氧,又含有水汽。

因此湿氧氧化兼有干氧氧化和en +SiO 2n -Si 外延层 n +Si 衬底水汽氧化的作用,氧化速率和二氧化硅质量介于二者之间。

实际热氧化工艺通常采用干、湿氧交替的方式进行。

模拟cmos集成电路设计(拉扎维)第2章MOS器件物理基础PPT课件

Q d ( x ) W o ( V x G C V S ( x ) V T )H

西电微电子学院-董刚-模拟集成电路设计

16

I/V特性—推导I(VDS,VGS)

I D W o [ V G x C V S ( x ) V T ] v H

Givv E ea nn E (x d ) d(x V ) dx d(x V )

数字电路设计师一般不需要进入器件内 部,只把它当开关用即可

AIC设计师必须进入器件内部,具备器 件物理知识

❖MOS管是AIC的基本元件 ❖MOS管的电特性与器件内部的物理机制密

切相关,设计时需将两者结合起来考虑

器件级与电路级联系的桥梁?

❖器件的电路模型

西电微电子学院-董刚-模拟集成电路设计

5

本讲

基本概念

I D n C o W L ( x V G V T S ) V D H , V D S 2 S ( V G V T S )

等效为一个线性电阻

RONnCoxW L(V 1GSVTH)

在AIC设计中会用到

西电微电子学院-董刚-模拟集成电路设计

深三极管区

19

I/V特性—当VDS>VGS-VTH时?

与电源无关、与温度无关、PTAT电流、 恒Gm、速度与噪声

西电微电子学院-董刚-模拟集成电路设计

2

上一讲

研究模拟电路的重要性 模拟电路设计的难点 研究AIC的重要性 研究CMOS AIC的重要性 电路设计一般概念

❖抽象级别 ❖健壮性设计 ❖符号

西电微电子学院-董刚-模拟集成电路设计

3

上一讲

数字电路无法完全取代模拟电路,模拟 电路是现代电路系统中必不可少的一部 分

提供载流子的端口为源,收集载流子的端口为漏

第一 二章作业题(参考答案)汇总

第一章引论(Introduction)1.知识要点数字电路的发展及其在信息技术领域中的地位;数字信号与模拟信号之间的关系及数字信号的基本特点;数字系统输入/输出特性及其逻辑特点,数字逻辑电路(Digital Logic Circuit)的主要内容。

重点:1.数字信号(Digital Signal)与模拟信号(Analog Signal)之间的关系;2.数字信号的基本特点;3.数字系统(Digital System)输入/输出特性及其逻辑特点。

难点:1.数字信号的基本特点;2.数字系统的特点。

数字信号只在离散时刻(观测时刻)变化;其取值也是离散的,即数字信号只能取有限种不同的值,为方便电路中处理,这些数值可以用二进制(Binary Number)表达(0,1)。

数字系统的特点:(1)只需考虑观测时刻的输入/输出关系,无须考虑其连续的变化;(2)只需考虑有限的信号取值,不考虑其中间值;(3)任何时刻一根输入/输出线上的状态只能为0或1,所以输入/输出具有有限状态,输入-输出的关系可以采用有限表格进行表达;(4)对于输出的讨论只是考虑在哪些输入条件下输出会等于0,哪些条件下会等于1,于是输入-输出关系体现为逻辑关系。

2.Exercises1.1 Define the following acronyms:ASIC, CAD, CD, CO, CPLD, DIP, DVD, FPGA, HDL, IC, IP, LSI, MCM, MSI, NRE, PBX, PCB, PLD, PWB, SMT, SSI, VHDL, VLSI.ASIC: Application Specific Integrated Circuit,专用集成电路CAD: Computer Aided Design,计算机辅助设计CD: Compact Disc,原意: 紧凑型小唱片,即CD光盘CO: Central Office,中央局,中心站,交换机(也可作Carry Out,进位输出)CPLD: Complex Programmable Logic Device,复杂可编程逻辑器件DIP: Dual Inline-pin Package,双列直插式封装DVD: Digital Versatile Disc,数字通用光盘FPGA: Field Programmable Gate Array,现场可编程门阵列HDL: Hardware Description Language,硬件描述语言IC: Integrated Circuit,集成电路IP: Internet Protocol,因特网协议(也可作Intellectual Property,知识产权)LSI: Large Scale Integration,大规模集成电路MCM: MultiChip Module,多芯片模块MSI: Medium Scale Integration,中规模集成电路NRE: Nonrecurring Engineering,非再现工程,一次性工程PBX: Private Branch Exchange,专用用户交换机PCB: Printed Circuit Board,印制电路板PLD: Programmable Logic Device,可编程逻辑器件PWB: Printed-Wiring Board,印刷线路板SMT: Surface Mount Technology,表面贴装技术SSI: Small Scale Integration,小规模集成电路VHDL: Very High-speed-integrated-circuit Hardware Description Language,超高速集成电路硬件描述语言VLSI: Very Large Scale Integration,超大规模集成电路1.2 Research the definitions of the following acronyms:ABEL, CMOS, DDPP, JPEG, MPEG, OK, PERL (Is OK really an acronym?).ABEL: Advanced Boolean Equation Language,高级布尔方程语言(一种硬件描述语言)CMOS: Complementary Metal-Oxide Semiconductor,互补金属氧化物半导体DDPP: Digital Design Principles and Practices,数字设计原理和实践(英文教材名)JPEG: Joint Photographic Experts Group,联合图像专家组MPEG: Moving Picture Experts Group,运动图像专家组OK: OkayPERL: Practical Extraction and Report Language,实用报表提取语言1.3 Draw a digital circuit consisting of a 2-input AND gate and three inverters,where an inverter is connected to each of the AND gate’s inputs and its output for each of the four possible combinations of inputs applied to the two primary inputs of this circuit determine the value produced at the primary output. Is there a simpler circuit that gives the same input/output behavior?F第二章 信息的二进制表达 (Binary Expression of Information )1.知识要点十进制、二进制、八进制和十六进制数的表示方法以及它们之间的相互转换、二进制数的运算;符号-数值码,二进制补码、二进制反码表示以及它们之间的相互转换;符号数的运算;溢出的概念。

电子技术相关 《数字集成电路基础》作业答案

《数字集成电路基础》作业答案第一次作业1、查询典型的TTL与CMOS系列标准电路各自的VIH、VIL、VOH和VOL,注明资料出处。

2、简述摩尔定律的内涵,如何引领国际半导体工艺的发展。

第二次作业1、说明CMOS电路的Latch Up效应;请画出示意图并简要说明其产生原因;并简述消除“Latch-up”效应的方法。

答:在单阱工艺的MOS器件中(P阱为例),由于NMOS管源与衬底组成PN结,而PMOS 管的源与衬底也构成一个PN结,两个PN结串联组成PNPN结构,即两个寄生三极管(NPN 和PNP),一旦有因素使得寄生三极管有一个微弱导通,两者的正反馈使得电流积聚增加,产生自锁现象。

影响:产生自锁后,如果电源能提供足够大的电流,则由于电流过大,电路将被烧毁。

消除“Latch-up”效应的方法:版图设计时:为减小寄生电阻Rs和Rw,版图设计时采用双阱工艺、多增加电源和地接触孔数目,加粗电源线和地线,对接触进行合理规划布局,减小有害的电位梯度;工艺设计时:降低寄生三极管的电流放大倍数:以N阱CMOS为例,为降低两晶体管的放大倍数,有效提高抗自锁的能力,注意扩散浓度的控制。

为减小寄生PNP管的寄生电阻Rs,可在高浓度硅上外延低浓度硅作为衬底,抑制自锁效应。

工艺上采用深阱扩散增加基区宽度可以有效降低寄生NPN管的放大倍数;具体应用时:使用时尽量避免各种串扰的引入,注意输出电流不易过大。

2、什么是器件的亚阈值特性,对器件有什么影响?答:器件的亚阈值特性是指在分析MOSFET时,当Vgs<Vth时MOS器件仍然有一个弱的反型层存在,漏源电流Id并非是无限小,而是与Vgs呈现指数关系,这种效应称作亚阈值效应。

影响:亚阈值导电会导致较大的功率损耗,在大型电路中,如内存中,其信息能量损耗可能使存储信息改变,使电路不能正常工作。

3、什么叫做亚阈值导电效应?并简单画出logI D-V GS特性曲线。

答:GS在分析MOSFET时,我们一直假设:当V GS下降到低于V TH时器件会突然关断。

(整理)集成电路设计习题答案1-5章

CH11.按规模划分,集成电路的发展已经经历了哪几代?它的发展遵循了一条业界著名的定律,请说出是什么定律?晶体管-分立元件-SSI-MSI-LSI-VLSI-ULSI-GSI-SOC。

MOORE定律2.什么是无生产线集成电路设计?列出无生产线集成电路设计的特点和环境。

拥有设计人才和技术,但不拥有生产线。

特点:电路设计,工艺制造,封装分立运行。

环境:IC产业生产能力剩余,人们需要更多的功能芯片设计3.多项目晶圆(MPW)技术的特点是什么?对发展集成电路设计有什么意义?MPW:把几到几十种工艺上兼容的芯片拼装到一个宏芯片上,然后以步行的方式排列到一到多个晶圆上。

意义:降低成本。

4.集成电路设计需要哪四个方面的知识?系统,电路,工具,工艺方面的知识CH21.为什么硅材料在集成电路技术中起着举足轻重的作用 ?原材料来源丰富,技术成熟,硅基产品价格低廉2.GaAs和InP材料各有哪些特点? P10,11 3.怎样的条件下金属与半导体形成欧姆接触?怎样的条件下金属与半导体形成肖特基接触?接触区半导体重掺杂可实现欧姆接触,金属与掺杂半导体接触形成肖特基接触4.说出多晶硅在CMOS工艺中的作用。

P13 5.列出你知道的异质半导体材料系统。

GaAs/AlGaAs, InP/ InGaAs, Si/SiGe, 6.SOI材料是怎样形成的,有什么特点?SOI绝缘体上硅,可以通过氧隔离或者晶片粘结技术完成。

特点:电极与衬底之间寄生电容大大减少,器件速度更快,功率更低7. 肖特基接触和欧姆型接触各有什么特点?肖特基接触:阻挡层具有类似PN结的伏安特性。

欧姆型接触:载流子可以容易地利用量子遂穿效应相应自由传输。

8. 简述双极型晶体管和MOS晶体管的工作原理。

P19,21CH31.写出晶体外延的意义,列出三种外延生长方法,并比较各自的优缺点。

意义:用同质材料形成具有不同掺杂种类及浓度而具有不同性能的晶体层。

外延方法:液态生长,气相外延生长,金属有机物气相外延生长2.写出掩膜在IC制造过程中的作用,比较整版掩膜和单片掩膜的区别,列举三种掩膜的制造方法。

拉扎维模拟CMOS集成电路设计作业答案中文共40页文档

53、 伟 大 的 事 业,需 要决心 ,能力 ,组织 和责任 感。 ——易 卜 生 54、 唯 书 籍 不 朽。——乔 特

拉扎维模拟CMOS集成电路设计作业答 案中文

1、合法而稳定的权力在使用得当时很 少遇到 抵抗。 ——塞 ·约翰 逊 2、权力会使人渐渐失去温厚善良的美 德。— —伯克

3、最大限度地行使权力总是令人反感 ;权力 不易确 定之处 始终存 在着危 险。— —塞·约翰逊 4、权力会奴化一切。——塔西佗

5、虽然权力是一头固执的熊,可是金 子可以 拉着它 的鼻子 走。— —莎士 比

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CMOS集成电路设计第一、二章 作业

注意:作业题的参数一律以书上表2.1为准

1. 推导工作在线性区的MOSFET的跨导和输 出阻抗的表达式。画出这些量以及gmrO相 对于VDS为自变量的函数图形,要求图形 包括线性区和饱和区。 2. 画出PMOS的小信号电路图。并解释每一 项的具体含义。 3. 如右图所示,VDD=1.8V。设定Id= 1mA。试确定Vb1的范围使得M1 和M2工作在饱和区。