超大规模集成电路设计导论:全定制设计方法

《超大规模集成电路设计》考试习题(含答案)完整版分析

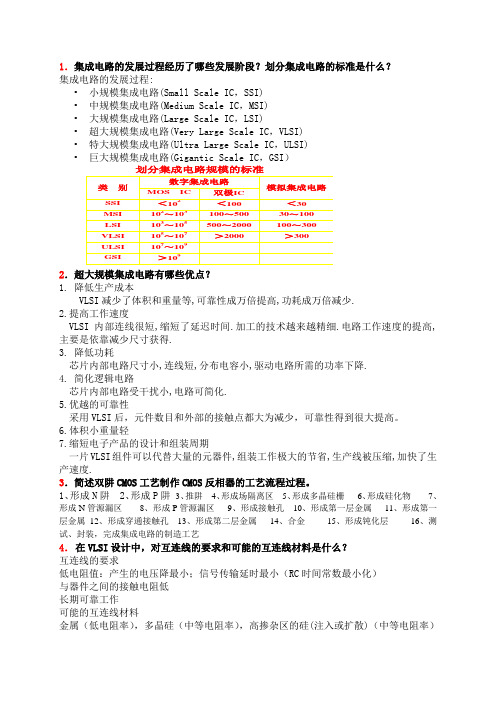

1.集成电路的发展过程经历了哪些发展阶段?划分集成电路的标准是什么?集成电路的发展过程:•小规模集成电路(Small Scale IC,SSI)•中规模集成电路(Medium Scale IC,MSI)•大规模集成电路(Large Scale IC,LSI)•超大规模集成电路(Very Large Scale IC,VLSI)•特大规模集成电路(Ultra Large Scale IC,ULSI)•巨大规模集成电路(Gigantic Scale IC,GSI)划分集成电路规模的标准2.超大规模集成电路有哪些优点?1. 降低生产成本VLSI减少了体积和重量等,可靠性成万倍提高,功耗成万倍减少.2.提高工作速度VLSI内部连线很短,缩短了延迟时间.加工的技术越来越精细.电路工作速度的提高,主要是依靠减少尺寸获得.3. 降低功耗芯片内部电路尺寸小,连线短,分布电容小,驱动电路所需的功率下降.4. 简化逻辑电路芯片内部电路受干扰小,电路可简化.5.优越的可靠性采用VLSI后,元件数目和外部的接触点都大为减少,可靠性得到很大提高。

6.体积小重量轻7.缩短电子产品的设计和组装周期一片VLSI组件可以代替大量的元器件,组装工作极大的节省,生产线被压缩,加快了生产速度.3.简述双阱CMOS工艺制作CMOS反相器的工艺流程过程。

1、形成N阱2、形成P阱3、推阱4、形成场隔离区5、形成多晶硅栅6、形成硅化物7、形成N管源漏区8、形成P管源漏区9、形成接触孔10、形成第一层金属11、形成第一层金属12、形成穿通接触孔13、形成第二层金属14、合金15、形成钝化层16、测试、封装,完成集成电路的制造工艺4.在VLSI设计中,对互连线的要求和可能的互连线材料是什么?互连线的要求低电阻值:产生的电压降最小;信号传输延时最小(RC时间常数最小化)与器件之间的接触电阻低长期可靠工作可能的互连线材料金属(低电阻率),多晶硅(中等电阻率),高掺杂区的硅(注入或扩散)(中等电阻率)5.在进行版图设计时为什么要制定版图设计规则?—片集成电路上有成千上万个晶体管和电阻等元件以及大量的连线。

电子电路设计中的数字集成电路设计方法

电子电路设计中的数字集成电路设计方法数字集成电路(Digital Integrated Circuit,简称DIC)设计方法在电子电路设计领域中扮演着至关重要的角色。

数字集成电路广泛应用于各种电子设备中,如计算机、通信设备、消费电子产品等。

本文将介绍几种常用的数字集成电路设计方法,并讨论其特点与应用。

一、全定制设计方法全定制设计方法是一种基于传统工艺的数字集成电路设计方法,它通过精确地定义电路的每个元件参数,将电路设计为完全定制化的形式。

在全定制设计方法中,设计师需要手动绘制电路原理图,并进行详细的手工布局和连线。

这种方法具有高度的灵活性和设计自由度,可以满足各种特定应用的需求。

然而,全定制设计方法需要投入大量人力与时间,成本较高,因此更适用于小批量、高性能的电路设计。

二、半定制设计方法半定制设计方法是介于全定制设计和可编程门阵列设计之间的一种设计方法。

在半定制设计方法中,设计师通过使用逻辑门库和标准元件库,将电路的逻辑功能和部分布局进行自定义,而其他部分则采用标准单元的形式。

这种方法兼具了全定制设计的灵活性和可编程门阵列设计的高效性,能够在满足设计需求的同时,有效地减少设计时间与成本。

半定制设计方法广泛应用于中小规模、低功耗的数字集成电路设计。

三、可编程门阵列(Programmable Gate Array,简称PGA)设计方法可编程门阵列设计方法是一种基于Field Programmable Gate Array (FPGA)的数字集成电路设计方法。

在可编程门阵列设计方法中,设计师通过在FPGA上进行逻辑配置,将电路设计实现为可编程的形式。

这种方法具有高度的灵活性和可重构性,能够适应快速变化的设计需求。

然而,相比于全定制设计和半定制设计方法,可编程门阵列设计方法在性能和功耗上存在一定的折中。

可编程门阵列设计方法主要应用于中小规模、低功耗的数字集成电路设计,以及快速原型验证与系统开发。

四、可重构计算机设计方法可重构计算机设计方法是一种基于可重构计算机架构的数字集成电路设计方法。

数字超大规模集成电路设计

数字超大规模集成电路设计数字超大规模集成电路设计数字超大规模集成电路(VLSI)是一种特殊类型的集成电路,由数百万个晶体管构成,可用于各种应用,例如计算机处理器、数字信号处理器、存储器和网络芯片。

设计数字超大规模集成电路需要专业的知识和技术,严格的设计过程和流程可以确保电路的性能和可靠性达到最佳水平。

数字超大规模集成电路设计的主要步骤包括电路规划、逻辑设计、物理设计和验证等四个阶段。

下面将对这四个过程分别详细介绍。

1. 电路规划电路规划是设计数字超大规模集成电路的第一步,它需要确定电路的总体结构和功能。

在这个阶段,设计师需要与客户或团队成员讨论需求和预期的目标,以确定应满足的功能和性能要求。

电路规划需要在不同的层次上考虑电路的结构,例如芯片层、宏单元层、模块层和单元层,以确保整个电路都经过了全面的思考和验证。

2. 逻辑设计在电路规划阶段完成后,设计师需要开始进行逻辑设计,这是将电路的功能和结构转化为数字逻辑块的过程。

设计师可以使用各种电子设计自动化(EDA)工具来实现逻辑设计,通常使用硬件描述语言(HDL)来表示电路的行为和结构。

逻辑设计包括几个不同的步骤,例如:逻辑合成:将高层次的行为描述转化为门级或寄存器传输级别的等效电路。

时序分析:确保电路满足时序约束和时钟周期。

优化布局和布线:通过逻辑综合和布局布线工具优化电路,以实现更好的性能和功耗。

3. 物理设计物理设计阶段是将逻辑电路实现为实际电路的过程,包括立即设计、布局规划、布线、物理验证等。

立即设计:确定电路各个模块的精确位置,以及电路的层次和结构。

布局规划:根据立即设计结果生成电路的初始布局方案,包括放置模块、布线规划以及时钟树设计等。

布线:将布局好的模块进行线路连接,生成物理电路,并进行布线优化、电容和电感提取,确定线路的延迟等等。

物理验证:设计师对所生成的物理电路进行验证,包括逻辑验证、时序验证、数据库校验等,以确保电路的功能与预期相符,而且其性能达到标准。

超大规模集成电路第一章

人们总是需要更复杂的系统

S S I M S I

L S I

V L S I U L S I G S I

晶 体 管 数< 102 102~103 103~105 105~107 107~109 > 109

门 数 < 10 10~102 102~104 104~106 106~108 > 108

利用率高、速度快、功耗低的最优性能的芯片,但这种设计周期长、成本高,适用于要 求性能高或批量很大的芯片。 半定制设计:

半定制设计又可分为门阵列设计、标准单元设计、可编程逻辑器件设计。都是约束性 的设计方法,其主要目的就是简化设计,以牺牲芯片性能为代价来缩短开发时间

53

集成电路半定制设计方法+

门阵列设计 又称“母片”(Master Slice)法,是早期开发并得到广泛应用的ASIC技术,母片是IC工厂

EDA工具 ★ 电路分析、原理图设计、仿真、综合(可测性设计、功耗)、版图、时序分析等。

50

未来VLSI工艺已从深亚微米到超深亚微米迈进,对于功耗与速度提出了更高的要求。 互联——延迟,交扰,寄生等问题 功耗 复杂度——系统芯片,软硬件协同设计等

51

连线参数-

工艺特征等比改变时,连线的延迟基本不变。 ★ 沟道长度按等比因子缩小,因此晶体管开关延迟按因子减小。 ★ 电阻的长度按因子减小,但截面积按2减小,因此电阻按增大。 ★ 电容的平板面积按2减小,但中间绝缘层也按因子减小,因此电容按减小。

双极型RTL

nMOS

CMOS

26

VLSI中的低功耗

CMOS门电路需要的功耗比其它门电路小 尺寸是低功耗的本质因素

超大规模集成电路设计

PentiumPro

当前:超大规模集成电路(VLSI)时代

为什么采用VLSI:人们对电子系统的需要

★ 功能要求越来越复杂:电路规模 ★ 性能要求越来越优良:速度、功耗 ★ 成本相对来讲最好低一点:尺寸

由于集成电路在电子系统中的核心作用,集成电路在系统功能、 性能和成本中所起的作用是关键性的

集成电路的三个关键特性(功能要求定下来的前提下)

课程参考书

(仅适用于Part 1) 中文版 《现代VLSI设计——系统芯片设计》(原书第三版)

[美]韦恩•沃尔夫 著 科学出版社

该书的前半部分 (Chap1-6)

英文版 Modern VLSI Design: System-on-Chip Design, 3th

by Wayne Wolf

绪 论

1. IC:从设计、制造、封装、测试到芯片产品

IC设计与EDA技术/EDA工具 (1)

• EDA(Electronic Design Automatic,电子设计自动化) 是指以计 算机为工作平台的电子CAD工具软件集 • EDA工具使得设计者的工作仅限于利用软件的方式,就能完成对 系统硬件功能和性能的实现 • 集成电路设计从一开始就依赖于EDA技术及工具,离开EDA技术 集成电路设计将寸步难行。而且随着技术的进步,集成电路的设 计越来越依赖EDA工具

• 数字IC中,数字ASIC与FPGA/CPLD 的区别 – ASIC:需制作掩模

• 设计时间长,硬件不能升级 • 芯片面积小,性能可以得到较好的优化 • 适合芯片需求量大的场合:片量用于平摊昂贵的光罩掩模制版 费,降低单片生产成本

– FPGA/CPLD:可以编程,不需要后端设计/制作掩模

• • • • 开发门槛较低,设计时间较短,可方便和快速地升级优化硬件 芯片面积大,性能不够优化 适合芯片需求量小的场合:不用支付昂贵的光罩掩模制版费 作为数字ASIC设计流程中的必要步骤:ASIC设计中前端设计 的FPGA原型验证(HDL功能验证)

超大规模集成电路

目录摘要 (1)关键词 (1)Abstract (1)Key words (1)1 引言 (1)2 超大规模集成电路的设计要求 (1)3 超大规模集成电路的设计策略 (2)3.1层次性 (2)3.2模块化 (2)3.3规则化 (2)3.4局部化 (2)4 超大规模集成电路的设计方法 (3)4.1 全定制设计方法 (3)4.2 半定制设计方法 (4)4.3 不同设计方法的比较 (5)5 超大规模集成电路的设计步骤 (6)5.1 系统设计 (7)5.2 功能设计 (7)5.3 逻辑设计 (7)5.4 电路设计 (7)5.5 版图设计 (7)5.6 设计验证 (8)5.7 制造 (8)5.8 封装和测试 (8)6 超大规模集成电路的设计流程 (8)6.1 总体的设计流程 (8)6.1.1高层次综合 (8)6.1.2逻辑综合 (8)6.1.3 物理综合 (9)6.2 详细的设计流程 (9)7 超大规模集成电路的验证方法 (9)7.1 动态验证 (9)7.2 静态验证 (9)7.3 物理验证 (9)8 总结 (9)致谢 (10)参考文献 (10)超大规模集成电路网络工程专业学生孙守勇指导教师吴俊华摘要:随着集成电路的高速发展,集成电路的设计显得越来越重要,目前设计能力滞后于制造工艺已成为世界集成电路产业的发展现状之一。

为了明确超大规模集成电路设计的理想方法,首先对超大规模集成电路的设计要求进行了调查,然后对超大规模集成电路的设计策略进行了研究,探讨了超大规模集成电路的不同设计方法,并对不同的设计方法做出了比较,明确了超大规模集成电路的设计步骤及设计流程,最后探讨了超大规模集成电路的验证方法。

关键词:集成电路设计方法步骤Very Large Scale IntegrationStudent Majoring in Network Engineering Sun ShouyongTutor Wu JunhuaAbstract:With the high speed development of integrated circuit, the design of integrated circuit is becoming more and more important. At present, the design capacity behind manufacture technology has become one of the world's integrated circuit industry development current situation. In order to specify the ideal method of VLSI design, first of all, the requirements of VLSI was investigated, then, the design strategy of VLSI is studied. Discuss different methods of VLSI, and made a comparison of different methods. Clear and definite the design steps of very large scale integrated circuit and the design process, finally, discuss the validation method of very large scale integrated circuit.Key words:integrated circuit; design; method; step1引言自从1959年集成电路诞生以来,经历了小规模(SSI)、中规模(MSI)、大规模(LSI)的发展历程,目前已进入超大个规模(VLSI)和甚大规模集成电路(ULSI)阶段,集成电路技术的发展已日臻完善,集成电路芯片的应用也渗透到国民经济的各个部门和科学技术的各个领域之中,对当代经济发展和科技进步起到了不可估计的推动作用。

超大规模集成电路的设计方法 (2)

超大规模集成电路课程论文题目:超大规模集成电路的设计方法院系:xxxxxxxxx专业:xxxxxxxxxxxx年级:xxxxxxxxx学号:xxxxxxxxxxx姓名:xxxxxx指导老师:xxxxxxxxxx完成时间:xxxxxxxxxxx超大规模集成电路的设计方法作者:xxxx指导老师:xxxxxxxxxxxxxxxxx摘要:本文在概述超大规模集成电路设计步骤上,详细的论述了各种设计集成电路的方法,讨论了全定制法、标准单元设计方法、积木块设计方法、门阵列设计方法以及可编程逻辑器件设计方法的特点和适用范围。

关键词:集成电路;全制定法;标准单元设计法Abstracts:On the basis of VLSI design method, this thesis detailed expounds the methods of design of integrated circuits, discusses the custom law, full customization method, standard unit design method ,building block design ,gate array method and design method of programmable logic devices 's characteristics and applicability.Keywords: integrate circuit;full customization method;standard unit design method1 引言所谓集成电路就是将晶体管、电阻、电容、等各种电子元器件以相互联系的状态集成到半导体材料(主要是硅)或者绝缘体材料薄层片子上,再用一个管壳将其封装起来,构成一个完整的、具有一定功能的电路或系统。

自1959年以来,集成电路技术发生了惊人的变化。

超大规模集成电路设计方法学导论第二版课程设计

超大规模集成电路设计方法学导论第二版课程设计项目背景随着半导体工艺和设计技术的不断进步,超大规模集成电路(Very Large Scale Integration,VLSI)已成为电子工业的主流技术之一。

在VLSI设计中,设计方法学起到至关重要的作用,可以提高设计效率、降低设计成本、提高设计质量和可重用性。

本课程旨在介绍VLSI设计方法学的基本原理和实践方法,为学生提供一种深入了解VLSI设计的能力和技能。

课程目标本课程旨在:•介绍VLSI设计的基本原理和实践方法;•培养学生的VLSI设计能力和技能;•提供学生参与VLSI设计项目的实践机会,了解VLSI产品开发和制造的全过程。

课程内容本课程包括以下主题:1.VLSI设计流程介绍VLSI设计的基本流程,包括开发需求、架构设计、逻辑设计、物理设计、验证和测试等环节。

2.VLSI设计工具介绍常用的VLSI设计工具,如EDA工具、仿真工具、物理设计工具等,并说明它们的使用方法和特点。

3.VLSI设计技术与方法介绍VLSI设计中的关键技术和方法,如低功耗设计、时序约束、功耗分析等,并通过实例分析加深理解。

4.VLSI设计案例分析选取一些典型的VLSI设计案例,介绍其设计原理和实现技术,并引导学生进行分析和讨论。

课程设计课程设计要求学生选择一个VLSI设计项目进行研究和实践,包括以下环节:1.项目选择学生从给定的VLSI设计项目中选择一个项目,并列出项目的开发需求、设计目标和约束条件。

2.架构设计学生进行项目的架构设计,确定项目的功能模块和接口,并绘制设计图。

3.逻辑设计学生进行项目的逻辑设计,编写硬件描述语言(HDL)代码,并进行仿真和验证。

4.物理设计学生进行项目的物理设计,包括布局设计和布线设计,并进行功耗和时序分析。

5.验证和测试学生进行项目的验证和测试,包括模拟验证、板级测试和芯片级测试等环节。

总结本课程通过理论学习和实践项目相结合的方式,培养学生的VLSI设计能力和技能,提高学生的综合素质和创新能力。