高速数字电路设计中反射的影响及其抑制方法

高速数字设计中的反射分析

电 子 澜

试

Au 201 g. 0 No. 8

繁 8强

EL EcTR0NI C T ES T

高速数字设 计中的反射分析

刘 伟,康 凯 , 子发 钟ຫໍສະໝຸດ ( 电子工程学院 ,安徽合肥

20 3 3 07

摘要 :随着集成 电路开关速度的提高 以及P B(r tdCi ut or) C Pi e r iB ad板密度的增加 ,信号完整性问题 已成 为高 n c 速P 设 计必须关注的问题之一, CB 对信号进行完整性分析 已经成 为高速数 字电路设 计中的一个必 要环节 。本文 介绍 了高速P 设计 中出现 的信 号完 整性问题 ,对相关的时序 、反射 、串扰和地弹等问题进行 了深入讨论 , CB 并利用Hy ey x pf n 对其作了相应的仿 真。根据 以上研究 的结果 ,比较 了不同的端接策略, 了解决方案 的有效 l 验证

w a e or n vit e o y ry v f m i ru fH pe lnx. n t s s u so a ve c O hebaeoft dic si n bo , om p rngal i so em i ai n e h que , he a i lk nd ft r n to tc ni s i ov ha h c m ei aii n h ehod o i na n e rt a lssi i po t n o hih—s e e i . tpr et tt e she sv ld t a d t e m t y fS g lI t g y nay i s m i ra tt g pe d d sg n

0引 言

随着 电子技术 的不断发 展 , 速器件 被广泛 的 高

常用的抑制反射的方法

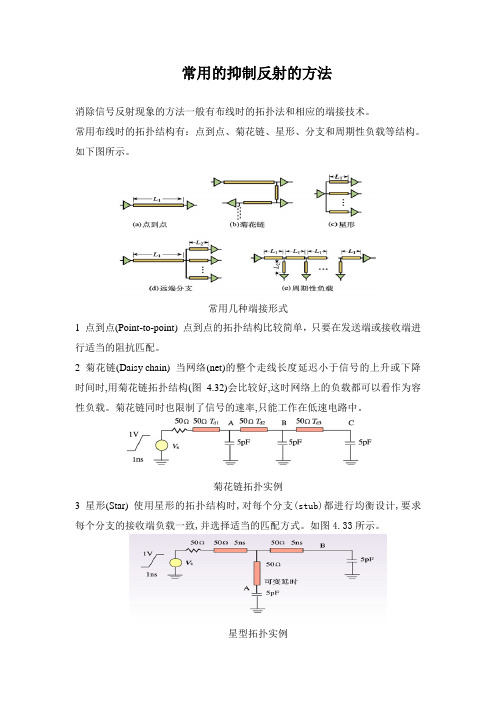

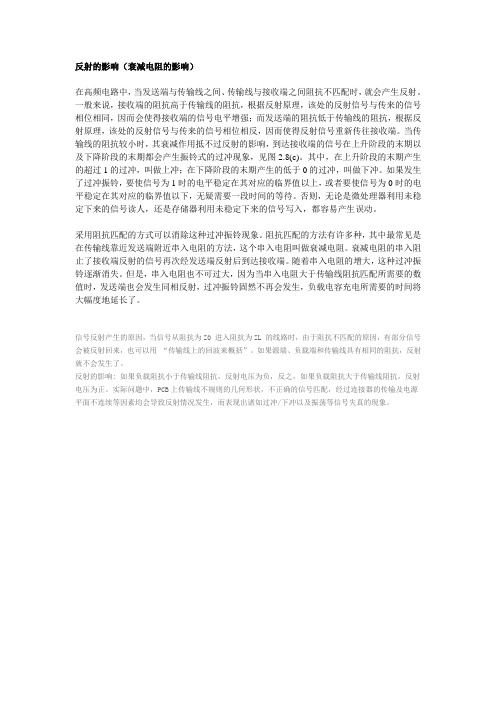

常用的抑制反射的方法消除信号反射现象的方法一般有布线时的拓扑法和相应的端接技术。

常用布线时的拓扑结构有:点到点、菊花链、星形、分支和周期性负载等结构。

如下图所示。

常用几种端接形式1 点到点(Point-to-point) 点到点的拓扑结构比较简单,只要在发送端或接收端进行适当的阻抗匹配。

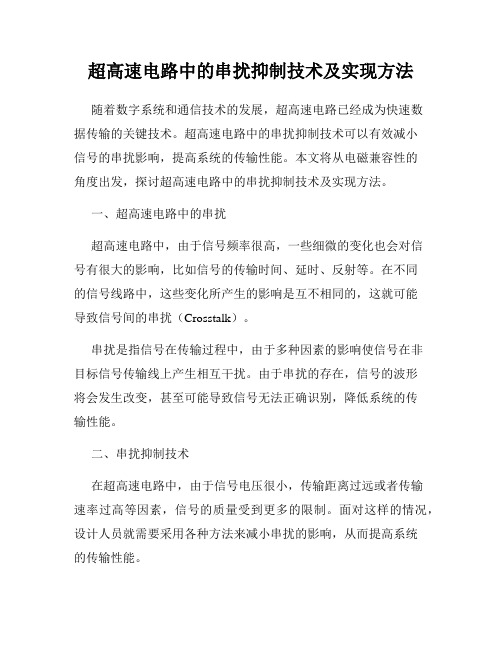

2 菊花链(Daisy chain) 当网络(net)的整个走线长度延迟小于信号的上升或下降时间时,用菊花链拓扑结构(图 4.32)会比较好,这时网络上的负载都可以看作为容性负载。

菊花链同时也限制了信号的速率,只能工作在低速电路中。

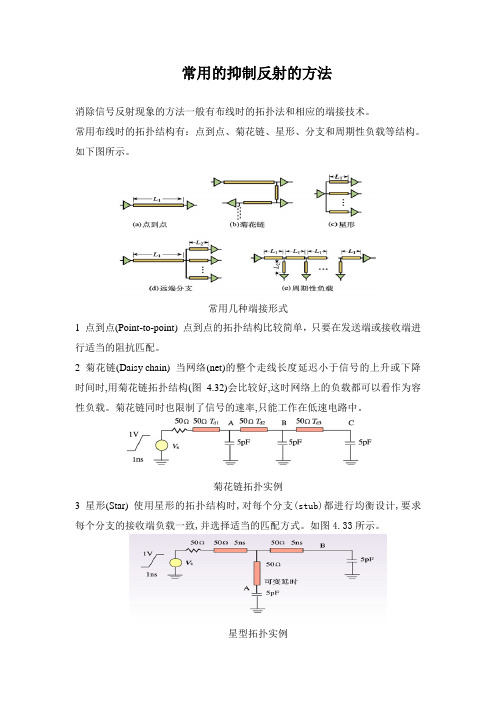

菊花链拓扑实例3 星形(Star) 使用星形的拓扑结构时,对每个分支(stub)都进行均衡设计,要求每个分支的接收端负载一致,并选择适当的匹配方式。

如图4.33所示。

星型拓扑实例远端分支(Far-end cluster) 跟星形类似,只不过分支是靠近接收端。

在这种拓扑结构中,也要限制远端stub的长度,使stub上的传输延时小于信号上升沿,这样每个接收端都可以被看作为一个简单的容性负载。

周期性负载(Periodic loading) 周期性负载的拓扑结构同样要求每段stub的长度足够小,使stub上的传输延时小于信号上升沿。

这种主干传输线和所有的stub段组合起来的结构可以看作为一段新的传输线,其特征阻抗要比原来主干传输线的特征阻抗小,传输速率也比原来的低,因此在进行阻抗匹配时要注意。

传输线上的反射会对数字系统性能有重要的负面影响。

为了最小化反射的负面影响,除了从拓扑结构上消除相应的影响外,还必须有相应控制它们的方法。

基本上有三种方法减低这些反射的负面影响。

第一种方法就是降低系统的频率或增大信号的上升沿时间,以使传输线上的反射将在另一个信号驱动到线上之前达到稳态。

然而通常这是不可能的,对于高速系统,增大信号上升沿时间,将影响系统的性能。

第二种方法是缩短PCB走线长度以使反射在更短时间内达到稳态。

42. 如何在电磁兼容设计中避免信号反射?

42. 如何在电磁兼容设计中避免信号反射?42、如何在电磁兼容设计中避免信号反射?在当今的电子设备和系统设计中,电磁兼容(EMC)是一个至关重要的考虑因素。

信号反射是电磁兼容设计中常见的问题之一,如果不加以妥善处理,可能会导致信号完整性受损、系统性能下降,甚至影响设备的正常运行。

那么,如何在电磁兼容设计中有效地避免信号反射呢?要理解信号反射,我们首先需要明白它是怎么产生的。

当信号在传输线上传播时,如果遇到阻抗不连续的地方,就会发生反射。

这就好比在高速公路上开车,突然道路变窄或者出现障碍物,车流就会受到阻碍和反弹。

在电子电路中,常见的阻抗不连续点包括线路的拐角、分支、不同线宽的连接、连接器以及终端负载等。

为了避免信号反射,一个关键的措施是进行良好的阻抗控制。

这意味着我们要确保信号传输线的阻抗在整个路径上保持恒定。

对于常见的 PCB 布线来说,我们可以通过选择合适的层叠结构、线宽和介质厚度来实现预定的阻抗值。

比如,在高速数字电路中,常用的微带线和带状线结构都有相应的计算公式和设计规则,来帮助我们达到所需的阻抗。

终端匹配也是减少信号反射的重要手段。

当信号到达传输线的终端时,如果终端的阻抗与传输线的特性阻抗不匹配,就会产生反射。

常见的终端匹配方式有串联匹配、并联匹配和戴维南匹配等。

串联匹配通常适用于源端输出阻抗较低的情况,通过在信号源端串联一个电阻来实现匹配;并联匹配则是在终端并联一个电阻,使其阻抗与传输线的特性阻抗相等;戴维南匹配则相对复杂一些,但在一些特殊情况下能够提供更好的性能。

合理的布线规则同样有助于避免信号反射。

在 PCB 设计中,应尽量避免直角走线,因为直角会导致阻抗的突变。

采用 45 度角或者弧形走线可以减少这种影响。

同时,要注意信号线之间的间距,避免信号之间的串扰。

对于高速信号线,还应该进行差分走线,这样可以有效地提高信号的抗干扰能力,并减少反射。

选择合适的连接器和封装也非常重要。

连接器和封装的寄生参数,如电感和电容,会对信号的传输产生影响。

高速数据传输线路中的反射与传输特性分析

高速数据传输线路中的反射与传输特性分析随着科技的不断进步,高速数据传输已经成为现代社会中不可或缺的一部分。

无论是在通信领域还是在计算机网络中,高速数据传输线路的稳定性和可靠性对于数据的传输质量至关重要。

在实际应用中,我们常常会面临一些问题,比如信号的反射和传输特性。

本文将对高速数据传输线路中的反射和传输特性进行分析和探讨。

首先,我们来看一下高速数据传输线路中的反射问题。

当信号在传输线路中传输时,会遇到各种不同的障碍物,比如连接器、电缆、分支等。

这些障碍物会导致信号的反射,从而降低传输的质量。

反射信号会与原始信号相叠加,形成波形失真和信号衰减。

为了解决这个问题,我们可以采取一些措施,比如使用合适的连接器和电缆,以及安装衰减器和终端阻抗匹配器。

通过这些措施,可以有效减少信号的反射,提高传输的稳定性和可靠性。

接下来,我们来讨论高速数据传输线路的传输特性。

传输特性是指信号在传输线路中的衰减、延迟和失真等方面的表现。

在高速数据传输中,信号的传输特性对于数据的完整性和准确性起着重要的影响。

传输特性的分析可以帮助我们了解信号在传输过程中的变化,并采取相应的措施来优化传输效果。

首先是衰减特性。

随着信号在传输线路中传播,会逐渐衰减,导致信号强度的降低。

这是由于电缆材料和电磁波传播特性造成的。

为了减少衰减,我们可以选择合适的电缆和信号放大器,以增强信号的强度。

其次是延迟特性。

信号在传输线路中传播需要一定的时间,这就是延迟。

延迟会导致信号的同步问题,特别是在多路传输和远程通信中。

为了解决这个问题,我们可以使用延迟补偿器和时钟同步技术来保持信号的同步。

最后是失真特性。

高速数据传输线路中的失真主要包括时域失真和频域失真。

时域失真是指信号波形的扭曲和失真,频域失真是指信号频谱的变化。

为了减少失真,我们可以使用均衡器和滤波器来调整信号的波形和频谱。

综上所述,高速数据传输线路中的反射和传输特性是影响数据传输质量的重要因素。

通过分析和理解这些特性,我们可以采取相应的措施来优化传输效果,提高数据传输的稳定性和可靠性。

数字信号传输过程中的反射干扰及其抑制方法

数字信号传输过程中的反射干扰及其抑制方法[摘要] 在数字电路(特别是高速数字电路)信号有线传输过程中,存在传输信号的反射干扰问题。

在简要介绍传输线等效电路的基础上,分析了数字信号传输线的反射特性和数字信号有线传输时存在的反射干扰,给出了数字信号反射干扰的抑制方法和措施。

[关键词] 数字信号传输线反射干扰阻抗匹配1引言在高频电路和微波电路中,通常比较重视研究信号的反射干扰问题。

反射干扰是指在信号的传输过程中,由于传输系统的传输线特性阻抗与负载阻抗不匹配等原因,使得传输到负载上的信号部分或全部被反射回来,从而对传输信号造成的干扰。

反射干扰严重时甚至会使信号无法进行传输。

要抑制或消除反射干扰,必须使信源内阻等于传输线特性阻抗,同时传输线的特性阻抗又等于负载阻抗,实现阻抗匹配。

实际上,信号的反射干扰问题在数字电路信号传输过程中同样存在,特别是在高速数字电路中,传输信号的反射干扰问题非常突出。

数字信号在传输线中传输(尤其是长距离传输)时,传输线的长度、结构等因素直接影响到反射信号的量值,造成信号波形畸变或产生脉冲噪声,严重时甚至会导致电路误动作。

研究数字电路中信号传输的反射干扰及其抑制方法有重要的实际意义。

2数字信号传输线反射特性分析2.1传输线及其等效电路图1 传输线及其等效电路图1是传输线及其等效电路。

传输线都有分布电容和分布电感。

如将整个传输线分成n小段,每小段均由自己的分布电容和电感,由于电感阻碍电流的突变,而电容阻碍电压的突变,因此,在电路开关闭合后,并不是整个传输线上所有各点都同时达到电压的定值U和电流的定值I,而是像电压波和电流波那样按相同的速度向终点推进。

电流的大小既与传输线本身的特性有关,也与负载特性有关。

电压波和电流波幅度之间的关系,一般只取决于传输线本身的分布参数C1和L1(C1、L1分别表示单位长度传输线上的分布电容量和电感量),即通常把称为传输线的特性阻抗。

传输线的特性阻抗反映了沿传输线运行的电压波和电流波之间的关系。

反射的影响

反射的影响(衰减电阻的影响)在高频电路中,当发送端与传输线之间、传输线与接收端之间阻抗不匹配时,就会产生反射。

一般来说,接收端的阻抗高于传输线的阻抗,根据反射原理,该处的反射信号与传来的信号相位相同,因而会使得接收端的信号电平增强;而发送端的阻抗低于传输线的阻抗,根据反射原理,该处的反射信号与传来的信号相位相反,因而使得反射信号重新传往接收端。

当传输线的阻抗较小时,其衰减作用抵不过反射的影响,到达接收端的信号在上升阶段的末期以及下降阶段的末期都会产生振铃式的过冲现象,见图2.8(c)。

其中,在上升阶段的末期产生的超过1的过冲,叫做上冲;在下降阶段的末期产生的低于0的过冲,叫做下冲。

如果发生了过冲振铃,要使信号为1时的电平稳定在其对应的临界值以上,或者要使信号为0时的电平稳定在其对应的临界值以下,无疑需要一段时间的等待。

否则,无论是微处理器利用未稳定下来的信号读人,还是存储器利用未稳定下来的信号写入,都容易产生误动。

采用阻抗匹配的方式可以消除这种过冲振铃现象。

阻抗匹配的方法有许多种,其中最常见是在传输线靠近发送端附近串入电阻的方法,这个串入电阻叫做衰减电阻。

衰减电阻的串入阻止了接收端反射的信号再次经发送端反射后到达接收端。

随着串入电阻的增大,这种过冲振铃逐渐消失。

但是,串入电阻也不可过大,因为当串入电阻大于传输线阻抗匹配所需要的数值时,发送端也会发生同相反射,过冲振铃固然不再会发生,负载电容充电所需要的时间将大幅度地延长了。

信号反射产生的原因,当信号从阻抗为Z0 进入阻抗为ZL 的线路时,由于阻抗不匹配的原因,有部分信号会被反射回来,也可以用“传输线上的回波来概括”。

如果源端、负载端和传输线具有相同的阻抗,反射就不会发生了。

反射的影响: 如果负载阻抗小于传输线阻抗,反射电压为负,反之,如果负载阻抗大于传输线阻抗,反射电压为正。

实际问题中,PCB上传输线不规则的几何形状,不正确的信号匹配,经过连接器的传输及电源平面不连续等因素均会导致反射情况发生,而表现出诸如过冲/下冲以及振荡等信号失真的现象。

超高速电路中的串扰抑制技术及实现方法

超高速电路中的串扰抑制技术及实现方法随着数字系统和通信技术的发展,超高速电路已经成为快速数据传输的关键技术。

超高速电路中的串扰抑制技术可以有效减小信号的串扰影响,提高系统的传输性能。

本文将从电磁兼容性的角度出发,探讨超高速电路中的串扰抑制技术及实现方法。

一、超高速电路中的串扰超高速电路中,由于信号频率很高,一些细微的变化也会对信号有很大的影响,比如信号的传输时间、延时、反射等。

在不同的信号线路中,这些变化所产生的影响是互不相同的,这就可能导致信号间的串扰(Crosstalk)。

串扰是指信号在传输过程中,由于多种因素的影响使信号在非目标信号传输线上产生相互干扰。

由于串扰的存在,信号的波形将会发生改变,甚至可能导致信号无法正确识别,降低系统的传输性能。

二、串扰抑制技术在超高速电路中,由于信号电压很小,传输距离过远或者传输速率过高等因素,信号的质量受到更多的限制。

面对这样的情况,设计人员就需要采用各种方法来减小串扰的影响,从而提高系统的传输性能。

1. 电磁屏蔽在超高速电路中,电磁屏蔽是一种非常有效的串扰抑制方法。

通过在信号传输线周围设置导电屏蔽材料,可以有效隔离与信号传输无关的电磁场干扰,同时有效地减小了信号间的串扰。

2. 增加信号线之间的距离在超高速电路中,信号传输线之间的距离越大,信号间的串扰就越小。

因此,在设计超高速电路时,应该尽可能的增加信号线之间的距离,以减小信号间的干扰影响。

3. 使用串扰抑制电路技术串扰抑制电路技术可以有效减小信号的串扰影响,提高系统的传输性能。

常见的串扰抑制电路技术包括共模抑制、差分传输技术、电子束平衡等。

其中,差分传输技术是比较常用的一种串扰抑制电路技术。

通过采用差分信号的传输方式,能够在相邻的线路中产生相反的信号,从而减小串扰的影响,提高信号的传输质量。

三、串扰抑制技术的实现方法1. 均匀分布型布局在超高速电路设计中,均匀分布型布局是一种值得推荐的布局方式。

在设计电路时,应该将信号线之间均匀分布,尽可能保持信号线之间的距离,减小信号间的干扰影响。

常用的抑制反射的方法

常用的抑制反射的方法消除信号反射现象的方法一般有布线时的拓扑法和相应的端接技术。

常用布线时的拓扑结构有:点到点、菊花链、星形、分支和周期性负载等结构。

如下图所示。

常用几种端接形式1 点到点(Point-to-point) 点到点的拓扑结构比较简单,只要在发送端或接收端进行适当的阻抗匹配。

2 菊花链(Daisy chain) 当网络(net)的整个走线长度延迟小于信号的上升或下降时间时,用菊花链拓扑结构(图 4.32)会比较好,这时网络上的负载都可以看作为容性负载。

菊花链同时也限制了信号的速率,只能工作在低速电路中。

菊花链拓扑实例3 星形(Star) 使用星形的拓扑结构时,对每个分支(stub)都进行均衡设计,要求每个分支的接收端负载一致,并选择适当的匹配方式。

如图4.33所示。

星型拓扑实例远端分支(Far-end cluster) 跟星形类似,只不过分支是靠近接收端。

在这种拓扑结构中,也要限制远端stub的长度,使stub上的传输延时小于信号上升沿,这样每个接收端都可以被看作为一个简单的容性负载。

周期性负载(Periodic loading) 周期性负载的拓扑结构同样要求每段stub的长度足够小,使stub上的传输延时小于信号上升沿。

这种主干传输线和所有的stub段组合起来的结构可以看作为一段新的传输线,其特征阻抗要比原来主干传输线的特征阻抗小,传输速率也比原来的低,因此在进行阻抗匹配时要注意。

传输线上的反射会对数字系统性能有重要的负面影响。

为了最小化反射的负面影响,除了从拓扑结构上消除相应的影响外,还必须有相应控制它们的方法。

基本上有三种方法减低这些反射的负面影响。

第一种方法就是降低系统的频率或增大信号的上升沿时间,以使传输线上的反射将在另一个信号驱动到线上之前达到稳态。

然而通常这是不可能的,对于高速系统,增大信号上升沿时间,将影响系统的性能。

第二种方法是缩短PCB走线长度以使反射在更短时间内达到稳态。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第22卷第11期系统工程与电子技术Systems Engineering and ElectronicsVol 122,No 1112000收稿日期:1999-11-10 修订日期:2000-04-29作者简介:王宏伟(1971-),男,北京理工大学电子工程系博士,主要研究方向为雷达信号处理技术。

文章编号:1001-506X(2000)11-0081-03高速数字电路设计中反射的影响及其抑制方法王宏伟 高梅国 韩月秋北京理工大学电子工程系,100081摘 要 主要研究了高速数字电路设计中信号反射的抑制方法。

理论上分析了信号反射产生的原因及其对电路设计指标的影响,通过电路仿真,比较不同的布局布线和端接策略,并针对具体情况,提出了合理的布局布线和端接方法。

该方法已成功应用于多DSP 并联处理系统中,实践证明该方法可靠、系统工作稳定。

主题词 数字电路 信号反射 电路设计中图分类号:TN911172The Influence and Elimination Method of Reflections in High-Speed Digital-Circuit DesignWang Hongwei Gao Meiguo Han YueqiuDe partment o f Ele ctronics Engine ering ,Bei jing Institute o f Technology,100081A bstract This paper studies the elimination method of reflections i n hi gh-speed digital-circui t design.The cause and i nflu -ence of reflections of high-speed digital signal are analyzed.All kinds of termination techniques and board layout are compared and si mulated.The proper termination technique and board layou t are promoted according to circumstances.The mul tiprocessing DSP sys -tem which employed proper terminations has been proved stably and reliably.Keywords Di gital circuit Signal reflection Circuit design1 信号反射的产生及其影响在PCB 板上,信号传输的等效模型如图1所示[1],信号的反射可以利用电磁波传输理论来理解,当驱动器驱动信号由低电平向高电平转换时,在信号的上升阶段发出入射波,入射波沿传输线传向负载Z L ,如果Z L 等于传输线特征阻抗Z 0,则入射波被完全吸收,没有信号反射发生,如果Z L 不等于Z 0,即有阻抗失配,则产生反射波沿传输线传回发射端,反射波的大小与阻抗的误配程度有关,通常用反射系数来描述,负载端的反射系数K L 定义为反射电压与入射电压之比,即K L =(Z L -Z 0)/(Z L +Z 0),由于Z L 是输入电路的输入阻抗,常远远大于Z 0,所以反射系数K L 约为1,即反射波等于入射波,发生全反射,这时负载端的电压为入射波电压的2倍,形成过冲。

同理,反射波到达源端后再次形成反射,其反射系数K S =(R S -Z 0)/(R S +Z 0),R S 为驱动电路的输出阻抗,一般小于传输线特征阻抗Z 0,则信号再一次反射,传向接收端,以此类推。

由于实际的传输线有电阻,信号会逐渐衰减,通常只需考虑3次来回反射。

当信号从接收端反射回来时,如果发射信号仍处于信号的上升阶段,则反射波被/吸收0,即看不出明显影响,若发射信号已处于稳态,则反射波会叠加在稳态信号上,形成振荡,从经验上讲,当传输线延迟时间大于1/6信号的上升时间时,会有明显的振荡发生。

由于过大的振荡电压会损害输入电路,因而必须抑制反射;另一方面,反射波形成的振荡加长了信号的稳定时间,在高速电路设计中,这个时间是必须考虑的。

如常用的计算机局域总线(Peripheral Component Interconnect,PCI)规定信号的建立时间要小于10ns,这就对信号线的长度、布局和端接等提出了具体要求。

2 不同拓扑结构对信号的影响211 总线结构总线结构是指驱动器和负载顺序连接在信号线上,有时也称菊花链结构,这是一种最常见的连接方式,特别是多驱动和多负载的情况,如摩托罗拉公司定义的计算机标准总线(Versa Module Eurocard,VME),它的背板总线就采用这种结构,通常的要求是信号线的分支应尽可能短。

现建立如下仿真条件:采用ADSP-21060为驱动源,另有3个ADSP-21060为负载,采用508特征阻抗的微带传输线,两两之间相距10英寸,仿真结果如图2所示。

图中波形1是离驱动源近的信号,波形2是离驱动源远的信号,可见,离驱动源越近受到的反射干扰越严重,而远端的信号除了有一个相对较大的传输线延迟外,波形形状最好,有单调的上升和下降沿,其原因是近端信号是多点反射的综合结果,而远端受到的反射干扰较小,这一点应特别注意。

212 星形结构星形结构是指负载分布在驱动源的周围,直接和驱动源相连,现建仿真条件如下:3个ADSP-21060为负载,各通过长10英寸、特征阻抗为508的微带线与ADSP-21060驱动源直接相连,其仿真波形如图3所示(3个负载的波形相同),与图2相比,它是曲线1和曲线2的折衷,有较好的波形和较小的延迟。

采用这种结构,从驱动源看传输线的阻抗降低到原阻抗的1/3,与ADSP-21060的输出阻抗接近,效果相当于串行端接。

图2 总线拓扑结构仿真结果 图3 星形拓扑结构仿真结果结果分析:¹不同的拓扑结构对信号波形有很大的影响,合理的结构往往能够取得较好的效果;º信号的波形与连线的总长度有关,连线越长,离驱动点近的波形越差。

因此在设计高速电路时应采用缓冲器件把高速部分和低速部分分开,把近端和远端分开;»由于实际的输入电路有保护二极管,它旁路了过冲电流,因而反射影响较小,当电路中没有接具体器件时,这时反射形成的过冲很大,在系统调试时应注意这个问题;¼信号反射与驱动器的驱动能力有关,低输出电阻,高输出电流的驱动器引起的信号反射相对严重。

3 信号的端接端接的目的是减少信号的反射,通常有并行端接、戴维宁端接、AC 端接、串行端接和二级管端接,它们都能有效地减少信号反射,但同时也引入了其它问题,如能量消耗大、噪声抑制下降和增加了延迟等,因此,在进行信号端接时一定要分析它们的影响,只有采用恰当的端接技术才能改善信号的质量。

311 并行端接并行端接是最简单的端接技术,通过在负载端接一电阻到地或到电源,其阻值等于特征阻抗来实现。

当驱动信号为高占空比信号时,端接到电源端有利于减少能量消耗。

这种端接的缺点是要求驱动器有很大的驱动能力来维持要求的电平,因而较少被采用,另一个缺点是这种端接会改变信号的边沿,从而改变信号的占空比。

312 戴维宁端接戴维宁端接是并行端接的改进,在负载端采用两个电阻,一个接电源和另一个接地来实现,要求它们的并联阻值等于信号线的特征阻抗来减少反射,接电源端的电阻有利于驱动器上拉到高电平,接地的电阻有利于驱动器下拉到低电平,恰当地选择电阻值能够增强驱动器的扇出能力,这种端接有较好的过冲抑制能力。

它的缺点是有大的直流消耗在端接电阻上,还有一个容易被遗漏的缺点,即在没有信号驱动(三态)的情况下,戴维宁端接的电压选择在输入电路的阈值电压,这个电压会使NMOS 和PMOS 导通,在CMOS 逻辑电路里会引起很大的能量消耗,使芯片过热。

戴维宁端接比较适合TTL 电路,特别是FAC T 电路和驱动能力不足的情况,如很重负载的VME 背板总线结构。

313 AC 端接AC 端接是指在负载端接一电阻和电容,电阻的阻值等于传输线特征阻抗,用于减少反射,电容用于减少直流消耗,通常要求RC 时间常数应大于信号线传输延迟的2倍,根据这条规律来取电容值。

AC 端接的缺点是增加了信号的延迟时间,不适合超高速电路应用。

314 串行端接串行端接是指在源端串接一电阻,其阻值加上驱动器的输出电阻值应等于传输线的特征阻抗,它通过源端匹配来减少信号的反射。

这种端接的优点是使用方便,能量消耗小,而且对于串扰有很好的抑制能力,广泛应用于C MOS 、FAC T 和EC L 电路,特别适合点对点的单向或双向驱动情况。

这种端接方法的缺点是多数驱动器的输出阻抗是非线性的,并随信号的逻辑状态而变化,如通常的CMOS 电路的高电平的输出电阻要大于低电平的输出电阻,因而较难和特征阻抗匹配。

另一个缺点是在信号线上有半波幅度信号出现,因而不适合单点对多点的分布负载端接。

315 二级管端接二极管端接是在信号线上分别对地和对电源接箝位二极管来实现的,它能有效减少过冲,为能充分发挥作用,要求二极管的导通时间要小于1/4的信号上升时间,同时还应具有短的恢复时间。

这种端接的优点是不要求阻抗匹配,能量消耗很小,可放置在信号线的任意位置,这种端接特别适合信号连接复杂的情况,如具有三态的背板总线结构。

它的缺点是对二极管性能要求严格,不满足要求的二极管往往产生更糟的结果。

4 端接的应用和仿真结果信号的反射是与驱动器的输出特性、接收器的输入特性、传输线的特征阻抗、负载情况和连接的拓扑结构密切相#82#系统工程与电子技术2000年关的,是一个复杂的过程[2],因此应对信号的端接进行仿真。

常用的仿真模型有三种,即Bergeron 图[3]、SPICE 模型和IBIS(Input/Output Buffer Information Specification)模型[4]。

Bergeron 图是手工计算方法,主要根据输入输出特性曲线来粗略估计反射和端接效果,这种方法的优点是简单、方便,缺点是不准确。

SPICE 模型是元件电路级的仿真,它提供详尽的电路信息,适合很复杂情况和更详细的仿真。

IBIS 模型是行为级仿真,它提供驱动器和接收器的行为描述,但不泄漏电路内部构造的细节,是一种快速、简洁和准确的仿真方法,这里采用IBIS 模型仿真。

411 影响信号端接的几个关键因素(1)传输线的特征阻抗Z 0,它决定端接电阻值,通常取值为508。

PCB 板的传输线形式主要有两种,带状线和微带线。