DSP实验定时器中断实验精

汕头大学电子系DSP实验报告4(精)

汕头大学实验报告学院: 工学院系:电子工程系专业:电子信息工程年级:09 成绩:实验五定时器及中断实验一、实验目的1. 熟悉CCS开发环境2. 熟悉DSP 54X EVM板的硬件环境3. 了解DSP 54X定时器工作原理4. 了解DSP 54X中断原理及中断向量表建立5. 了解数码LED显示原理(动态扫描)6. 掌握键盘扫描原理7. 掌握DSP 54X I/O寻址方式8. 掌握长整型数的运算9. 掌握中断优先级设置10. 掌握全局变量、局部变量的概念二、实验原理1、定时器及中断实验用行扫描法,读取键值;定时器进行不断地刷新LED的显示;使用外部中断来实现功能的切换(正计数,倒计数,复位)。

2、AD/DA实验采用DSP McBSP串口原理设置,TLV2544ID为I/O模式,位操作控制。

构建SPI 协议进行传输。

三、实验内容与基本要求1、定时器及中断实验1 实验内容DSP初始化定时器0初始化中断寄存器初始化中断向量表定时器中断服务程序(LED扫描驱动程序键盘扫描驱动程序外部中断1中断服务程序2 基本要求通过定时器启动中断,在中断服务程序中扫描数码LED显示,由扫描键盘得到不同的键值,根据不同的键值完成正计数、倒计数、停止、复位等功能。

外部中断可终止计数。

2、A/D-D/A 实验实验内容DSP初始化LCD初始化LCD显示驱动A/D 芯片TLV2544初始化;D/A 芯片TLV5638初始化;DSP McBSP串口2初始化为I/O模式;按A/D、D/A芯片时序,用DSP构建SPI协议;基本要求设置串口2为I/O模式,用DSP构建SPI协议:输入直流信号,启动A/D采样,将采样数据显示在LCD上,比较采样数据与计算值应一致;(在EVM板上有3个按键,可分别产生0.8V,1.2V,1.6V直流电压),并修改原来程序,使扩展到可以在CCS观看波形。

四、实验程序框图1、定时器及中断实验初始化主程序DSP初始化调初始化程序定时器0初始化定时器0,外部中断1使能读键值并延时(100ms)消抖是空键?YLCD初始化、设置LCD显示N数码LED显示使能由不同的键值调不同的子程序结束EXIT1中断程序T0中断程序清标志寄存器调LED显示库函数设置LCD显示位码计数器+1结束N计数值=6?Y位码计数器=0结束正计数子程序调延时程序长型计数器+1NN标志寄存器=0?计数值=1000000?YY结束长型计数器=0长型数转换为BCD送显示缓存器2、A/D-D/A 实验主程序初始化程序调初始化程序DSP初始化Mcbsp2初始化读键值并延时(100ms)消抖AD/DA 初始化是空键?YNLCD初始化、设置LCD显示外部中断1使能由不同的键值调不同的子程序结束ADC程序DAC程序调LCD显示库函数调LCD显示库函数清DA输出值=0,启动ADC, 采样4次, 取平均值启动DAC结果转换为浮点数送显示缓存器调延时子程序设置LCD显示DA输出值+1调延时子程序N输出值=4096N标志寄存器=0?Y标志寄存器=0?YNY结束结束注:当输入为直流信号时:EXIT1中断程序AI=VCC*R0/(R0+RZ其中RZ=R1+R2+R3+R4S1按键:RZ=R1,AI= VCC*R0/(R0+R1清标志寄存器S2按键:RZ=R1+ R2,AI= VCC*R0/(R0+R1+R2设置LCD显示S3按键:RZ=R1+ R2+R3,AI= VCC*R0/(R0+R1+R2+R3结束五、问题1.请解释C54定时器初始化步骤,并解释定时器中断在该实验中的作用。

DSP中断设计实验

中断设计实验学院:物电学院专业:电子信息工程班级:0904 姓名:叶俊学号:2009112030415一:实验任务1.熟悉ARM/DSP/FPGA实验箱的DSP模块2.熟悉DSP的中断的原理3.掌握如何编写DSP中断服务子程序二:实验工具1.具有USB接口的PC机一台2.USB仿真器一台3.ARM/DSP/FPGA实验箱一台三:实验内容(包括实验步骤,电路,程序)本实验是在学生基本上了解DSP的GPIO使用的基础上,进一步学习如何在DSP内部实现中断服务程序的编写。

在TMS320VC5410A的DSP中,可以管理多达29个中断,其中包括1个非屏蔽中断(NMI)、14个软件中断(SINT)、4个外部中断(EINT)、1个定时器中断(TINT)、3个串口接收中断(RINT)、3个串口发送中断(XINT)、2个DMA中断(DMAC)以及1个主机接口中断(HINT)等,表4.3.1是该芯片中支持的所有中断类型、中断好、相对中断偏移地址以及中断优先级等。

要正确的完成整个中断服务程序有以下几种方式:1)在中断向量表中对应的中断向量处放置中断跳转命令,跳转至相应的中断服务程序(该方式实现最直接、最易理解,本实验机采用该方式实现中断,)。

2)利用CCS的CSL库中的函数来实现。

3)利用DSP/BIOS来实现。

第二种和第三种方式在后面的实验中会介绍并使用到。

完成一个完整的中断过程可以分为以下几步:1)首先在C文件或者asm文件中编写好相应的中断服务子程序。

2)在中断向量表(vectors.asm)中相应的中断处放置中断跳转指令,转到1)中编写的函数处(需要注意的是,如果是在C文件中编写的函数,在汇编中调用是需要在函数名称前加下划线‘_’)。

3)在主程序中初始化相应的中断屏蔽寄存器(IMR)和中断标志寄存器(IFR),在IFR中清除相应中断标志,并在IMR中使能相应中断。

4)使能全局中断,即将ST1寄存器中的INTM位清零。

dsp实验:定时器

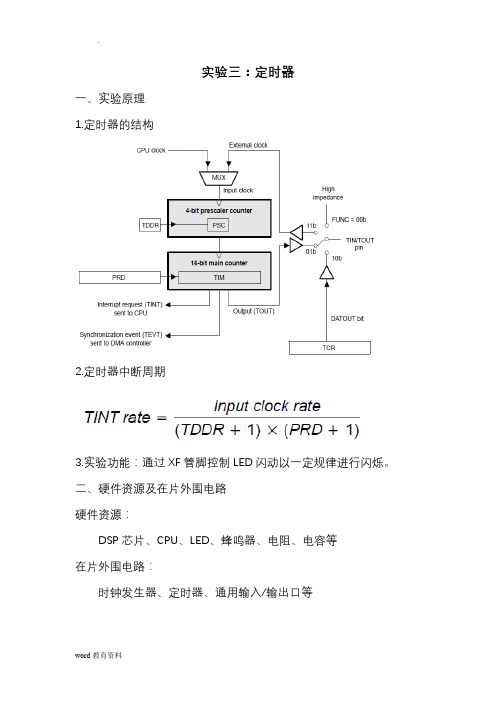

实验三:定时器一、实验原理1.定时器的结构2.定时器中断周期3.实验功能:通过XF管脚控制LED闪动以一定规律进行闪烁。

二、硬件资源及在片外围电路硬件资源:DSP芯片、CPU、LED、蜂鸣器、电阻、电容等在片外围电路:时钟发生器、定时器、通用输入/输出口等三、参数设置CPU工作时钟:*clkmd =0x21b3;0010000110110011CLKOUT=18M中断频率:9 /* PRSC 4bit*/18M/9000=2KHZ 四、实验流程图五、程序#include <stdio.h>#include <csl.h>#include <csl_irq.h>#include <csl_timer.h>#include <csl_chiphal.h>extern void VECSTART(void);#define TIMER_CTRL TIMER_TCR_RMK(\TIMER_TCR_IDLEEN_DEFAULT, /* IDLEEN == 0 */ \TIMER_TCR_FUNC_OF(0), /* FUNC == 0 */ \TIMER_TCR_TLB_RESET, /* TLB == 1 */ \TIMER_TCR_SOFT_BRKPTNOW, /* SOFT == 0 */ \TIMER_TCR_FREE_WITHSOFT, /* FREE == 0 */ \TIMER_TCR_PWID_OF(0), /* PWID == 0 */ \TIMER_TCR_ARB_RESET, /* ARB == 1 */ \TIMER_TCR_TSS_START, /* TSS== 0 */ \TIMER_TCR_CP_PULSE, /* CP== 0 */ \TIMER_TCR_POLAR_LOW, /* POLAR == 0 */ \TIMER_TCR_DATOUT_0 /* DATOUT == 0 */ \)/* Create a TIMER configuration structure that can be passed *//* to TIMER_config CSL function for initialization of Timer *//* control registers. */ TIMER_Config timCfg0 = {TIMER_CTRL, /* TCR0 */// 0x3400u, /* PRD0 0x3400=13312*/ 14400, /* PRD0 16bit0x3400=144000=14400*10*/9 /* PRSC 4bit*/}; //中断频率=Fcpu/(9000*1)=144MHz/13312=1kHzUint16 eventId0;/* Create a TIMER_Handle object for use with TIMER_open */ TIMER_Handle mhTimer0;volatile Uint16 timer0_cnt = 0;/* Function/ISR prototypes */interrupt void timer0Isr(void);int old_intm;Uint16 tim_val;Uint16 xfchange = 0;Uint16 ms,f;void main(void){/* Initialize CSL library - This is REQUIRED !!! *//*CLS库的初始化,这是必需的*/CSL_init();/* Set IVPH/IVPD to start of interrupt vector table *//*修改寄存器IVPH,IVPD,重新定义中断向量表*/IRQ_setVecs((Uint32)(&VECSTART));/* Temporarily disable all maskable interrupts *//*禁止所有可屏蔽的中断源*/old_intm = IRQ_globalDisable();/* Open Timer 0, set registers to power on defaults *//*打开定时器0,设置其为上电的的默认值,并返回其句柄*/ mhTimer0 = TIMER_open(TIMER_DEV0, TIMER_OPEN_RESET);/* Get Event Id associated with Timer 0, for use with *//* CSL interrupt enable functions. *//*获取定时器0的中断ID号*/eventId0 = TIMER_getEventId(mhTimer0);/* Clear any pending Timer interrupts *//*清除定时器0的中断状态位*/IRQ_clear(eventId0);/* Place interrupt service routine address at *//* associated vector location *//*为定时器0设置中断服务程序*/IRQ_plug(eventId0,&timer0Isr);/* Write configuration structure values to Timer control regs */ /*设置定时器0的控制与周期寄存器*/TIMER_config(mhTimer0, &timCfg0);/* Enable Timer interrupt *//*使能定时器的中断*/IRQ_enable(eventId0);/* Enable all maskable interrupts *//*设置寄存器ST1的INTM位,使能所有的中断*/IRQ_globalEnable();/* Start Timer *//*启动定时器0*/TIMER_start(mhTimer0);ms=0;for(;;){// Wait for at least 10 timer periods//等待10个定时周期if(xfchange == 0){//点亮XF的LEDCHIP_FSET(ST1_55,XF,1);}else{//关掉XF的LEDCHIP_FSET(ST1_55,XF,0);}}/* Restore old value of INTM *//*恢复INTM旧的值*/IRQ_globalRestore(old_intm);/* We are through with timer, so close it */ /*关掉定时器0*/TIMER_close(mhTimer0);}/*定时器0的中断程序*/interrupt void timer0Isr(void){ms++;++timer0_cnt;if(timer0_cnt == 500){xfchange = 1;}if(timer0_cnt == 1000){timer0_cnt = 0;xfchange = 0;}}。

DSP原理及其应用实验讲义(精)

DSP 原理及其应用实验讲义CCS 设置1. 安装目标板驱动程序。

点击epp 文件夹下的安装文件,进行安装。

2. 运行Code Composer Studio Setup软件,即点击图标3. 点击Install a Device Driver,选择驱动程序 sdgo5xx32.dll 。

4. 此时,Available Board/Simulator Type一栏中出现相应的驱动图标5. 将图标sdgo5xx32 拖到最左边的System Configuration 一栏中,出现Board Properties 对话框。

6. 点击NEXT ,进入下一页,会显示板卡的I/O口值,修改为0x378,再点击NEXT。

7. 在Processor Configuration 窗中,在Available Processor 中选择TMS320C54XX 然后点击Add Single;对话框右边出现CPU_1图标。

8. 点击NEXT ,进入下一页,选择一个初始化的.gel 文件,本实验系统,选择c5402.gel。

9. 点击finish ,关闭CCS 程序,选择保存。

实验一常用指令实验一实验目的1、了解DSP 开发系统的组成和结构;2、熟悉DSP 开发系统的连接;3、熟悉CCS 开发界面;4、熟悉C54X 系列的寻址系统;5、熟悉常用C54X 系列指令的用法。

二实验设备计算机,CCS2.0版软件,DSP 仿真器,实验箱。

三实验步骤与内容1、系统连接进行DSP 实验之前,先必须连接好仿真器、实验箱及计算机,连接方法如下所示:PCI/USB/EPP2、上电复位在硬件安装完成之后,确认安装正确、各实验部件及电源连接正常后,接通仿真器电源,启动计算机,此时,仿真器上的“红色小灯”应点亮,否则DSP 开发系统有问题。

3、运行CCS 程序待计算机启动成功后,实验箱后面220V 输入电源开关置“ON ”,实验箱上电,启动CCS ,此时仿真器上的“绿色小灯”应点亮,并且CCS 正常启动,表明系统连接正常;否则仿真器的连接、JTAG 接口或CCS 相关设置存在问题,掉电,检查仿真器的连接、JTAG 接口连接,或检查CCS 相关设置是否正确。

DSP实验十三 定时器中断及应用

实验十三 定时器中断及应用

一、实验目的

l、掌握在汇编条件下如何编写中断服务程序; 2、利用定时器中断,来实现一个 8 进制计数器。

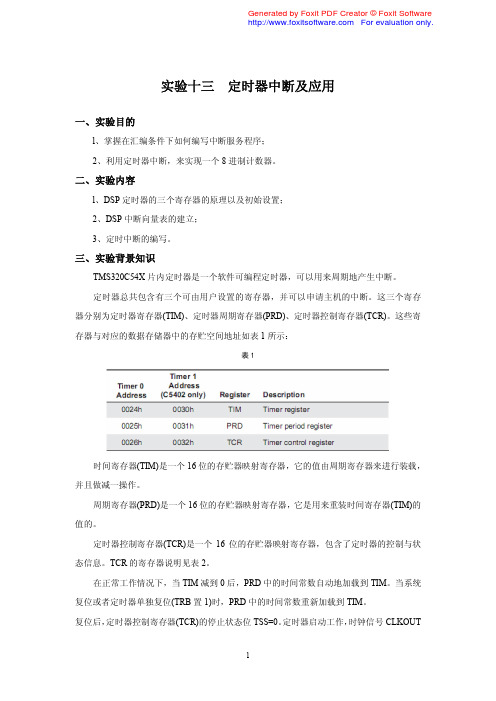

在正常工作情况下,当 TIM 减到 0 后,PRD 中的时间常数自动地加载到 TIM。当系统 复位或者定时器单独复位(TRB 置 1)时,PRD 中的时间常数重新加载到 TIM。 复位后,定时器控制寄存器(TCR)的停止状态位 TSS=0。定时器启动工作,时钟信号 CLKOUT

1

Generated by Foxit PDF Creator © Foxit Software For evaluation only. 加到预定标计算器 PSC。PSC 也是一个减 1 计数器,每当复位或其减到 0 后,自动地将定 时器分频系数 TDDR 加载到 PSC。 PSC 在 CLKOUT 作用下,作减 l 计数。当 PSC 减到 0,产生一个借位信号,令 TIM 作 减 l 计数。TIM 减到 0 后,产生定时中断信号 TINT,传送到 CPU 和定时器输出引脚 TOUT。 因此,定时中断的周期为: CLKOUT*(TDDR+1)*(PRD+1) 其中,CLKOUT 为时钟周期,TDDR 和 PRD 分别为定时器的分频系数和时间常数。 表2

B$

/*******************************************

* 时钟中断处理程序

*

*******************************************/

timerint:

CALL _ecounter

DSP中断实验报告lecture5-2011_478507120

实验事件管理器模块(EV)中通用定时器中断操作一、实验目的:1、熟悉事件管理器模块(EV)中通用定时器计时及比较的操作;2、熟悉中断产生过程及中断的配置操作。

二、实验原理及说明:本实验是让XF引脚相连的LED灯0.5s内亮灭一次,采用定时器计时产生中断的方法实现。

实验中外部时钟输入为30MHz,DSP内部锁相环半分频为15MHz,通用定时器1预分频因子为128,所以计算出延迟0.5s周期寄存器的值约为E4E0h(定时器的周期数等于周期寄存器的值加1)。

三、实验内容及步骤:1、新建一个名为interrupt1的工程并向其中添加相应的文件,并做好相应的配置。

2、在工程中新建名为interrupt1.c的源文件。

//step0: 输入所需的头文件和定义用户自己的函数#include "DSP28_Device.h"interrupt void ISRTimer1(void); //定义定时器1周期中断服务//程序void main(void){//step1: 初始化系统控制寄存器,主要内容包括PLL,WatchDog,系统时钟和外设时钟设置;InitSysCtrl(); // 调用DSP28_SysCtrl.c文件中的函数,也就是//说在DSP28_SysCtrl.c文件中完成系统初始化;//step2:初始化所需的通用IO口;InitGpio();// 调用DSP28_Gpio.c文件中的函数,也就是说在//DSP28_Gpio.c 文件中完成通用IO口的配置;//step3: 初始化系统中断//关闭CPU中断DINT;IER = 0x0000;IFR = 0x0000;//初始化PIE控制寄存器;InitPieCtrl(); //在DSP28_PieCtrl.c文件中要打开所需外设中断;//初始化PIE中断矢量表,设置成默认状态;InitPieVectTable(); //在DSP28_PieVect.c文件中完成;//step4:初始化所需的外设(包括事件管理器EV模块、ADC模块、CAN //总线模块等)InitPeripherals(); //在DSP28_InitPeripherals.c文件中完成//step5: 使用用户所需的函数、重新指定中断矢量(可选择的)、开用//户所需中断EALLOW; //EALLOW和EDIS已经在头文件中定义了PieVectTable.T1PINT = &ISRTimer1; //更该定时器1周期中断服//务程序地址EDIS;//开中断IER |= M_INT2; //开中断2,M_INT2已经在头文//件中定义EINT;EvaRegs.T1CON.all=EvaRegs.T1CON.all|0x0040; //启动Timer1//step6:无限空循环,等待中断(可选择)while(1){;}}//step7:用户自定义函数interrupt void ISRTimer1(void) //定时器1周期中断服务程序{double i;asm(" SETC XF ");for(i=0;i<50000;i++){;}asm(" CLRC XF ");PieCtrl.PIEACK.all=0x0002; //清除PIEACK中断标志位EvaRegs.T1CNT=0x0000; //Timer1的计数器重新赋0EvaRegs.EVAIFRA.all=EvaRegs.EVAIFRA.all&0x0080; //清除定//时器1周期中断标志IER |= M_INT3; //使能定时器2的中断EINT; //开CPU中断ERTM; // Enable Global realtime interrupt DBGM}在主程序中调用相关的初始化程序,完成相关的初始化工作,而中断程序中完成的是控制LED灯亮灭的功能。

DSP实验报告定时器2

实验二DSP系统定时器的使用一、实验目的:1、掌握5402 DSP片上定时器的初始化设置及应用;2、掌握DSP系统中实现定时的原理及方法;3、了解5402 DSP中断寄存器IMR、IFR的结构和使用;4、掌握5402 DSP系统中断的初始化设置过程和方法;5、掌握在C语言中嵌入汇编语句实现数字I/O的方法。

二、实验原理:1、定时器及其初始化在5402内部包括两个完全相同的定时器:定时器0和定时器1。

每个定时器分别包括3个寄存器:定时器周期寄存器PRD、定时器寄存器TIM、定时器控制寄存器TCR,其中TCR 寄存器中包括定时器分频系数TDDR、定时器预分频计数器PSC两个功能寄存器。

通过PRD 和TDDR可以设置定时器的初始值,TIM(16bits)和PSC(4bits)是用于定时的减法计数器。

CLKOUT是定时器的输入时钟,最大频率为100Mhz。

定时器相当于20bit的减法计数器。

定时器的结构如图1所示。

图1 定时器的组成框图定时器的定时周期为:CLKOUT×(TDDR+1)×(PRD+1)其中,CLKOUT为时钟周期,TDDR和PRD分别为定时器的分频系数和时间常数。

在正常工作情况下,当TIM减到0后,PRD中的时间常数自动地加载到TIM。

当系统复位或者定时器单独复位时,PRD中的时间常数重新加载到TIM。

同样地,每当复位或PSC减到0后,定时器分频系数TDDR自动地加载到PSC。

PSC在CLKOUT作用下,作减1计数。

当PSC 减到0时,产生一个借位信号,令TIM作减l计数。

TIM减到0后,产生定时中断信号TINT,传送至CPU和定时器输出引脚TOUT。

例如:欲设置定时器0的定时周期为1ms,当DSP工作频率为100Mhz时,通过上式计算可得出:TDDR=15,PRD=6520。

2、定时器的使用下面是一段定时器应用程序,每检测到一次中断,ms+1,利用查询方式每计500个数就令XF引脚的电平翻转一次,在XF引脚输出一矩形波信号,因定时器1ms中断一次,故500ms就使LED翻转一次,这样LED指示灯就不停地闪烁。

DSP定时器与中断系统的使用实验报告

贵州大学实验报告学院:电气工程学院专业:电子信息工程班级:电信091 姓名徐朝忠学号0908040224 实验组实验时间2012年12月指导教师尉学军老师成绩实验项目名称DSP定时器与中断系统的使用实验目的1. 掌握TMS320C54x定时器的工作原理和初始化步骤2. 掌握DSP的中断结构和对中断的处理流程实验要求①根据本实验的特点、要求和具体条件,采用教师简单讲解,学生自己动手操作的形式;②学生实验时,并严格遵守实验室规则、安全制度和学生实验守则;③认真学习实验操作技能,严格按指导书和实验指导教师的指导操作有关仪器设备,不要做与本实验无关的事情;④做好实验预习、实验记录,并按要求按时完成实验报告。

实验原理译码后地址是03002HDSP的工作主频为8MHz,设置定时时间125ms,每定时器中断4次,正好为0.5s。

每0.5s 亮一次,灭一次,正好1s闪烁一次。

实验仪器计算机一台(安装CCS3.3)、ICETEC-VC5415-A试验箱实验步骤1、将试验箱<<DSP教学实验系统>>的JTAG连到ICETEC-VC5415-A板上,接好电源和USB接口。

2、进入CCSsetup,设置运行环境为3、输入程序:源程序1.Time1.asm.mmregs.bss count,1.bss x,1.def _main,_time1 TIMO .set 0024HPRD0 .set 0025HTCR0 .set 0026HPA1 .SET 3002H.text_main: STM #count,AR1 ST #4,*AR1STM #0008H,TCR0STM #0F423H,PRD0STM #042FH,TCR0STM #0008H,IMRSTM #0008H,IFRRSBX INTMSTM x,AR5ST #55H,*AR5PORTW *AR5,PA1stm #00A0H,PMST loop1: B loop1_time1: PSHM TRNPSHM TPSHM ST0PSHM ST1ADDM #-1,*AR1CMPM *AR1,#0BC still_wait,NTCPORTR 3002h,*AR5LD *AR5,AXOR #0ffh,0,A,ASTL A,*AR5PORTW *AR5,PA1ST #4,*AR1still_wait: POPM ST1 ;POPM ST0POPM TPOPM TRNRETE.end输入中断向量程序:.sect ".vectors.ref _main ; C entry point.align 0x80 ; must be aligned on page boundary RESET: ; reset vectorBD _main ; branch to C entry pointSTM #200,SP; stack size of 200 nmi: RETE ; enable interrupts and return from oneNOPNOPNOP ;NMI~; software interruptssint17 .space 4*16sint18 .space 4*16sint19 .space 4*16sint20 .space 4*16sint21 .space 4*16sint22 .space 4*16sint23 .space 4*16sint24 .space 4*16sint25 .space 4*16sint26 .space 4*16sint27 .space 4*16sint28 .space 4*16sint29 .space 4*16sint30 .space 4*16int0: RETENOPNOPNOP int1: RETENOPNOPNOP int2: RETENOPNOPNOP tint: B _time1.ref _time1NOPNOP rint0: RETENOPNOPNOP xint0: RETENOPNOPNOP rint1: RETENOPNOPNOP xint1: RETENOPNOPNOP int3: RETENOPNOPNOP.end *.CMD 文件:-w-stack 400h-heap 100-l rts.libMEMORY{PAGE 0:VECT : o=80h,l=80hPRAM : o=100h,l=1f00hPAGE 1:DRAM : o=2000h,l=1000h}SECTIONS{.text : {}> PRAM PAGE 0.data : {}> PRAM PAGE 0.cinit : {}> PRAM PAGE 0.switch : {}> PRAM PAGE 0.const : {}> DRAM PAGE 1.bss : {}> DRAM PAGE 1.stack : {}> DRAM PAGE 1.vectors: {}> VECT PAGE 0}4.编译链接,5.运行,观察试验箱中发光二级管的变化情况6.修改发光二级管的初始状态,观察其变化情况。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验四定时器中断实验一:实验目的1.熟悉定时器初始化的步骤;2.熟悉定时器控制寄存器(TCR)的含义和使用;3.熟悉定时器的原理和应用。

二:实验内容本实验要求编写一个简单的定时器中断程序,设置一定的周期控制与XF引脚相连的LCD指示灯。

当定时器中断产生时可以观察到LCD周期性闪烁。

三:实验原理1.定时器SRESET.C54xx 系列的 DSP 都具有一个或两个预定标的片内定时器,这种定时器是一个倒数定时器,它可以被特定的状态位实现停止、重启动、重设置或禁止。

定时器在复位后就处于运行状态,为了降低功耗可以禁止定时器工作。

应用中可以用定时器来产生周期性的 CPU 中断或脉冲输出。

定时器的功能方框图如图 9.1 所示,其中有一个主计数器( TIM )和一个预定标计数器( PSC )。

TIM 用于重装载周期寄存器 PRD 的值, PSC 用于重装载周期寄存器 TDDR 的值。

图5.1中有一个信号,是在器件复位时,DSP向外围电路(包括定时器)发送的一个信号,此信号将在定时器上产生以下效果:寄存器TIM和PRD装载最大值(0FFFFH);TCR的所有位清0;结果是分频值为0,定时器启动,TCR的FREE 和SOFT为0。

图5.1定时器的功能方框图定时器实际上是有20bit的周期寄存器。

它对CLKOUT信号计数,先将PSC(TCR 中的D6~D9位)减1,直至PSC为0,然后把TDDR(TCR中的低4位)重新装载入PSC,同时将TIM减1,直到TIM减为0。

这时CPU发出TINT中断,同时在TOUT引脚输出一个脉冲信号,脉冲宽度与CLKOUT一致,然后将PRD重新装入TIM,重复TSS下去直到系统或定时器复位。

定时器产生中断的计算公式如下:1PRD+1TINT的频率= × × (其中tc为 CLKOUT的周期定时器由三个寄存器组成:TIM、PRD、TCR。

TIM:定时器寄存器,用于装载周期寄存器值并自减1。

PRD:周期寄存器,用于装载定时器寄存器。

TCR:定时器控制寄存器,包含定时器的控制状态位。

定时器是一个片内减计数器,用于周期地产生CPU中断。

定时器被预定标计数器所触发,后者每个CPU时钟周期减1,当计数器减至0时,会产生一个定时器中断,同时在下一周期计数器被定时周期值重新装载。

在正常操作模式下,当TIM自减至0时,TIM将被PRD内的数值重装载。

在硬件复位或定时器单独复位(TCR中TRB位置1)的情况下,主定时器模块输出的是定时器中断(TINT)信号。

该中断被发送至CPU,同时由TOUT引脚输出。

TOUT脉冲的宽度等于CLKOUT的时钟宽度。

预定标模块由两个类似TIM和PRD的单元构成。

它们是预定标计数器(PSC)和定时器分频寄存器(TDDR)。

PSC、TDDR是RCR寄存器的字段。

在正常操作时PSC自减为0,TDDR值装入PSC,同样在硬件复位或定时器单独复位的情况下,TDDR也被装入PSC。

PSC被CPU时钟定时,即每个CPU时钟使PSC自减1。

PSC可被TCR读取,但不能直接写入。

当TSS置位时,定时器停止工作。

若不需要定时器,终止定时操作,可使芯片工作在低功耗模式,并且可以使用与定时器相关的两个寄存器(TIM和PRD)作为通用的存储器单元,可以在任意周期对它们进行读或写操作。

TIM的当前值可被读取,PSC也可以通过TCR读取。

因为读取这两个存储器需要两个指令,而在两次读取之间因为自减,数值可能改变,因此,PSC两次读的结果可能有差别,不够准确。

若要准确测量时序,在读这两个寄存器值之前可先中止定时器,对TSS置1和清0后,可重新开始定时。

通过TOUT信号或中断,定时器可以用于产生周边设备的采样时钟,如模拟接口。

对于有多个定时器的DSP,由寄存器GPIOCR中的第15位控制使用某一个定时器产生的TOUT信号。

2.定时器初始化(1)定时器初始化步骤●TCR的TSS位写1,定时器停止工作;●装载TRD;●初始化TCR中的TDDR,并对TCR中的TSS置0,对TRB置1来重装载定时器周期。

(2)初始化定时器中断方法(INTM=1)●FIR中的TINT写1,以清除挂起的定时器中断;●IMR中的TINT置1,启动定时器中断;●启动全部中断,INTM置0;●在重启(RESET)后,TIM和PRD被设置为最大值(FFFFH),TCR中的TDDR置0。

(3)定时控制寄存器(TCR)TCR为一个映射到片内的16位寄存器,它可以控制:●定时器的工作方式;●设定预定标计数器中的当前数值;●启动或停止定时器;●重新装载定时器;●设置定时器的分频值。

TCR的位描述如图5.215~12 11 10 9~6 5 4 3~0Reserved SOFT FREE PSC TRB TSS TDDR图5.2TCR位描述●第15~12位Reserved:保留位,总为0。

●第11~10位SOFT、FREE:特殊的仿真位。

高级语言调试程序中出现一个断点时,该仿真位决定定时器的状态。

如果FREE位设为1,则当遇到一个断点时,定时器继续运行(即自由运行),在这种情况下,SOFT被忽略。

但是,如果FREE 为0,则SOFT有效。

在此情况下,如果SOFT=0,则定时器停止,下一次TIM 的值递减;如果SOFT=1,则当TIM减到0,定时器停止工作。

●第9~6位PSC:定时器预定标计数器。

这4位用来保存定时器的当前预定标计数器。

每个CLKOUT周期内,若PSC值大于0,PSC减1,在PSC减到0后的下个CLKOUT周期内,装载TDDR的内容,并且TIM减1。

每当软件设置了定时器重载位(TRB)时,PSC也被重新装载。

可通过TCE检测PSC,但PSC不能直接设置,PSC值必须从TDDR中提取。

复位时,PSC设为0。

●第5位TRB:定时器重载位。

当TRB写入1时,TIM装载PRD中的值,并且PSC装载TDDR中的值。

TRB位总被读为0。

●第4位TSS:定时器停止状态位。

TSS停止或重新启动定时器。

复位时,TSS清零,并且立即启动定时器。

TSS=0,启动或重新启动定时器;TSS=1,停止定时。

注意,此位为只读位,读出的值永远为0。

●第3~0位TDDR:定时器分频比寄存器。

每经过(TDDR+1)个CLKOUT周期,TIM减1。

复位时,TDDR位清0。

如果想通过一个整数因子增加总的定时计数值,则将整数因子减1后写入这4位。

当PCS值为0时,在随后的一个CLKOUT周期内,TDDR内容将被重新装入PSC,并且TIM减1。

每当TRB重载入时,TDDR也将被PSC重新装载。

3:定时器应用:C54x定时器所能计计时的长度可通过公式Tx(TDDR+1×(PRD+1来计算,其中,TDDR最大值为0FH,PDR最大值为0FFFFH,所以能计时的最长长度为T×1048576,由所采用的机器周期T决定,例如f=4MHz,T=250,则最长定时时间为:Tmax=250×1048576=262.144(ms例如若需要更长的计时时间,则可以在中断程序中设计一个计数器。

设计一个周期为40s的方波,可将定时器设置为100ms,程序计数器设为200,当计数200×100ms=20s时输出取值一次,可形成所要求的波形。

四:实验步骤本实验的步骤为:(1)连接好实验板,选择相应的CCS 运行环境。

(2)新建工程,添加TIME文件及其配制文件,用编译链接工具条对文件进行编译链接,如果编译链接错误提示为“0Errors”,则把.out文件下载到目标板,然后再单击图6.3中的运行工具运行程序,这时可以看到目标板上和XF引脚的LED在周期性闪烁。

(3)选择菜单View→CPU Registers→CPU Registers命令,可以观察到累加器A 在不断加1,如图5.3所示。

图5.3 CPU 寄存器(4)参考程序如下;.mmregs.global mainintktcr .set 0029hktcrstop .set 0010h;TCR 定时器控制寄存器各位含义如下:;RES SOFT FREE PSC TRB TSS TDDR;00000 0 0000 1 0 (TSS=1时停止定时) 1001;**********************定时器参数定义***************************************Tim0 .set 24h ;timer0 registerPrd0 .set 25h ; timer0 period counterTcr0 .set 26h ; timer0 control registerperiod .set 99 ;定时器周期;*********************************************************************** ******.sect "vectors";**********************中断向量表*****************************************vector: b mainintnopnopnmi: retenopnopnopsint17: retenopnopnopsint18: retenopnopnopsint19: retenopnopnopsint20: rete nopnopnopsint21: rete nopnopnopsint22: rete nopnopnopsint23: rete nopnopnopsint24: rete nopnopnopsint25: rete nopnopnopsint26: rete nopnopnopsint27: rete nopnopnopsint28: rete nopnopnopsint29: rete nopnopnopsint30: rete nopnopnopint0: rete nopnopnopint1: retenopnopint2: rete nopnopnopb tint0 nopnopbrint0: rete nopnopnopbxint0: rete nopnopnoptrint: rete nopnopnop txint: rete nopnopint3: retenopnopnophpint: retenopnopnopq26: .word 0ff80h.word 0,0,0q27: .word 0ff80h.word 0,0,0q28: .word 0ff80h.word 0,0,0q29: .word 0ff80h.word 0,0,0q30: .word 0ff80h.word 0,0,0q31: .word 0ff80h.word 0,0,0;************************************************************************ *.textmainint: stm #203FH,PMST ;从定位中断向量表到2000H处ssbx intm ;关中断ssbx sxmssbx frct ;允许小数乘法ld #0,dpstm #0008h,imr ;允许定时器0中断;************************************************************************ **;允许定时器0中断,IMR 寄存器各位含义如下:;RES DMAC5 DMAC4 BXINT1 BRINT1 HINT INT3 TINT DMAC0 BXINT0 BRINT0 TINT0 INT2 INT1 INT0;00 0 0 0 0 0 0 0 0 0 0 1 0 0 0;************************************************************************ ***stm #ktcrstop,tcr ;停止定时stm #period,tim ;设定定时器寄存器stm #period,prd ;设定定时器周期寄存器stm #ktcr,tcr ;启动定时器stm #0008h,imr ;允许TIMER0中断stm #0ffffh,ifr ;清中断rsbx intm ;开中断wait: nop ;循环,等中断b wait;**************************定时器中断程序*********************************;************************************************************************ *tint0:add #1,A ;A寄存器加1操作stm #20,*ar2stm #20,*ar1aa:ssbx xf ;XF引脚置高,LCD亮rpt #8000 ;重复8001次nop ;等待rpt #8000 ;重复8001次nop ;等待rpt #8000 ;重复8001次nop ;等待rpt #8000 ;重复8001次nop ;等待rpt #8000 ;重复8001次nop ;等待rpt #8000 ;重复8001次nop ;等待rpt #8000 ;重复8001次nop ;等待rpt #8000 ;重复8001次nop ;等待rpt #8000 ;重复8001次nop ;等待banz aa,*ar1-bb:rsbx xf ;XF引脚置低,LCD灭rpt #8000 ;重复8001次nop ;等待rpt #8000 ;重复8001次nop ;等待rpt #8000 ;重复8001次nop ;等待rpt #8000 ;重复8001次nop ;等待rpt #8000 ;重复8001次nop ;等待rpt #8000 ;重复8001次nop ;等待rpt #8000 ;重复8001次nop ;等待rpt #8000 ;重复8001次nop ;等待rpt #8000 ;重复8001次nop ;等待banz bb ,*ar2-rete ;中断返回.end配置文件如下:time.obj-o time.out-m time.map-e mainintMEMORY{PAGE 0:EPROM :org=2000h,len=1000hPAGE 1:SPRAM :org=0060h,len=100h}SECTIONS{vectors :> EPROM PAGE 0.text :> EPROM PAGE 0}五:实验报告要求:1. 运行源程序,观察实验结果,看到XF引脚的LED周期性地变化,修改定时器参数,改变LED闪烁周期。