8086CPU引脚

8086引脚信号

11

1). 数据和地址引脚

A19/S6~A16/S3(Address/Status)

地址/状态分时复用引脚,输出、三态 这些引脚在访问存储器的第一个时钟周期T1时刻输 出高4位地址A19~A16 在访问外设的第一个时钟周期全部输出低电平无效

ⅰ)S6为0,表明AD15~AD0作为数据线;

在总线周期的T2-T4时,这4条线作为输出CPU的状态信息。

28

“引脚”小结

CPU引脚是系统总线的基本信号 可以分成三类信号: 16位数据线:D15~D0 20位地址线:A19~A0 控制线:

ALE、M/IO*、WR*、RD*、READY

INTR、INTA*、NMI,HOLD、HLDA

RESET、CLK、Vcc、GND

29

系统总线的形成

14

2). 读写控制引脚

M/IO*(Memory/Input and Output) 存储器或I/O访问,输出、三态 该引脚输出高电平时,表示CPU将访问 存储器,这时地址总线A19~A0提供20 位存储器地址 该引脚输出低电平时,表示CPU将访问 I/O端口,这时地址总线A15~A0提供16 位I/O口地址

21

3). 中断请求和响应引脚

NMI(Non-Maskable Interrupt)

非屏蔽中断请求,输入、上升沿有效 有效时,表示外界向CPU申请不可屏蔽中断 该请求的优先级别高于INTR,并且不能在CPU 内被屏蔽 当系统发生紧急情况时,可通过他向CPU申请 不可屏蔽中断服务

主机与外设进行数据交换通常采用可屏蔽中断 不可屏蔽中断通常用于处理掉电等系统故障

23

4). 总线请求和响应引脚

第5讲、8086_8088微处理器引脚功能、总线结构和时序

第五讲8086/8088微处理器引脚功能、总线结构和时序第一节、8086/8088引脚信号和功能第二节、8086/8088最小模式和最大模式第三节、8086/8088主要操作第四节、8086存储器的分体结构第一节8086/8088引脚信号和功能一、8086/8088的两种工作模式二、8086/8088引脚信号和功能一、8086/8088的两种工作模式8086/8088CPU有两种模式:最小模式和最大模式。

y最小模式系统中只有8086/8088一个微处理器(单处理器模式)。

所有的总线控制信号都直接由8086/8088产生。

总线控制逻辑电路被减少到最小。

适合于较小规模的系统。

y最大模式包含两个(以上)微处理器,其中一个主处理器是8086/8088,其他的处理器称为协处理器,协助主处理器工作。

适合于中等规模或大型的8086/8088系统中。

系统的控制总线由总线控制器8288来提供:¾8288增强了8088CPU总线的驱动能力;¾将8086的状态信号(S2~S0)进行译码,提供8086对存储器、I/O接口进行控制所需的信号。

最小模式与最大模式的主要区别8086/8088外部引脚图(括号内为最大模式时引脚名)8088地A14A13A12A11A10A9A8AD7AD6AD5AD4AD3AD2AD1AD0NMI INTR CLK 地Vcc(5V)A15A16/S3A17/S4A18/S5A19/S6SS0(HIGH)MN/MX RDHOLD(RQ/GT0)HLDA(RQ/GT1)WR(LOCK M/IO DT/R(S1)DEN(S0)ALE(QS0)INTA(QS1)TEST READY RESETVcc(5V)AD15A16/S3A17/S4A18/S5A19/S6BHE/S7MN/MX RDHOLD (RQ/GT0)HLDA (RQ/GT1)WR (LOCK)M/IO (S2)DT/R ( S1 )DEN (S0 )ALE (QS0)INTA (QS1)TEST READY RESET8086Vcc(5V)AD15A16/S3A17/S4A18/S5A19/S6BHE/S7MN/MX RDHOLD (RQ/GT0)HLDA (RQ/GT1)WR (LOCK)M/IO (S2)DT/R ( S1 )DEN (S0 )ALE (QS0)INTA (QS1)TEST READY RESET8086(1)地址/数据复用引脚(AD15~AD0 )是分时复用①在总线周期来输出要访问的存储器地址或口地址A15~A②在总线周期的其他时间内,作为双向数据总线:对8086就是(对8088地AD14AD13Vcc(5V)AD15A16/S3A17/S4A18/S5A19/S6BHE/S7MN/MXRDHOLD (RQ/GT0)HLDA (RQ/GT1)WR (LOCK)M/IO (S2)DT/R ( S1 )DEN (S0 )ALE (QS0)INTA (QS1)TESTREADYRESET8861.两种模式下公共引脚(2) 地址/状态复用引脚A19/S6~ A16/S3分时复用引脚,输出,三态。

8086的引脚功能以及基本知识

8086微处理器由哪几部分组成?各部分的功能是什么?【解】:按功能可分为两部分:总线接口单元BlU(BUSInterfaceUnit)和执行单元EU(ExecutionUnit)。

总线接口单元BlU是8086CPU在存储器和I/O设备之间的接口部件,负责对全部引脚的操作,即8086对存储器和I/O设备的全部操作都是由BIU完成的。

全部对外部总线的操作都必需有正确的地址和适当的限制信号,BIU中的各部件主要是围绕这个目标设计的。

它供应了16位双向数据总线,20位地址总线和若干条限制总线。

其具体任务是:负责从内存单元中预取指令,并将它们送到指令队列缓冲器暂存。

CPU执行指令时,总线接口单元要协作执行单元,从指定的内存单元或I/O端口中取出数据传送给执行单元,或者把执行单元的处理结果传送到指定的内存单元或I/O端口中。

执行单元EU中包含1个16位的运算器A1.U,8个16位的寄存器,1个16位标记寄存器FR,1个运算暂存器和执行单元的限制电路。

这个单元进行全部指令的说明和执行,同时管理上述有关的寄存器。

EU对指令的执行是从取指令操作码起先的,它从总线接口单元的指令队列缓冲器中每次取一个字节。

假如指令队列缓冲器中是空的,WJEU就要等待BIU通过外部总线从存储器中取得指令并送到EU,通过译码电路分析,发出相应限制吩咐,限制A1.U数据总线中数据的流向。

8086的基本总线周期为4个时钟周期,每个时钟周期间隔称为一个T 状态Tl 状态:BlU (总线接口部件)将RAM 或I/O 地址放在地址/数据夏用总线(A/D )上。

T2状态:读总线周期:A/D 总线为接收数据做准备。

变更线路的方向。

写总线周期:A/D 总线上形成待写的数据,且保持到总线周期的结束(T4)。

T3,T4:对于读或写总线周期,AD 总线上均为数据。

还有插入等待周期Tw:当RAV 或I/O 接口速度不够时,T3及T4之间可插入等待状态Tw βTi:当InU 无访问操作数和取指令的任务时,8086不执行总线操作,总线周期处于空闲状态TiO在最小模式中引脚定义GND ・ADl4ADBADUADllADl∙AD9ADt AD7 AD3 ADl 5 6 78 108086H CPU 12 13 14 15 16 17 18 19 20 403938 37 36 35 34 33 3231 302928 27 2625 24 2322 21⅛VCC(÷5V) 1.^^^AD1S AD16/S3 H AD11∕S4・AD18/S5 [ ■她9∕S⅜ 1■ ■^II BHE/S7 M ∙-IM/MXRD 一HO1.D(Wl∕GT0)⅞DA(⅞Q∕GT1)WR(1.OCK) h ⅛M∕iθ⅞) I OT∕R(Si) DEN(So) I 一迎(QSo) -IMTA(QSl) ι⅜TEST - I READY - IESET INTICHGND .AD15~AD0(AddressDataBUS>:16位地址/数据总线,分时复用。

CPU8086 的引脚及其功能

二. 8086/8088CPU引脚及功能

8086/8088CPU引脚如图所示

最大方式

HIGH

(RQ/GTO) (RQ/GT1) LOCK (S2) (S1) (S0) (QS0) (QS1)

8088引脚说明

最小方式

二. 8086/8088CPU引脚及功能

引脚构成了微处理器级总线,引脚 功能也就是微处理器级总线的功能。 8086/8088CPU的40条引脚中,引脚1和 引脚20(GND)为接地端;引脚40(VCC) 为电源输入端,采用的电源电压为+5V。

Χ

三.8086/8088CPU工作于最小方式下 引脚定义与系统总线结构

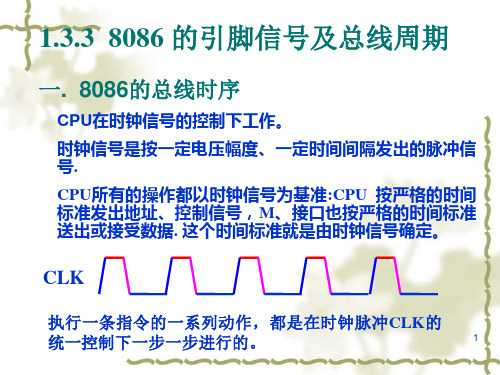

时钟周期 微处理器是在统一的时钟信号CLK

控制下,按节拍进行工作的。8086/8088 的时钟频率为5MHz。时钟周期就是控制 微处理器工作的时钟信号的一个周期 (200ns),它是CPU工作的最小节拍。

Χ

三.8086/8088CPU工作于最小方式下 引脚定义与系统总线结构

二. 8086/8088CPU引脚及功能

最大方式:适合用于实现多处理器系 统,在这种方式中,8088/8086CPU不直接 提供用于存贮器或I/O读写的读写命令等控 制信号,而是将当前要执行的传送操作类 型编码为三个状态位(S2,S1,S0)输出,由 外部的总线控制器8288对状态信号进行译 码产生相应信号。

三.8086/8088CPU工作于最小方式下 引脚定义与系统总线结构

表5.1.1 S4、S3的功能 S4 0 0 1 1 S3 0 1 0 1 段寄存器 ES SS CS(或I/O,中断响应) DS

三.8086/8088CPU工作于最小方式下 引脚定义与系统总线结构

5.A19/S6 –A16/S3 (输出,三态)

8086微处理器引脚

8086微处理器引脚(线)说明﹡8086/8088微处理器采用40条引线双列直插(DIP)封装。

﹡ 8086/8088微处理器引线是对外前端总线及专用信号引线。

﹡ 8086/8088微处理器引线,在逻辑上可分为3类:地址总线信号、数据总线信号、控制总线信号。

还有一些专用信号:电源、地、时钟。

﹡ 8086/8088采用引线分时复用技术,一条引线不同时间代表不同信号,解决引线不够问题。

基本引脚信号﹡AD15~AD0(I/O,三态):地址/数据复用引脚。

﹡A19/S6 ~ A16/S3(O,三态):地址/状态复用引脚。

﹡BHE# /S7 (O,三态):高字节允许/状态复用引脚。

﹡NMI(In):非屏蔽中断请求线,上升边触发。

﹡INTR (In) :可屏蔽中断请求线,高电平有效。

﹡RD# (O,三态) :读选通信号,低电平有效。

﹡CLK (In) : 时钟信号,处理器基本定时脉冲。

﹡RESET (In) :复位信号,高电平有效。

* WR# (O,三态):写选通信号,低电平有效。

﹡READY (In):准备好信号,高电平有效。

处理器与存储器及I/O接口速度同步的控制信号。

﹡TEST# (In): 测试信号,低电平有效。

处理器执行W AIT指令的控制信号。

﹡MN/MX# (In):最大/最小工作模式选择信号。

硬件设计者用来决定8086工作模式,MN/MX# =1 8086为最小模式, MN/MX# =0 8086为最大模式。

﹡Vcc (In): 处理器的电源引脚,接 +5V电源。

﹡GND :处理器的地线引脚,接系统地线2)最小模式下的有关控制信号﹡INTA# (O) :最小模式下的中断响应信号。

﹡ALE (O) :地址锁存允许信号。

﹡DEN# (O,三态) :数据总线缓冲器允许信号。

﹡DT/R# (O,三态) :数据总线缓冲器方向控制信号。

﹡M/IO# (O,三态) :存储器或I/O接口选择信号。

﹡WR# (O,三态) :写命令信号。

第4章 8086CPU引脚功能,系统组成和时序

3.BHE /S7(Bus High Enable/Status)高8位数据总线允许/ 状态复用信号(输出、三态) 在8086系统中: ①在总线周期的T1时钟内,8086在 BHE /S7引脚输出低 电平( BHE = 0)有效信号,表示高8 位数据总线AD8~AD15 上的数据有效;若 BHE = 1,表示当前仅在数据总线 AD0~AD7上传送低8位数据。信号也作为对I/O电路或中断 响应时的片选条件信号。 ②在T2、T3、TW和T4时钟周期, BHE /S7引脚此时输出 状态信息。在8086中,S3、S7状态没有实际定义。 ③ BHE 和AD0信号相配合,可知系统当前的操作类型, 具体规定见表4.2所示。

表4.1 S4、S3的代码组合与当前段寄存器的关系

S4S3

00 01

当前使用的段寄存器

ES段寄存器 SS段寄存器 当存储器寻址时,使用CS寄存器; 当对I/O端操作或中断矢量寻址时,不使用段寄存器。 DS段寄存器

10

11

⑤S5状态指示当前中断允许标志IF 的状态: 如IF = 1,表明当前允许可屏蔽中断请求; 如IF = 0,则禁止可屏蔽中断。 ⑥S6状态为低电平时,表示8086/8088当前正与总线相连。所 以,在T2、T3、TW和T4时钟周期S6总保持低电平。

6.TEST (-Pin23) 测试输入信号(低电平有效) TEST信号与WAIT指令结合起来使用,CPU执行WAIT 指令后,处于等待状态,当 TEST 0 ,系统脱离等待状态, 继续执行被暂停执行的指令。当CPU执行WAIT指令时, CPU每隔 5个时钟周期就对此引脚进行测试。 TEST引脚信号用于多处理器系统中,实现8086/8088 CPU与协处理器间的同步协调之功能。

9.RESET(--Pin21):复位输入信号---高电平有效 RESET信号高电平至少应保持4个时钟周期。随着 RESET变为低电平,CPU就开始执行再启动过程。复位时, CPU内部各寄存器的状态如表4.3所示。

第三章_2_8086-8088_cpu_引脚功能_总线结构和时序

38086/8088 CPU 引脚功能、总线结构和时序3.1.3 8086/8088控制引脚BHE / S7与特殊的存储器结构方式A19A1A0BHESEL A18A0SELA18A奇地址存储体偶地址存储体D7D0D7D0D15D8D7D0图 3.1 8086 存储器结构该复用引脚 S7 1没有明确定义,但 BHE 0 表明 D8 D15高8位数据线有效。

该信号和地址线 A0合起来决定了当前数据在数据总线上以何种格式出现。

该引脚与8086 特殊的存储器结构密切相关。

8086 的 1MB 存储器由两个存储体组合而成。

如图 3.1 所示。

图中偶数与奇数存储总体各占512KB,其选通信号分别为BHE和 A0,偶地址存储体数据线只和低8 位数据总线相连,奇地址存储体数据线只和高 8 为数据总线相连。

这种存储器结构决定了:若A0,=0BHE 0 ,则可在一个总线周期内读/写一个“对准字”,这属于正常操作;若 BHE =1,A=0,则只能从存储器中读 / 写一个字节的数据,且只能通过一 D0D进行传递;反之,若 BHE 0,A=1,则也可70读/ 写一个字节,但该字节的数据是由奇地址存储体中取出的,故它必须通过高位数据线 D8 D15传递。

如果一个字在存储体中是“非对准”存放,则必须先用一个总线周期存取高8 位(奇地址),然后再用一个总线周期读 / 写低 8 位(偶地址),使存取速度减慢造成时间浪费。

这主要是因为 BHE 及A0的有效时间与操作指令有关。

这就再次提醒我们,在存储器中存储信息时,一定要按8086 存储器结构的特殊要求存放。

在 8088 中,由于数据总线总是8 位的,每个总线周期只能完成一个字节的操作,不存在上述问题,且CPU也没有BHE这个引脚。

3.1.4 复位信号 RESET的作用RESET是外部引入 CPU的信号,高电平有效,脉冲宽度不低于4个时钟周期。

若是上电复位,脉冲宽度就应大于50s。

8086引脚详细说明

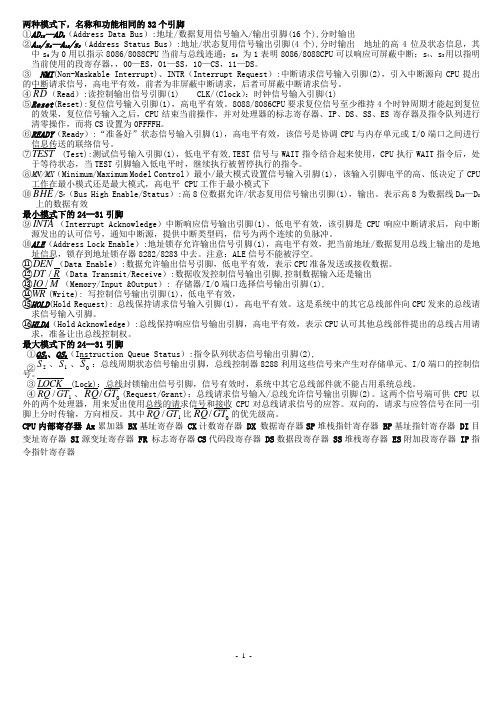

- 1 - 两种模式下,名称和功能相同的32个引脚①AD 15—AD 0(Address Data Bus ):地址/数据复用信号输入/输出引脚(16个),分时输出②A 19/s 6—A 15/s 3(Address Status Bus ):地址/状态复用信号输出引脚(4个),分时输出 地址的高4位及状态信息,其中s 6为0用以指示8086/8088CPU 当前与总线连通;s 5 为1表明8086/8088CPU 可以响应可屏蔽中断;s 4、s 3用以指明当前使用的段寄存器,,00—ES ,01—SS ,10—CS ,11—DS 。

③ NMI (Non-Maskable Interrupt)、INTR (Interrupt Request ):中断请求信号输入引脚(2),引入中断源向CPU 提出的中断请求信号,高电平有效,前者为非屏蔽中断请求,后者可屏蔽中断请求信号。

④RD (Read ):读控制输出信号引脚(1) CLK/(Clock ):时钟信号输入引脚(1)⑤Reset (Reset):复位信号输入引脚(1),高电平有效。

8088/8086CPU 要求复位信号至少维持4个时钟周期才能起到复位的效果,复位信号输入之后,CPU 结束当前操作,并对处理器的标志寄存器、IP 、DS 、SS 、ES 寄存器及指令队列进行清零操作,而将CS 设置为0FFFFH 。

⑥READY (Ready ):“准备好”状态信号输入引脚(1),高电平有效,该信号是协调CPU 与内存单元或I/O 端口之间进行信息传送的联络信号。

⑦TEST (Test):测试信号输入引脚(1),低电平有效,TEST 信号与WAIT 指令结合起来使用,CPU 执行WAIT 指令后,处于等待状态,当TEST 引脚输入低电平时,继续执行被暂停执行的指令。

⑧MN/MX (Minimum/Maximum Model Control )最小/最大模式设置信号输入引脚(1),该输入引脚电平的高、低决定了CPU 工作在最小模式还是最大模式,高电平 CPU 工作于最小模式下 ⑩BHE /S 7(Bus High Enable/Status ):高8位数据允许/状态复用信号输出引脚(1),输出。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

存储器分段示意图 (堆栈段和附加段重叠) 堆栈段和附加段重叠)

3.8086存储器的逻辑地址与物理地址

8086 CPU中的每个 中的每个 存储元在存储体中 的位置都可以使用 实际地址和逻辑地 址来表示。 址来表示。 CPU 访 问 存 储 器 时 , 要 形 成 20 位 的 物 理 地址,即先找到某 段,再找到该段内 的偏移量。换句话 说 , CPU 是 以 物 理 地址访问存储器的, 如图所示。 如图所示。

二、8086/8088的I/O组织 / 的 组织

8086系统与外部设备的输入/输出是通过接口 完成的。 1)单独编址 系统要为I/O芯片的每个端口分配一个地址,各 个端口号不能重复,是单独编址的。 2 2)寻址范围 8086CPU设计了65535个8位的I/O端口,即寻址 范围是0~64K。两个编号相邻的8位端口可以组合 成一个16位端口。 3)访问指令 执 行 IN, OUT 指 令 , RD# 信 号 或 WR# 信 号 与 M/IO#信号同时为低电平。

00001H 00003H 00005H 512k*8 位 奇地址存储体 512k*8 位 偶地址存储体

8 7

0

00000H 00002H 00004H

FFFFFH

FFFFEH

存储器的字节交叉编址方式

数据总线低8位 数据总线低 位AD7-AD0

存

数据总线高8位 数据总线高 位AD15-AD8

储 体 与 总 线 的 连 接

15

00001H 00003H 00005H 512k*8 位 奇地址存储体

8 7

0

00000H 00002H 00004H 512k*8 位 偶地址存储体

FFFFFH

FFFFEH

存储器的字节交叉编址方式

数据总线低8位 数据总线低 位AD7-AD0

存

数据总线高8位 数据总线高 位AD15-AD8

2.8086的引脚特性 2.8086的引脚特性

8086微处理器引 8086微处理器引 脚,在逻辑上可分 为3类:地址总线信 数据总线信号、 号、数据总线信号、 控制总线信号。 控制总线信号。还 有一些专用信号: 有一些专用信号: 电源、 时钟。 电源、地、时钟。 8086采用引脚分 8086采用引脚分 时复用技术, 时复用技术,一条 引脚不同时间代表 不同信号, 不同信号,解决引 脚不够问题。 脚不够问题。

3.3 存储器和I/O组织 存储器和I/O组织

1.8086的存储体结构 . 的存储体结构 2.8086存储器的分段结构 . 存储器的分段结构 3.8086存储器的逻辑地址与物理 . 存储器的逻辑地址与物理 4.8086存储器 位物理地址的形成 存储器20位物理地址的形成 . 存储器

一.存储器的组织 1.存储空间与存储器结构 存储空间与存储器结构 15

8086/8088系统总线的构成 8086/8088系统总线的构成

8086系统的硬件组成根据工作在最大 最小模式而 系统的硬件组成根据工作在最大/最小模式而 系统的硬件组成根据工作在最大 有所不同。 有所不同。 1、最小模式系统总线的构成 、 最小模式的特点:在最小模式下, 最小模式的特点:在最小模式下,所有信号都是 直接或通过地址锁存器8282和数据收发器 由8086直接或通过地址锁存器 直接或通过地址锁存器 和数据收发器 8286给出。 给出。 给出 典型配置:3片地址锁存器 典型配置: 片地址锁存器8282,2片数据收发器 , 片数据收发器 片地址锁存器 8286,1片时钟发生器 片时钟发生器8284。 , 片时钟发生器 。

D7-D0 奇地址存储体 SEL BHE A19-A1

D7-D0 偶地址存储体 SEL A19-A1

A0

A19-A1

2.8086存储器的分段结构

8086 CPU中有四个段 中有四个段 寄 存 器 : CS , DS , SS和 ES, 这四个段寄 和 , 存 器 存 放 了 CPU 当 前 可以寻址的四个段的 基值,也即可以从这 四个段寄存器规定的 逻辑段中存取指令代 码和数据。一旦这四 个段寄存器的内容被 设 定 , 就 规 定 了 CPU 当前可寻址的段,如 图所示。 图所示。

(In):准备好信号,高电平有效。 ﹡READY (In):准备好信号,高电平有效。处理器 与存储器及O接口速度同步的控制信号 In): 测试信号,低电平有效。 ﹡TEST (In): 测试信号,低电平有效。处理器执行 WAIT指令的控制信号 指令的控制信号。 WAIT指令的控制信号。 (In):最大 最小工作模式选择信号。 最大/ ﹡MN/MX (In):最大/最小工作模式选择信号。硬件设 计者用来决定8086工作模式, 8086工作模式 8086为最小模 计者用来决定8086工作模式,MN/MX =1 8086为最小模 8086为最大模式 为最大模式。 式, MN/MX =0 8086为最大模式。 In): 处理器的电源引脚, +5V电源 电源。 ﹡Vcc (In): 处理器的电源引脚,接 +5V电源。 处理器的地线引脚,接系统地线。 ﹡GND :处理器的地线引脚,接系统地线。

(2)最小模式下的有关控制信号 )

INTA(中断响应信号, 输出脚, 在最小模式下表示 ( 中断响应信号,输出脚,在最小模式下表示CPU响 响 应了外设的INTR请求,在中断响应周期,用来作为读选通 请求, 应了外设的 请求 在中断响应周期, 信号,读入中断向量) 信号,读入中断向量) M/IO (在最小模式下,用来区分 在最小模式下,用来区分CPU进行存储器访问还是 进行存储器访问还是 输入/输出访问 输出访问) 输入 输出访问)。 WR(最小模式下为写信号,输出引脚,) 最小模式下为写信号,输出引脚, 最小模式下为写信号

逻辑地址与物理地址的关系

4.8086存储器20位物理地址的形成

在存储段划分时,段内地址是连续的,段与 在存储段划分时, 段内地址是连续的, 段之间是相互独立的。 段之间是相互独立的 。 每个段的起始地址称 段的首地址,段首地址必须是能被16整除的 段的首地址,段首地址必须是能被 整除的 位的段首地址的低四位应当是0000。 数,即20位的段首地址的低四位应当是 位的段首地址的低四位应当是 。 由于段起始地址的低四位为0, 所以将20位 由于段起始地址的低四位为 , 所以将 位 地址的高16位称做段基值, 位称做段基值 地址的高 位称做段基值,存放在段寄存器 段寄存器共四个: 、 、 、 。 中。段寄存器共四个:CS、DS、ES、SS。

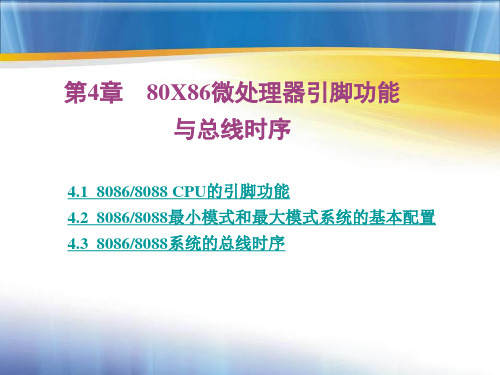

2.2 8086/8088CPU引脚及其功能 8086/8088CPU CPU引脚及其功能

1.8086系统工作模式 8086系统工作模式 8086设计了两种工作模式 设计了两种工作模式——最小模式和最大模式。 最小模式和最大模式。 8086设计了两种工作模式 最小模式和最大模式 8086处于最小模式就是系统中的CPU只有8086单独一个 处于最小模式就是系统中的CPU只有8086 8086处于最小模式就是系统中的CPU只有8086单独一个 处理器,所有总线控制信息都直接由8086产生 总线控制信息都直接由8086产生。 处理器,所有总线控制信息都直接由8086产生。 在最大模式系统中有多个微处理器,其中一个主处 在最大模式系统中有多个微处理器, 理器8086 其它处理器称为协处理器或辅助处理器。 8086, 理器8086,其它处理器称为协处理器或辅助处理器。 8086匹配有 8087( 专用于数值运算的处理器) 匹配有8087 与 8086 匹配有 8087( 专用于数值运算的处理器 ) 和 8089(专用于输入/输出处理的处理器) 8089(专用于输入/输出处理的处理器)。

8088引脚信号 引脚信号

与8086CPU 的对比: 的对比:

1、外部 、 有8条数 条数 据线引脚 2、存储 、 器/IO设备 设备 选择引脚 为IO/M 。

(1)8086基本引脚信号 8086基本引脚信号 I/O,三态):地址 数据复用引脚。 三态):地址/ ﹡AD15~AD0(I/O,三态):地址/数据复用引脚。 A16/S3(O,三态):地址 三态):地址/ ﹡A19/S6 ~ A16/S3(O,三态):地址/状态复用 引脚。 引脚。 ﹡BHE /S7 (O,三态):数据线高8位允许/状态复 O,三态) 数据线高8位允许/ 三态 用引脚。 用引脚。 NMI(In):非屏蔽中断请求线,上升边触发。 ):非屏蔽中断请求线 ﹡NMI(In):非屏蔽中断请求线,上升边触发。 可屏蔽中断请求线,高电平有效。 ﹡INTR (In) :可屏蔽中断请求线,高电平有效。 (O,三态 三态) 读选通信号,低电平有效。 ﹡RD (O,三态) :读选通信号,低电平有效。 In) 时钟信号,处理器基本定时脉冲。 ﹡CLK (In) : 时钟信号,处理器基本定时脉冲。 In) :复位信号,高电平有效。 ﹡RESET (In) :复位信号,高电平有效。 复位信号

5.堆栈段的使用 堆栈段的使用

所谓堆栈是在存储器中开辟一个区域,用来存 放需要暂时保存的数据,其工作方式是“先进 后出”或“后进先出”的方式。 8086系统中的堆栈段是由段定义语句在存储 器中定义的一个段,堆栈段容量小于等于64K 字节。段基址由堆栈寄存器SS指定,栈顶由 堆栈指针SP指定,堆栈地址由高向低增长, 栈底设在存储器的高地址区。

储 体 与 总 线 的 连 接

D7-D0 奇地址存储体 SEL BHE A19-A1

D7-D0 偶地址存储体 SEL A19-A1

A0

A19-A1

BHE、A0的控制作用 、 的控制作用

BHE 0 0 1 0 1 A0 0 1 0 1 0 操作 从偶地址读写一个字。 只访问奇地址存储体,读/ 写一个字节。 只访问偶地址存储体,读/ 写一个字节。 若从奇地址读/写一个字, 需要分两个总线周期实现, 先读/写奇地址字节,然后 再读/写偶地址字节。 所用数据引脚 AD15-AD0 AD15-AD8 AD7-AD0 AD15-AD8 AD7-AD0