组合逻辑电路的数据流描述

EDA判断题题库(56题)_附答案

(√ ) 54. Verilog 语言的行为描述语句,如条件语句、赋值语句和循环语句类似于软件

高级语言,便于学习和使用。( √ ) 55. 行为描述就是对设计实体的数学模型的描述,其抽象程度远高于结构描述。

2/3

48. 目前常用的硬件描述语言为:Verilog HDL 和 VHDL。( √ ) 49. Verilog HDL 数据类型是用来表示数字电路中的物理连线、数据存储和传输

单元等物理量的。( √ ) 50. 混合仿真器就是能同时支持 Verilog 和 VHDL 的仿真器。( √ ) 51. Verilog 程序的基本设计单元是“模块”( module)。( √ ) 52. 布局布线为将综合生成的电路逻辑网表映射到具体的目标器件中实现,并产

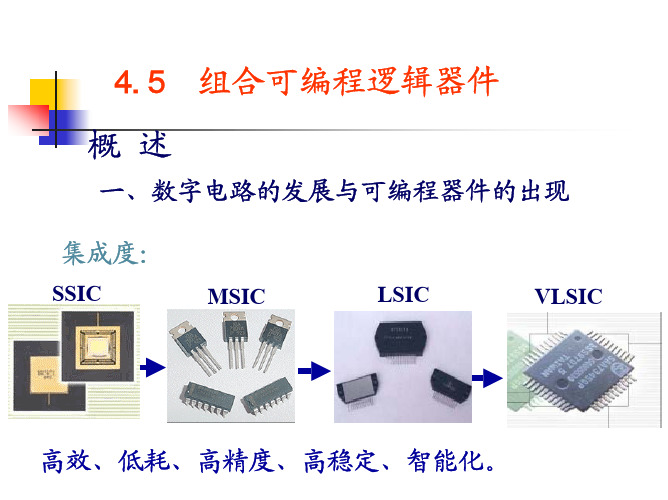

种。( √ ) 13. PLD 是 Programmable Logic Device,可编程逻辑器件的缩写。( √ ) 14. Verilog 语言即适合可综合的电路设计,也可胜任电路与系统的仿真。( √ ) 15. Verilog HDL 支持循环语句。( √ ) 16. 硬件综合器和软件程序编译器没有本质区别。( × ) 17. 集成度是 PLD 器件的一项重要指标。( √ ) 18. PLD 器件的设计往往采用层次化的设计方法,分模块,分层次地进行设计描

1/3

25. CPLD 是 Complex Programmable Logic Device,复杂可编程逻辑器件的缩写。 (√ )

26. PLD 是一种全定制器件。( × ) 27. 综合指的是将较高级抽象层次的设计描述自动转化为较低层次描述的过程。

(√ ) 28. Verilog HDL 和 VHDL 目前还都不是 IEEE 标准。( × ) 29. 把适配后生成的编程文件装入到 PLD 器件中的过程称为下载。( √ ) 30. Verilog HDL 中 assign 为持续赋值语句。( √ ) 31. Verilog HDL 语法要素与软件编程语言(如 C 语言)是完全相同的。( × ) 32. 数字设计流程中采用原理图方式适合描述电路的连接关系和接口关系。

数字逻辑知到章节答案智慧树2023年山东科技大学

数字逻辑知到章节测试答案智慧树2023年最新山东科技大学绪论单元测试1.系统一般可分为模拟系统、数字系统和模拟数字混合系统。

()参考答案:对第一章测试1.假定下列字符码中有奇偶校验位,但没有数据错误,采用偶校验的字符码是:()参考答案:110010012.某数在计算机中用 8421BCD 码表示为 0111 1000 1001 ,其真值为:()参考答案:7893.常用的BCD码有:()参考答案:8421码4.与余 3码(10001000 )等值的十进制数是:()参考答案:555.8421BCD码是否具有奇偶特性?()参考答案:是第二章测试1.试求此函数的最简或与式为()。

参考答案:2.函数的最简与或式为()。

参考答案:3.函数和相等()。

参考答案:对4.函数的反函数为。

()参考答案:错5.函数的对偶式为。

()参考答案:错第三章测试1.二极管具有单向导电性。

()参考答案:对2.三极管的三个工作区域分别是:饱和区、截止区、放大区。

()参考答案:对3.OC门工作时要外加上拉电阻才可以正常工作。

()参考答案:对4.TTL与非门可以实现“线与”功能。

()参考答案:错5.TTL与非门的悬空端可看作: ()参考答案:高电平6.下列哪种门电路可以将输出端直接并联使用:()参考答案:OC门7.三态门的三个状态是: ()参考答案:低电平;高电平;高阻态第四章测试1.根据如下电路,设输入为A,B,C,输出为F,利用组合逻辑电路的分析方法可知,此电路只有当输入信号一致时,输出F=1,;输入不一致时,输出F=0,该电路为不一致检测电路。

()参考答案:对2.在输入不提供反变量的情况下,用与非门实现函数,利用组合逻辑电路的设计方法,如下电路设计可以实现该逻辑函数功能。

()参考答案:对3.利用险象判断的方法,如下电路中可能存在险象。

()参考答案:对4.逻辑函数可能存在竞争-冒险。

()参考答案:对5.利用译码器的使能端,将两片3-8译码器可扩展为一片4-16译码器,可用于设计四位二进制的偶校验发生器,经电路分析,如下四位二进制的偶校验发生器电路存在设计错误。

组合逻辑电路的数据流描述

用VerilogHDL描述组合逻辑电路有三种不同抽象级 别:组合逻辑电路的门级描述、组合逻辑电路的数 据流描述、组合逻辑电路的行为级描述。 VerilogHDL描述的电路就是该电路的VerilogHDL模 型。

•门级描述:

一般使用Primitive(内部元件)、自定义的下层模块对电 路描述。主要用于层次化设计中。

endmodule

例2 用Verilog的门级元件进行

B

L

描述由三态门构成的2选1数据选

A

择器 。

SEL

//Gate-level description of a 2-to-1-line multiplexer module _2to1muxtri (A,B,SEL,L);

input A,B,SEL output L; tri L; bufif1 (L,B,SEL); bufif0 (L,A,SEL); endmodule

•数据流描述方式: 一般使用assign语句描述,主要用于对组合逻辑电路建模。 •行为描述方式:

一般使用下述语句描述,可以对组合、时序逻辑电路建模。 1)initial 语句 2)always 语句

4.6.1 组合逻辑电路的门级建模

门级建模:将逻辑电路图用HDL规定的文本语言表示出来。

三态门

元件符号 功能说明

2选1数据选择器的连续赋值描述是: wire A,B,SEL,L; //声明4个连线型变量 assign L=(A & ~SEL)|(B & SEL); //连续赋值

注意,在assign语句中,左边变量的数据类型必须是wire型。

E

1

A0

1

A1

Verilog描述方法与层次

Verilog描述⽅法与层次Verilog描述⽅法与层次Verilog语⾔有多种描述⽅法,这些⽅法也可以在多个层次上来描述硬件。

描述⽅式在上⼀篇当中已经引⼊过数据流描述、⾏为描述、结构化描述这三种描述的⽅式的概念,本篇将继续深⼊说明这三种描述⽅式。

数据流描述1.数据流:组合逻辑电路的信号传输其实就类似于数据的流动,数据从中经过但是不会存储,⼀旦输⼊改变,输出随之在⼀定的延时(Tpd)之后发⽣改变。

连续赋值语句连续赋值语句具有以下的特点:1.连续驱动:输⼊的改变将导致该语句重新计算2.只有线⽹型变量可以⽤assign赋值:仿真器中不会储存assign赋值的变量,寄存器有存储要求显然不能⽤assign赋值,只有线⽹型可以。

另外,assign语句允许多驱动即⼀个变量可以多个输⼊(实际上就是实现线与和线或),建议复习⼀下数字电路中线与和线或的实现。

3.适⽤于组合逻辑建模:若要模拟延迟可以通过 # 来加延迟4.并⾏性:assign语句同其他语句块是并发的。

以⼀个异或门为例:module FullAdder(input x,input y,input c_in,output c_out,output sum);assign sum = x^y^c_in;assign c_out = (x&y) || (x&c_in) || (y&c_in)//以上两条语句都是并发执⾏且连续赋值的。

endmodule延时任何⼀个元器件都必然存在延时,⽽在数据流描述⽅式中,我们也可以选择对其进⾏建模。

延时具体也可以分为:上升延时即输出变为1时的延时,下降延时即输出变为0的延时,关闭延时即输出变为⾼阻态的延时,以及输出变为X 即中间态的延时(通常取前⾯三种中最⼩的)。

关于延时的建模也有多种⽅法,以下是⼀个例⼦:assign #1 out = in1^in2;//`timescale 1ns/1ns输⼊到输出须1nsassign #(1,2) out1 = in1^in2;//上升延时1ns,下降延时2ns,变x和关闭取最⼩为1nsassign #(1,2,3) out2 = in1^in2;//上升1ns,下降2ns,关闭3ns,变X1nsassign #(4:5:6,3:4:5)out3 = in1^in2;//(min:typ:max)描述的时延时最⼩典型最⼤三种情况,同样第⼀个是上升,第⼆个是下降注意:连续赋值中的延时是惯性延时,即出现⼩于延时的信号(⽑刺信号)会被过虑掉。

EDA考试必考知识点

考试题型:简答题,程序语句解释,程序填空,编程EDA就是以计算机为工作平台,以EDA软件工具为开发环境,以PLD器件或者ASIC专用集成电路为目标器件设计实现电路系统的一种技术。

现代EDA技术的特征:1,、采用硬件描述语言进行设计2、逻辑综合与优化3、开放性和标准化4.、更完备的库。

数字系统设计技术:1、Topdown即自顶向下的设计。

这种设计首先从系统设计下手,在顶层进行功能方框图的划分和结构设计。

须经过“设计—验证—修改设计再验证”的过程,不断反复,直到结果能够实现所要求的功能,并在速度、功耗、价格和可靠性方面实现较为合理的平衡。

2、Bottomup设计,即自底向上的设计,由设计者调用设计库中的元件(如各种门电路、加法器、计数器等) ,设计组合出满足自己需要的系统。

不仅效率低、成本高而且易出错。

IP:原来的含义是指知识产权、著作权,在IC设计领域指实现某种功能的设计。

IP核(IP模块):指功能完整,性能指标可靠,已验证的、可重用的电路功能模块。

IP复用:软IP--用VHDL等硬件描述语言描述的功能块,但是并不涉及用什么具体电路元件实现这些功能。

固IP完成了综合的功能块。

硬IP供设计的最终阶段产品:掩膜。

基于IP复用的开发帮助设计者节省时间,缩短开发周期,避免重复劳动。

可编程逻辑阵列PLA,可编程与阵列或阵列,输出电路固定。

可编程阵列逻辑PAL,可编程与阵列,或阵列输出电路固定。

FPGA是一种半定制的器件,器件内已做好各种逻辑资源,用户只需对器件内的资源编程连接就可实现所需要的功能。

ASIC指用全定制的方法来实现设计的方式,它在最底层,即物理版图级实现设计,因此也称为掩膜ASCI。

CPLD即复杂可编程逻辑器件,是从EPLD改进而来的。

逻辑综合:RTL级描述转换到逻辑门级(包括触发器)。

版图综合或结构综合:从逻辑门表示转换到版图表示,或转换到PLD器件的配置网表表示。

综合器是能够自动实现上述转换的软件工具,是能将原理图或HDL语言描述的电路功能转化为具体电路结构网表的工具。

第3章 逻辑电路功能描述方法

full_add

⑶采用程序建模:顶层模块编程设计

将顶层模块用硬件描述语言进行设计,在这里需要调 用底层半加器模块来实现。 例3.7 一位全加器顶层模块程序 module full_add(ain,bin,cin,sum,cout); input ain,bin,cin; output sum,cout; wire d,e,f; //用于内部连接的节点信号 half_add u1(ain,bin,e,d); //半加器模块调用,采用位置关联方式, //或名称对应方式 //hall_add u1(.a(ain),. b(bin), .so(e),.co(d)) half_add u2(e,cin,sum,f); or u3(cout,d,f); //或门调用 endmodule

//或仅使用下面一条语句替代上面两条

//assign {cout,sum}=a+b+cin

endmodule

【例3.6】行为描述的1位全加器

module full_add3(a,b,cin,sum,cout); input a,b,cin; output reg sum,cout;//必须定义为寄存器型变量 always @* //或写为always @(a ,b , cin) begin {cout,sum}=a+b+cin; end endmodule

一位半全加器U2

1、采用层次化方式设计1位全加器 ⑴底层一位半加器模块建模

采用数据流描述设计建模,并通过编译、仿真得到正 确的半加器电路,保存文件,用于顶层文件调用。

module half_add(a,b,so,co); input a,b; output so,co; assign co=a&b; assign so=a^b; endmodule

verilog的三种描述方式

verilog的三种描述方式(最新版)目录1.引言2.Verilog 描述方式概述1.结构描述2.数据流描述3.行为描述4.混合描述3.结构描述1.门级结构描述2.模块级结构描述4.数据流描述1.逻辑关系2.持续赋值语句5.行为描述1.寄存器传输级描述2.状态机描述6.混合描述7.结论正文一、引言Verilog 是一种硬件描述语言,广泛应用于数字电路和模拟混合信号电路的设计验证。

在 Verilog 中,有多种描述方式可以实现逻辑功能,包括结构描述、数据流描述、行为描述和混合描述。

本文将对这些描述方式进行详细介绍。

二、Verilog 描述方式概述1.结构描述:通过调用逻辑原件,描述它们之间的连接来建立逻辑电路的 Verilog 模型。

这里的逻辑元件包括内置逻辑门、自主研发的已有模块、商业 IP 模块。

结构描述分为门级结构描述和模块级结构描述。

2.数据流描述:根据信号之间的逻辑关系,采用持续赋值语句描述逻辑电路的行为。

数据流描述关注信号的传输和处理过程,适用于组合逻辑电路的设计。

3.行为描述:通过描述电路的输入输出行为,以及电路内部状态的变化,来实现逻辑功能的描述。

行为描述主要包括寄存器传输级描述和状态机描述。

4.混合描述:结合结构描述、数据流描述和行为描述,实现对逻辑功能的全面描述。

混合描述可以充分利用 Verilog 的各种特性,提高描述的准确性和效率。

三、结构描述1.门级结构描述:通过实例化内置逻辑门或使用自定义模块,构建逻辑电路的结构。

例如,可以使用与门、或门、非门等逻辑门实现组合逻辑电路。

2.模块级结构描述:将具有一定功能的模块进行组合,形成复杂的逻辑电路。

模块可以是自主研发的已有模块,也可以是商业 IP 模块。

四、数据流描述1.逻辑关系:根据信号之间的逻辑关系,使用持续赋值语句进行描述。

例如,对于一个与非门,可以使用`assign #5 neg(a);`语句描述其输出信号与输入信号 a 的逻辑关系。

组合可编程逻辑器件

与阵列固定,或阵 列可编程(PROM)

B A

与阵列、或阵列 均可编程(PLA)

B A 或阵列 可编程

与阵列可编程,或 阵列固定(PAL和 GAL等)

B A

或阵列 固定

或阵列 可编程

与阵列 固定

L1 L0

与阵列 可编程

L1 L

与阵列 可编程

L1 L0

4.5.1

例1

组合逻辑电路的PLD实现

An Bn Cn

4、具有完善先进的开发工具: 提供语言、图形等设计方法,十分灵活 通过仿真工具来验证设计的正确性 5、系统处理速度高:用PLD与或两级结构实现任何逻辑功能, 所需的逻辑级数少。这不仅简化了系统设计,而且减少了级 间延迟,提高了系统的处理速度。 6、系统具有加密功能:某些PLD器件,如GAL或高密度可 编程逻辑器件本身具有加密功能。设计者在设计时选中加密 项,可编程逻辑器件就被加密,器件的逻辑功能无法被读出, 有效地防止逻辑系统被抄袭。 7、使用方便:可以反复地擦除、编程,方便设计的修改和 升级

低电平 L 高电平

A、B、C有一个输入低电 平0V A、B、C三个都输入高电 平+5V

L=A•B•C

A

B

C

D

V CC L

VCC

A

B

C

D

L

A、B、C 中有一个为0 输出为0; A、B、C 中都为1 输出为1。 L=ABC L=AC

T1

T2

X T3

T4

X

连接 连接 连接 断开 连接 断开 连接 断开

(4) 浮栅MOS管开关 叠栅注入MOS(SIMOS)管 浮栅MOS管 浮栅隧道氧化层MOS(Flotox MOS)管 快闪(Flash)叠栅MOS管 用不同的浮栅MOS管连接的PLD,编程信息的擦除方法 也不同。SIMOS管连接的PLD,采用紫外光照射擦除; Flotox MOS管和快闪叠栅MOS管,采用电擦除方法。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

z

0 x

nand

0

输 1 入 x

输入1 0 1 1 1 1 0

x 1 x

z 1 x

2

x z

0 0

x x

1

1

x

x

x

x

x

x

2 z

X- 不确定状态

Z- 高阻态

or真值表

or

0 输 入 2 1 输入1

xor真值表

Z

X 1 输 入

0

0 1

1

1 1

X

X 1

xor 0 1

X Z

输入1

0

0 1 X X

1

1 0 X X

多输入端的异或门 多输出端的缓冲器 控制信号高电平有效的三态缓冲 器 控制信号低电平有效的三态缓冲 器

bufif1

bufif0

notif1

notif0

end

Verilog 基本门级元件

and nand or nor n-input AND gate n-input NAND gate n-input OR gate n-input NOR gate buf n-output buffer

X X X X X

Z X X X X

X

Z

X

X

1

1

X

X

X

X

2

2、多输出门 允许有多个输出,但只有一个输入。

not N1(out1,out2,…,in);buf B1(out1,out2,…,in);

out1 in out2 in outN

…

out 1 out 2 out N

…

not真值表

输入 not 0 1 输 出1 0 x x z x

4.6 用VerilogHDL描述组合逻辑电路

4.6.1 组合逻辑电路的门级建模 4.6.2 组合逻辑电路的数据流建模

4.6.3 组合逻辑电路的行为级建模

4.6 用VerilogHDL描述组合逻辑电路

用VerilogHDL描述组合逻辑电路有三种不同抽象级

别:组合逻辑电路的门级描述、组合逻辑电路的数 据流描述、组合逻辑电路的行为级描述。 VerilogHDL描述的电路就是该电路的VerilogHDL模 型。

notif1真值表

bufif1 数 据 输 入 0 1 x z

Hale Waihona Puke 控制输入 0 1 x 0 0/z z z z z 1 x x 1/z x x

z 0/z

1/z x x

notif1 控制输入 0 1 x z 0 z 1 1/z 1/z 数 1 z 0 0/z 0/z 据 x x 输 x z x x x 入 z z x

•门级描述: 一般使用Primitive(内部元件)、自定义的下层模块对电 路描述。主要用于层次化设计中。 •数据流描述方式: 一般使用assign语句描述,主要用于对组合逻辑电路建模。 •行为描述方式: 一般使用下述语句描述,可以对组合、时序逻辑电路建模。 1)initial 语句

2)always 语句

//Gate-level description of a 2to-4-line decoder 4、设计举例 module _2to4decoder 试用Verilog语言的门级 (A1,A0,E,Y); 元件描述2线-4线译码器. input A,B,E; 说明 output [3:0]Y; 部分 wire A1not,A0not,Enot; 1 E & Y0 not n1 (A1not,A1), n2 (A0not,A0), & Y1 n3 (Enot,E); 1 A0 功能 nand & Y 2 描述 n4 (Y[0],A1not,A0not,Enot), 1 n5 (Y[1],A1not,A0,Enot), A1 & Y3 n6 (Y[2],A1,A0not,Enot), n7 (Y[3],A1,A0,Enot); endmodule

4.6.1 组合逻辑电路的门级建模

门级建模:将逻辑电路图用HDL规定的文本语言表示出来。

三态门

元件符号 and or xor buf 功能说明 多输入端的与门 多输入端的或门

基本门级元件模型 多输出门

元件符号 nand nor xnor not 功能说明

多输入门

多输入端的与非门 多输入端的或非门 多输入端的异或非门 多输出端的反相器 控制信号高电平有效的 三态反相器 控制信号低电平有效的 三态反相器

=1 &

S A B C=AB

//Gate-level hierarchical description of 4-bit adder // Description of half adder module halfadder (S,C,A,B); input A,B; output S,C; //Instantiate primitive gates xor (S,A,B); and (C,A,B); endmodule

例2 用Verilog的门级元件进行 描述由三态门构成的2选1数据 选择器 。

B A

L

SEL

//Gate-level description of a 2-to-1-line multiplexer module _2to1muxtri (A,B,SEL,L); input A,B,SEL output L; tri L; bufif1 (L,B,SEL); bufif0 (L,A,SEL); endmodule

5、分层次的电路设计方法简介 分层次的电路设计:在电路设计中,将两个或多个模块组 合起来描述电路逻辑功能的设计方法。

设计方法:自顶向下和自底向上两种常用的设计方法 4位全加器的层次结构框图

4 位全加器

1 位全加器

1 位全加器

1 位全加器

1 位全加器

半加器

或门

. . . . . .

半加器

或门

A B

buf真值表

输入 buf 0 1 输 出 0 1

x x

z x

3、三态门 有一个输出、一个数据输入和一个输入控制。 如果输入控制信号无效,则三态门的输出为高阻态z。

in ctrl (a) out in ctrl out

(b) 图 4.6.3 三态门元件模型 (a)bufif1 (b)notif1

bufif1真值表

not

bufif0

n-output inverter

tri-state buffer; Io enable

bufif1 tri-state buffer; hi enable

notif0 notif1 tri-state inverter; Io enable tri-state inverter; hi enable

xor

n-input exclusive OR gate

n-input exclusive NOR gate

xnor

1、多输入门 只允许有一个输出,但可以有多个输入。

调用名

and A1(out,in1,in2,in3); and真值表

and

0 输 入 1

nand真值表

X 0 x

x x

0 0

0

输入1 1 0 1 x x