Quartus-II中FPGA管脚的分配策略

Quartus_II常见问题集锦

Quartus II常见问题集锦1、【问题】Pin Planner 的使用问题:在QuartusII 7.2 ,时序仿真都通过,但是,一旦使用Pin Planner设定引脚后,时序仿真就发生变化,与功能仿真结果不一致,不是理想的结果。

使用Pin Planner时要注意些什么问题呢?【解答】如果在没有设定引脚时就进行时序仿真,那么在后仿真就会不准确。

因为当设定引脚以后,需要重新进行布局布线,这和没有设定引脚是不同的,因此,布线的改变自然会影响到时序的改变。

通常的做法是:先做好所有的设定,生成网表文件和延时文件,再加上激励文件进行仿真,这个时候的仿真结果是最接近实际情况的。

通常的pin设定没有特定要求,差分信号是成对的。

所以请不要搞错。

时钟信号尽量使用专用的时钟引脚;普通I/O没有什么限制,做好时序约束就可以了。

2、【问题】怎样配置cyclone FPGA的管脚功能?【解答】FPGA芯片的引脚分为好多类,有通用IO,有时钟网络,有复位网络,这些引脚的具体功能是在布线时由用户选择的。

你可以自由的配置这些引脚的功能,但最好根据芯片的数据手册进行选择,如将时钟配置到专用时钟引脚上,将复位配置到专用复位引脚上,否则会影响最终的布线结果。

3、【问题】分配fpga管脚时该怎么选择,引脚有什么属性需要考虑,quartus2中引脚有几个属性:Reserved,Group,I/O Bank,Vref Group,I/O standard( 3.3-V LVTTL(default) )分别是什么意思,要怎么设置?【解答】首先说IO standard:这个是用于支持对应不同的电平标准。

FPGA IO 口的电压由IO bank上的VCC引入。

一个bank上引入3.3V TTL电平,那么此时整个bank上输出3.3V的TTL电平。

设置这个第一是为了和current strength 一起计算功率。

第二个是用于在IO口上加载正确的上拉/下拉电阻。

FPGA的配置引脚说明

FPGA是基于SRAM编程的,编程信息在系统掉电时会丢失,每次上电时,都需要从器件外部的FLASH或EEPROM中存储的编程数据重现写入内部的SRAM中。

FPGA在线加载需要有CPU的帮助,并且在加载前CPU已经启动并工作。

FPGA的加载模式主要有以下几种:1). PS 模式(P assive Serial Con figuration Mode)即被动串行加载模式。

PS模式适合于逻辑规模小,对加载速度要求不高的FPGA加载场合。

在此模式下,加载所需的配置时钟信号CCLK由FPGA外部时钟源或外部控制信号提供。

另外,PS加载模式需要外部微控制器的支持。

2).AS 模式(Active Serial Con figuration Mode),即主动串行加载模式。

在AS模式下,FPGA主动从外部存储设备中读取逻辑信息来为自己进行配置,此模式的配置时钟信号CCLK由FPGA内部提供。

3).PP 模式(Passive Parallel Configuration Mode,即被动并行加载模式。

此模式适合于逻辑规模较大,对加载速度要求较高的FPGA加载场合。

PP模式下,外部设备通过8bit并行数据线对FPGA进行逻辑加载,QCLK信号由外部提供。

4).BS 模式(Bou ndary Sca n Con figuratio n Mode),即边界扫描加载模式。

也就是我们通常所说的JTAG加载模式。

所有的FPGA芯片都有三个或四个加载模式配置管脚,通过配置MESL[0..3]来选取不同的加载模式。

首先来介绍下PS加载模式,各个厂商FPGA产品的PS加载端口定义存在一些差异,目前主流的三个FPGA厂商Altera, Xilinx,Lattice的PS加载方式进行一一介绍。

Altera公司的FPGA产品PS加载接口如下图所示。

nSTATUS1).C0NFIG_D0NE :加载完成指示输出信号,I/O接口,高有效,实际使用中通过4.7K电阻上拉到VCC,使其默认状态为高电平,表示芯片已加载完毕,当FPGA正在加载时,会将其驱动为低电平。

数字实验箱与QuartusII使用

选择 ,单击左键、右键可 以调整时间轴单位

用鼠标选择一段波形, 单击工具栏可以将选定波形设置为1、0 等

Quartus II 的使用 (4)设计文件的仿真

设置周期波形

单击

,分别将a, b, cin

的时间周期(Period)设置

成20, 40, 80(ms)。

从全加器真值表可以看出,a,b,cin具有二倍 关系,可以选中其中一个输入管脚

拨码开关拨到上方,对应的发光管 点亮,电路送给FPGA高电平

拨码开关

EP2C5 I/O管脚

BM1 95

BM2 96

BM3 BM4 BM5 BM6

97

99 101 102

BM7 103

BM8 104

数字电路实验箱的使用 (3)彩灯电路与EP2C5管脚连接对照表

行 红(R) 黄(Y) 绿(G)

EP2C5的I/O管脚 列 EP2C5的I/O管脚

如:在Name栏输入xor 点击OK

S = A XOR B XOR Cin Co = A XOR B Cin + A B

Quartus II 的使用 (2) 建立图形文件 …

双击空白处后分别输入

xor

异或门

and2

与门

or2

或门

input

输入管脚

output

输出管脚

注:输入与门/或门时要注明 有几个输入管脚

S

0

0

0

0

0

0

0

1

0

1

0

1

0

0

1

0

1

1

1

0

1

0

0

0

1

Quartus II自动添加管脚分配的方法

二、管脚分配方法FPGA 的管脚分配,除了在QII软件中,选择“Assignments ->Pin”标签(或者点击按钮),打开Pin Planner,分配管脚外,还有以下2种方法。

方法一:Import Assignments步骤1:使用记事本或类似软件新建一个txt文件(或csv文件),按如下格式编写管脚分配内容(不同的开发版,其内容也不同,本文以我使用的DIY_DE2开发板为范例)。

【这种方式格式最为简单】注意:To和Location两个关键字中间有一个半角逗号。

图1 pin.txt步骤2:在QII软件中,选择“Assignments -> Import Assignments”。

如图所示,导入xxx.txt或者xxx.csv文件即可图2 导入pin.txt步骤3:在QII软件中,选择“Assignments -> Pin”标签(或者点击按钮),打开Pin Planner,验证管脚是否分配正确。

图3 验证管脚是否分配正确方法二:导入source xxx.tcl文件步骤1:在QII软件中,使用“Assignments -> Remove Assignments”标签,移除管脚分配内容,以确保此次操作,分配的管脚没有因为覆盖而出现错误的情况。

图4 Remove Assignments注:在未执行任何管脚分配操作新工程中,可跳过步骤1。

步骤2:使用记事本或类似软件新建一个tcl文件,按如下格式编写管脚分配内容(不同的开发版,其内容也不同,本文以我使用的DIY_DE2开发板为范例)。

注意关键字set_location_assignment和-to的用法。

图5 pin.tcl步骤3:执行pin.tcl方法1:在QII软件中,使用“View -> Utility Windows -> Tcl Console”标签,打开Quartus II Tcl Console。

执行语句:图6 source pin.tcl方法2:在QII软件中,使用“Tools -> Tcl Scripts …”标签,打开Tcl Scripts。

QuatusII简明使用指南

EDA应用实习软件平台QuatusII简明使用指南邹海英编黑龙江工程学院电子工程系2010年12月·哈尔滨一、Quartus Ⅱ简介Quartus II是美国Altera公司于2000年推出的FPGA/CPLD开发设计的集成软件环境,能够直接满足特定设8BA1需要,为可编程芯片系统(SOPC) 提供全面的设计环境,是Altera 前一代FPGA/CPLD开发软件MAX+PLUS II的更新换代产品。

至今已相继推出了Quartus II 1.0,5.0,6.0,7.2等很多版本,2009年11月又推出最新的Quartus II软件9.1,与以前的软件版本相比,其新特性和增强功能将编译时间缩短了20%。

Quartus II 软件集成了FPGA 和CPLD 开发流程中所用到的所有工具和第三方软件接口。

我们可以使用Quartus II 软件完成FPGA 和CPLD 设计的所有阶段,也可以在设计的不同阶段使用自己熟悉的EDA 工具,如在输入综合阶段利用第三方的输入与综合工具,如Leonardo Spectrum、FPGA Compiler II、Synplify、Synplify Pro等,在仿真阶段利用第三方的仿真工具,如ModelSim、VCS MX等。

Quartus II 软件同时支持自上而下或自下而上的渐进式设计流程以及基于模块的设计方法。

使用Quartus II 模块编辑器、文本编辑器、Mega Wizard 插件管理器和EDA设计输入工具还可以设计Altera宏功能模块、参数化模块库(LPM) 功能和知识产权(IP)。

Quartus II 软件还提供全面的命令行界面解决方案。

它允许使用命令行可执行文件和选项完成设计流程的每个阶段。

另外,Quartus II还可以与MATLAB和DSP Builder相结合,进行FPGA的DSP系统开发。

二、Quartus II软件开发流程Quartus II软件的开发流程如图2-1所示。

FPGA引脚分配方法

第二种:建立TCL文件进行管脚分配。

这种方法比较灵活,是比较常用的。

这种方法具有分配灵活,方便快捷,可重用性等多方面优点。

方法如下:选择Projects菜单项,并选择Generate tcl file for project选项,系统会为你自动生成相应文件,然后你只要向其中添加你的分配内容就可以了。

还有一种方法就是直接用new ,新建一个TCL文件即可,具体不再细讲。

下面是我分配的内容一部分,可供大家参考。

set_global_assignment -name FAMILY Cycloneset_global_assignment -name DEVICE EP1C3T144C8set_global_assignment -name ORIGINAL_QUARTUS_VERSION 8.0 set_global_assignment -name PROJECT_CREATION_TIME_DATE "19:14:58 JANUARY 06, 2009"set_global_assignment -name LAST_QUARTUS_VERSION 8.0set_global_assignment -nameUSE_GENERATED_PHYSICAL_CONSTRAINTS OFF -section_ideda_palaceset_global_assignment -name DEVICE_FILTER_PACKAGE "ANY QFP" set_global_assignment -name LL_ROOT_REGION ON -section_id "Root Region"set_global_assignment -name LL_MEMBER_STATE LOCKED-section_id "Root Region"set_global_assignment -name DEVICE_FILTER_PIN_COUNT 144 set_global_assignment -name DEVICE_FILTER_SPEED_GRADE 8 set_global_assignment -name FITTER_EFFORT "STANDARD FIT" set_global_assignment -name BDF_FILE topDesign.bdfset_global_assignment -name QIP_FILE nios.qipset_global_assignment -name QIP_FILE altpll0.qipset_global_assignment -name USE_CONFIGURATION_DEVICE ON set_global_assignment -name STRATIX_DEVICE_IO_STANDARD "3.3-V LVTTL"set_global_assignment -name PARTITION_NETLIST_TYPE SOURCE -section_id Topset_global_assignment -name PARTITION_COLOR 14622752-section_id Topset_location_assignment PIN_72 -to addr[7]set_location_assignment PIN_69 -to addr[6]set_location_assignment PIN_70 -to addr[5]set_location_assignment PIN_67 -to addr[4]set_location_assignment PIN_68 -to addr[3]set_location_assignment PIN_42 -to addr[2]set_location_assignment PIN_39 -to addr[1]set_location_assignment PIN_40 -to addr[0]set_location_assignment PIN_48 -to data[15]set_location_assignment PIN_47 -to data[14]set_location_assignment PIN_50 -to data[13]set_location_assignment PIN_49 -to data[12]set_location_assignment PIN_56 -to data[11]set_location_assignment PIN_55 -to data[10]set_location_assignment PIN_58 -to data[9]set_location_assignment PIN_57 -to data[8]set_location_assignment PIN_61 -to data[7]set_location_assignment PIN_62 -to data[6]set_location_assignment PIN_59 -to data[5]set_location_assignment PIN_60 -to data[4]set_location_assignment PIN_53 -to data[3]set_location_assignment PIN_54 -to data[2]set_location_assignment PIN_51 -to data[1]set_location_assignment PIN_52 -to data[0]set_location_assignment PIN_16 -to clkset_location_assignment PIN_38 -to csset_location_assignment PIN_141 -to led[3]set_location_assignment PIN_142 -to led[2]set_location_assignment PIN_143 -to led[1]set_location_assignment PIN_144 -to led[0]set_location_assignment PIN_33 -to reset_nset_location_assignment PIN_41 -to rdset_location_assignment PIN_71 -to wrset_location_assignment PIN_105 -to mosiset_location_assignment PIN_107 -to sclkset_location_assignment PIN_106 -to ssset_location_assignment PIN_73 -to motor[0]set_location_assignment PIN_74 -to motor[1]set_location_assignment PIN_75 -to motor[2]set_location_assignment PIN_76 -to motor[3]set_instance_assignment -name PARTITION_HIERARCHY root_partition -to | -section_id Top# Commit assignmentsexport_assignmentsFPGA 点滴(2008-09-30 09:44:45)转载标签:杂谈以此记录心得以及重要的知识点。

QuartusII软件概述

QuartusII软件概述QuartusII软件是Altera公司最新版本的EDA开发软件,支持APEX系列、Cyclone系列、Stratix系列和Excalibur系列等新型系列器件的开发。

含有工作组计算、集成逻辑分析仪、EDA工具集成、多过程支持、增强重编译和IP集成等特性。

支持百万门级的设计,支持高速I/O设计,具有更强的设计能力和更快的编译速度。

QuartusII开发软件为可编程片上系统(SOPC)设计提供了一个完整的设计环境。

无论是使用个人电脑、NUIX或Linux 工作站,QuartusII都提供了方便设计、快速编译处理以及编程功能。

QuartusII输入的设计过程可分为创建工程、输入文件、项目编译、项目校验和编程下载等几个步骤。

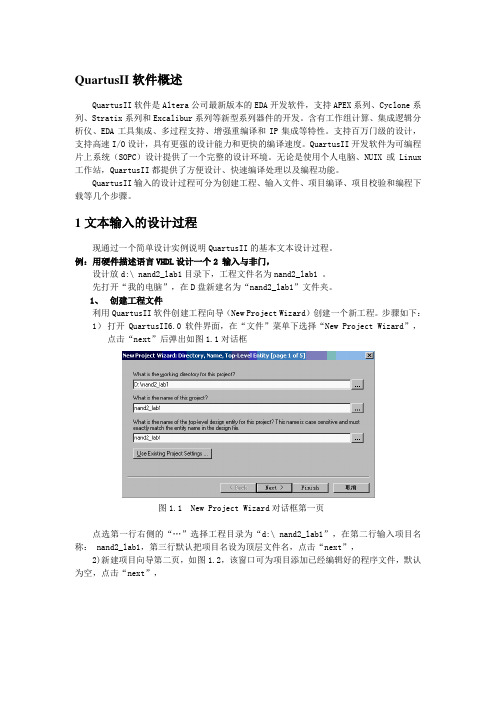

1文本输入的设计过程现通过一个简单设计实例说明QuartusII的基本文本设计过程。

例:用硬件描述语言VHDL设计一个2 输入与非门,设计放d:\ nand2_lab1目录下,工程文件名为nand2_lab1 。

先打开“我的电脑”,在D盘新建名为“nand2_lab1”文件夹。

1、创建工程文件利用QuartusII软件创建工程向导(New Project Wizard)创建一个新工程。

步骤如下:1)打开QuartusII6.0软件界面,在“文件”菜单下选择“New Project Wizard”,点击“next”后弹出如图1.1对话框图1.1 New Project Wizard对话框第一页点选第一行右侧的“…”选择工程目录为“d:\ nand2_lab1”,在第二行输入项目名称: nand2_lab1,第三行默认把项目名设为顶层文件名,点击“next”,2)新建项目向导第二页,如图1.2,该窗口可为项目添加已经编辑好的程序文件,默认为空,点击“next”,图1.2 New Project Wizard对话框第二页3)新建项目向导第三页,如图1.3,该窗口可以选择FPGA硬件信息,在Family下拉框内选择“FLEX10K”,在Avaliable devices窗口选择芯片型号为:EPF10K20RC208-4,其它选项默认。

QUARTUS II 使用入门

2、 QUARTUS II系统安装

2.1 QUARTUS II安装

对于安装Quartus II 7.2版本的系统必须满足以下最低要求: 硬件:运行速度为866MHz或更快Pentium III 以上计算机,

系统内存容量大于256M。

操作系统:Microsoft Windows 2000或Microsoft Windows XP。

编译的启动方法:

选择Processing菜单的Start Compilation项即可启动全程编译

编译过程中,status窗口会显示出当前的编译的进度。

下方的process栏中会显示出编译信息,如果有出错信 息就会在其中显示。双击出错的条文,即会弹出对应的

VHDL文件。

如果编译成功,就会出现一个编译成功的信息窗口 。

3.5 应用RTL电路观察器

Quartus II支持网表文件对应的RTL电路的生成。方法如下: 选择菜单Tool中的Netlist viewers项,在出现的次级菜单中选 择RTLviewer,即可观察到设计文件对应的RTL电路结构

3.6 引脚分配

所谓引脚分配就是将设计项目的输入输出端口分配到目 标芯片的对应管脚。引脚的分配可以由分配编辑器实现,也

(3)将设计项目的端口信号选入波形编辑器。 选择菜单Edit中的Insert Node or Bus项,弹出Insert Node or Bus对话框 .

单击Node Finder按钮出现Node Finder对话框

在Node Finder对话框的Filter框中选择“Pins: all”,然后单 击List按钮,此时在下方的Nodes Found窗口出现设计项目 中的所有端口的名称。

Quartus II的许可文件的设定步骤如下: 选择菜单Tools/LicenseSetup,弹出图7.2 所示 “LicenseSetup”对话框。 单用户许可方式(single-user licenses):在“License file”对话框,点击“…”按钮选择License.dat 文件即可。 最后单击OK,完成设定。文件所许可的AMPP and MegaCore functions会出现在“Licensed AMPP/MegaCore functions”窗口中。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Quartus II中FPGA管脚的分配策略编写:***校核:审核:二〇一年月日目录目录 (I)QUARTUS II中FPGA管脚分配策略 (1)1.FPGA管脚介绍 (1).电源管脚 (1).配置管脚 (2).普通I/O管脚 (2).时钟管脚 (2)2.FPGA管脚分配方法 (3).P IN P LANNER方式 (3).I MPORT A SSIGNMENTS方式 (3).T CL S CRIPTS方式 (6).项目组统一使用方式 (8)3.编写FPGA管脚分配文件 (9).查看PDF格式的原理图 (9).查看P RJ PCB格式的原理图 (10)4.保存FPGA管脚分配文件 (11).T CL格式或CSV格式 (11).QSF格式 (11).项目组统一使用格式 (11)附录管脚类型说明 (12)Quartus II中FPGA管脚分配策略1.FPGA管脚介绍FPGA的管脚从使用对象来说可分为两大类:专用管脚和用户自定义管脚。

一般情况下,专用管脚大概占FPGA管脚数的20% ~ 30%,剩下的70% ~ 80%为用户自定义管脚。

从功能上来说可分为电源管脚、配置管脚、时钟管脚、普通I/O管脚等。

下面以Altera公司的Cyclone IV E系列芯片EP4CE30F23C8为例,如图1所示,芯片总共包含484个芯片管脚。

图中不同颜色的区域代表不同的Bank,整个芯片主要分为8个Bank,FPGA的各个管脚分布在不同的Bank中。

其中,三角形标记的管脚为电源管脚,正三角表示VCC,倒三角表示GND,三角内部的O表示I/O管脚电源,I表示内核电源。

圆形标记的管脚为普通用户I/O管脚,可以由用户随意使用。

正方形标记且内部有时钟沿符号的管脚为全局时钟管脚。

五边形标记的管脚为配置管脚。

图1 Wire Bond1.1.电源管脚FPGA通常需要两个电压才能运行,一个是内核电压,另一个是I/O电压。

每个电压通过独立的电源管脚来提供。

内核电压是用来给FPGA内部的逻辑门和触发器供电。

随着FPGA的发展,内核电压从5V、、、到,变得越来越低。

I/O电压用来给各个Bank供电,每个Bank都有独立的I/O电压输入。

一般情况下,内核电压会比I/O电压低。

图1中的VCCINT是内核电压管脚,VCCIO是I/O电压管脚。

1.2.配置管脚每个FPGA都需要配置管脚,以支持多种配置方式,例如JTAG、从串、从并、主串、主并等。

对于配置管脚的控制信号来说,是专用管脚,不能作为普通的I/O管脚。

而其数据信号可以作为普通的I/O管脚使用。

图1中的MSEL为配置模式选择信号,即选择AS模式、PS模式或FAST AS模式。

MSEL[1:0]为00表示用AS模式,10表示用PS模式,01表示用FAST AS模式。

如果用JTAG模式,MSEL[1:0]置00,JTAG模式和MSEL无关,即用JTAG模式时,MSEL会被忽略,但是因为MSEL不能浮空,所以置00。

图1中的TMS、TCK、TDI和TDO为JTAG接口的4根线,分别为模式选择、时钟、数据输入和数据输出线。

常用的为AS模式和JTAG模式。

1.3.普通I/O管脚FPGA的I/O管脚是FPGA上较为丰富的资源,也是做管脚约束时最常用的资源。

对于FPGA的普通I/O管脚,可以设定电平类型(TTL、LVTTL、LVCOMS、ECL等)、驱动电流、摆率等参数。

1.4.时钟管脚FPGA内部的时钟都需要通过专用时钟管脚连接内部PLL或者DCM等专用时钟处理单元,从而接入内部高速时钟网络。

对于一些外部同步信号的输入,如果时钟只用于采样当前的同步信号,其时钟可以不用连接到专用时钟管脚上,即不用接入全局时钟网络,但需要约束其管脚不使用全局时钟资源。

否者,EDA 工具会报错,提示其作为时钟输入而没有接在专用时钟管脚上。

更多的管脚类型说明见附录。

2.FPGA管脚分配方法FPGA管脚分配常用的有3种方式,分别为Pin Planner方式、Import Assignments方式和Tcl scripts方式。

2.1.P in Planner方式步骤1:在Quartus II软件中,选择“Assignments ? Pin Planner”,或者按快捷键“Ctrl+Shirt+N”,出现如图2所示的画面。

通过下拉菜单可以选择需要的管脚在Location选择了管脚后I/O Bank自动填充Bank内部的细分区域,非修改属性用于支持对应不同的电平标准,即VCCIO。

每个Bank只能有一种电压标准对管脚内部的I/O逻辑进行约束驱动电流强度电压转换速率,表示单位时间内电压升高的幅值图2 Pin Planner图2主要包含了7个选择项,分别为Location、I/O Bank、VREF Group、I/O Standard、Reserved、Current Strength和Slew Rate。

Location里可以选择所需要的芯片管脚,管脚确定后I/O Bank 中的Bank数会自动填充,VREF Group也会自动填充。

I/O Standard是每个Bank对应的电压标准,一个Bank只能有一种电压标准,一般情况下选择默认值就好。

Reserved是对管脚内部的I/O逻辑进行约束,有6个选择项供选择,例As SignalProbe output、As bidirectional等。

Current Strength 是驱动电流强度,一般选择默认值,如果需要驱动大功率的电路,一般在FPGA外围加驱动电路。

Slew Rate是电压转换速率,跟信号跳变时间有关,一般选择默认值。

在管脚分配的过程中,我们主要关心Location这一选项,其他选项采用默认值就可。

步骤2:在Location中选择管脚。

所有管脚配置完成后关闭当前界面。

2.2.I mport Assignments方式步骤1:新建一个txt文件(或csv文件),按图3格式编写管脚分配内容。

(编写格式有多种,但这种格式最简单。

)【注】To和Location两个关键字中间有一个半角逗。

图3 管脚分配格式步骤2:在Quartus II软件中,选择“Assignments?? Import Assignments”,出现如图4所示的画面,导入或者文件。

图4 Import Assginments导入后Quartus II软件的Message信息栏会弹出如图5所示的内容,显示Import Completed,表示文件没有语法错误。

图5 Message步骤3:在Quartus II软件中,选择“Assignments ? Pin Planner”,验证管脚是否分配正确。

如图6所示。

图6 验证管脚是否分配正确常见错误1:分配的管脚不属于FPGA芯片。

如果分配的管脚不属于FPGA芯片,在Pin Planner中会出现如图7所示的错误提示,表示管脚PIN_GC21不属于该FPGA芯片,找不到对应的I/O Bank和VREF Group。

图7 管脚不属于FPGA若信号比较多,人工不能发现存在的错误,可以通过Enable Live I/O Check工具检查I/O分配情况。

点击Pin Planner工具栏中的I/O Check图标,如图8所示。

图8 Enable Live I/O Check执行Check后,在Message窗口中会弹出检查结果,如图9所示,提示PIN_GC21是非法的管脚定义。

图9 Check检查管脚不属于FPGA常见错误2:多个信号公用一个管脚,即分配管脚冲突。

如果分配的管脚冲突,通过肉眼的方式很难发现,通过Enable Live I/O Check工具可以有效的发现存在的问题,如图10所示,提示fpga_rst_n定义的管脚G21已经被phy_clk50m信号占用。

图10 Check检查管脚冲突2.3.T cl Scripts方式步骤1:在Quartus II软件中,选择“Assignments ? Remove Assignments”,出现如图11所示的画面。

此步骤用来移除已经存在的管脚分配内容,以确保分配的管脚没有因为覆盖而出现错误的情况。

【注】在执行没有管脚分配的新工程中,可跳过步骤1。

图11 Remove Assignments步骤2:新建一个tcl文件,按图12格式编写管脚分配内容。

注意关键字set_location_assignment和-to的用法。

图12管脚分配格式步骤3:执行文件。

方法1:(1)在Quartus II软件中,选择“View?? Utility Windows?? Tcl Console”,打开Quartus II Tcl Console,如图13所示。

图13 Tcl Console(2)将tcl文件中的内容复制到Tcl Console对话框中,如图14所示。

图14 执行管脚分配语句方法2:(1)将tcl文件添加到工程中,如图15所示。

图15 添加Tcl文件(2)在Quartus II软件中,选择“Tools ? Tcl Scripts”,出现如图16所示的画面。

图16 Tcl Scripts选择“Run”,执行Tcl文件。

步骤4:在Quartus II软件中,选择“Assignments ? Pin Planner”,验证管脚是否分配正确。

检查的方法同Import Assignments方式中的Enable Live I/O Check。

2.4.项目组统一使用方式为了统一代码风格,便于项目管理,FPGA项目组统一使用的Tcl Script方式。

在的步骤3中也使用方法2,即添加Tcl文件,而非命令行。

3.编写FPGA管脚分配文件在上文提到的3种管脚分配方法中主要包含了2种文件格式,即txt和tcl。

无论那种格式的文件都是为了阐明信号与管脚的对应关系。

编写FPGA管脚分配文件的主要任务就是要快速定位工程TOP文件中各个信号与FPGA管脚的对应关系。

通过2种方式可以定位这种关系,一种是通过查看对外PDF格式的原理图,另一种是通过查看PrjPCB格式的原理图。

推荐使用PrjPCB格式的原理图。

3.1.查看PDF格式的原理图通过SVN下载相应工程,在工程路径中可以找到对应的原理图,如图17所示。

由于PDF格式的原理图没有目录,如图18所示,查找各个模块比较费时费力,所以不推荐这种方式。

图17 原理图路径图18 PDF格式原理图3.2.查看PrjPCB格式的原理图查看原理图的软件有多种,我司主要使用Altium Designer软件。

通过SVN下载相应工程,在工程路径中可以找到对应的原理图,如图19所示。

图19 原理图路径用AD软件打开图15中的文件,打开后如图20所示。

左侧文件预览窗口罗列了整个板件各个模块的原理图,最后两个和就是FPGA部分的原理图。