双向移位寄存器

双向移位寄存器 (2)

双向移位寄存器

双向移位寄存器是一种能够在输入数据串和输出数据串之间实现双向数据传输的寄存器。

它可以通过控制信号来实现数据的左右移位操作。

双向移位寄存器通常由多个触发器组成,每个触发器都能够存储一个比特位。

这些触发器之间通过电路连接,形成一个寄存器。

在双向移位寄存器中,有两个输入端和两个输出端。

一个输入端被称为数据输入端,用于将外部数据输入到寄存器中。

另一个输入端被称为控制输入端,用于控制数据的移位方向(左移或右移)。

当控制输入端接收到移位信号时,寄存器可以执行左移或右移操作。

左移操作将所有触发器中存储的数据向左移动一位,其中最左边的触发器的输出位被丢弃,最右边的触发器的输入位接收一个新的数据位。

类似地,右移操作将

所有触发器中存储的数据向右移动一位,其中最右边的触

发器的输出位被丢弃,最左边的触发器的输入位接收一个

新的数据位。

双向移位寄存器的输出端将从寄存器中读取数据,并将其

作为输出数据串输出。

输出端和输入端可以通过控制信号

来切换,实现双向数据传输。

双向移位寄存器在许多应用中都有用途,比如数据缓冲和

数据传输等。

它可以灵活地处理不同方向的数据移位操作,并且能够实现高效的数据传输。

74164移位寄存器资料

5

集成异步二进制计数器74293

Q3 Q3 J3 C P3 Q3 K3 Q2 Q2 Q2 J2 C P2 K2 Q1 Q1 Q1 J1 C P1 K1 Q0 Q0 Q0 J0 C P0 K0 R1 R2 C P1 C P0

逻辑电路

74293功能: R1、R2:复位信号, R1和R2同时为“1”时输出被清零。 Q0 是 1bit 计数器; Q3Q2Q1 是 3bit 计数器; 如果把CP1接Q0,则Q3Q2Q1Q0组成 4bit 二进制计数器。

7490的两种接法

CP1与Q1相连构成 8421BCD码

CP0 0 1 2 3 4 5 6 7 8 9 Q3 0 0 0 0 0 0 0 0 1 1 Q2 0 0 0 0 1 1 1 1 0 0 Q1 0 0 1 1 0 0 1 1 0 0 Q0 0 1 0 1 0 1 0 1 0 1

CP0与Q3相连构成 5421BCD码

Qa Sd C P1 C P2

& Q

Qb Rd Sd

Q

Qc Rd Sd

Q

Qd Rd Sd

Q

Байду номын сангаас

Rd

J CP K

J CP K

J CP K

J CP K

& &

& &

& &

&

&

A

C /L

Rd

B

C

D

10

集成同步二进制加计数器74161

符号:

Q0 Q0

CP LD

Q1 Q1

Q2 Q2

Q3 Q3

C C

74161

Q 0Q 1Q 2Q 3 R d S 1 S 2

实验5 双向移位寄存器 (2010)

实现74LS194左移、右移逻辑功能的逻辑电路图:

5.测试74LS194的右循环移位逻辑功能和左循环移位逻辑功 能(即构成环形计数器),用发光二极管显示,并列出状态

转换表。

设计思路提示:移位寄存器的最高输出接至最低位的输入 端;或将最低位的输出接至最高位输入端,即将移位寄存器 的首尾相连就可实现。

四

实验步骤

1.根据实验指导书中实验内容1、2、3的要求,对双向移位寄 存器74LS194进行功能测试。 2.根据与非门的逻辑功能,检测芯片的好坏。 3.根据实验指导书中实验内容4、5的要求,设计电路,并在 实验装置上安装电路,验证理论设计的正确性。

五 常见问题

1.芯片使用前不进行功能好坏的检测。 2.电源连接不正确,接地点接到-5V上或接到模拟电子实验 箱的电源上,非常危险,上电后芯片烧毁。 3.逻辑开关电平前的发光二极管不亮,检查进入数字实验 箱的电源连接线是否断。 4.实验箱电源连接正确,电路自查确定无误后,电路验证 还是不正确的情况下进行下面的排错检查: (1)检查芯片的电源和地的电平是否正确。 (2)芯片的清零连接电平是否正确。 (3)芯片的控制电平(M1,M0)是否正确。 (4)从逻辑电平开关输入信号是否正确。 (5)时钟信号是否正确输入。 (6)从输出端按逻辑功能状态往前一步一步排查。

三 实验内容与实验原理

1.双向移位寄存器74LS194介绍 双向移位寄存器的逻辑图

双向移位寄存器逻辑功能

双向移位寄存器74LS194的引脚图

数据输 出端

数据输 入端

时钟 信号

控制Hale Waihona Puke 信号清零端右移输入端

左移输入端

2.测试74LS194的置数功能,用发光二极管显示。

3.测试74LS194的右移逻辑功能,用发光二极管显示,并将 状态填入表1。 4.测试74LS194的左移逻辑功能,用发光二极管显示,并将 状态填入表2。

d触发器构成的双向移位寄存器

d触发器构成的双向移位寄存器一、概述双向移位寄存器是一种能够实现数据在两个方向上移位的寄存器,其常用于串行通信、计数器等电路中。

其核心部件为d触发器构成的双向移位寄存器。

二、d触发器d触发器是一种基本的时序电路,其输入为数据输入端d和时钟输入端clk,输出为输出端q和反相输出端q'。

当clk上升沿到来时,其将输入端d的值传输到输出端q上,并保持该状态直到下一个时钟上升沿到来。

三、双向移位寄存器1. 正向移位当控制信号sel=0时,数据从右侧进入寄存器,并从左侧出去。

具体实现方式为:将右侧d触发器的数据输入端连接至外部数据线,左侧d触发器的数据输入端连接至右侧d触发器的输出端。

2. 反向移位当控制信号sel=1时,数据从左侧进入寄存器,并从右侧出去。

具体实现方式为:将左侧d触发器的数据输入端连接至外部数据线,右侧d触发器的数据输入端连接至左侧d触发器的输出端。

四、构成原理双向移位寄存器由两个d触发器构成,其中一个为正向移位的d触发器,另一个为反向移位的d触发器。

控制信号sel用于控制数据的进出方向。

1. 正向移位当sel=0时,右侧d触发器接收外部数据输入,左侧d触发器接收右侧d触发器的输出。

当时钟上升沿到来时,右侧d触发器将数据传递至左侧d触发器,并保持该状态直到下一个时钟上升沿到来。

此时,左侧d触发器将其输出端的值传递至外部输出线。

2. 反向移位当sel=1时,左侧d触发器接收外部数据输入,右侧d触发器接收左侧d触发器的输出。

当时钟上升沿到来时,左侧d触发器将数据传递至右侧d触发器,并保持该状态直到下一个时钟上升沿到来。

此时,右侧d触发器将其输出端的值传递至外部输出线。

五、应用场景双向移位寄存器常用于串行通信、计数器等电路中。

在串行通信中,双向移位寄存器可实现数据在串行通信线路中的进出操作;在计数器中,双向移位寄存器可实现计数器的正向和反向计数操作。

六、总结双向移位寄存器是一种能够实现数据在两个方向上移位的寄存器,其核心部件为d触发器构成的双向移位寄存器。

74LS194芯片资料

单脉冲的提供有两种途径:

实验目的

逻辑箱脉冲源

单脉冲

实验原理

低频信号源TTL 输出(1Hz)

实验内容

注意事项

现代电子技术实验

四、注意事项

1、出现故障应作哪些基本检查? 电源

实验目的

时钟 功能端(Cr 、S1、 S0 ) 数据输入是否正确

实验原理

实验内容

注意事项

2、实验中的环形计数器不具备自启动功能,抗 干扰能力差。改变电路连接时如进入死循环,必 须给电路重新赋初值。

实验目的

DSR

清零 置数

CP

0 1

DR

1 1

DL

1 1

Q0

0 0

Q1

0 1

Q2

0 0

Q3

0 1

实验原理

左移

实验内容

2 3

4

0 0

1

0 0

1

左移

右移

注意事项

右移 保持

5 6

1 0

1 0

现代电子技术实验

2、环形计数器的测试。首先应给寄存器置入初始 值(自拟),之后将工作状态设为对应的串行移 位,完成下表。

现代电子技术实验

移位寄存器的扩展

实验目的

实验原理

ห้องสมุดไป่ตู้

74LS194(1)

实验内容

74LS194(2)

注意事项

串行输入

构成八位右移串行移位寄存器

现代电子技术实验

2、环形计数器(又称循环移位寄存器)

把移位寄存器的串行输入端与输出端相连可以 构成环形计数器。例:DSR和Q3相连,可构成右移环 形计数器。

实验目的

n 2

0 X X

双向移位寄存器实验指导书

4) 回到波形编辑窗口,对所有输入端口设置输入波形,具体可以通过左边的工 具栏,或通过对信号单击鼠标右键的弹出式菜单中完成操作,最后保存次波形文 件。

4. 进行功能仿真 1) 单击 Assignments\Settings…,在弹出对话框中做以下设置:

-5-

制作人:程鸿亮

长安大学 电子与控制工程学院 电子科学与技术系

SPEAKER CLOCK0 CLOCK2 CLOCK5 CLOCK9

引脚号 C13 C7 H3 U3 P3 F4 C10 C16 G20 R20 AB16 AB17 AB18 AB19 AB20 AB7 AB8 AB11 A10 A9 A8 A7 A6 A5 A4 A3 AB9 AB10 B5 Y10

⒈⒉⒊⒋⒌⒍⒎⒏ ⒐⒑⒒⒓⒔⒕⒖⒗

四、实验步骤: 1. 打开 QuartusII 软件,建立一个新的工程: 1) 单击菜单 File\New Project Wizard…

2) 输入工程的路径、工程名以及顶层实体名。 3) 单击 Next>按钮,出现以下窗口

由于我们建立的是一个空的项目,所以没有包含已有文件,单击 Next>继续。 4) 设置我们的器件信息:

如图所示,Simulation mode 设置为 Functional,即功能仿真。指定仿真波形文件 后单击 OK 完成设置。 2) 单击 Processing\Generate Functional Simulation Netlist 以获得功能仿真网络表。 3) 单击 Processing\Start Simulation 进入仿真页面:

E8

I/O29

E7

I/O30

D11

I/O31

D9

I/O32

D8

四位双向移位寄存器

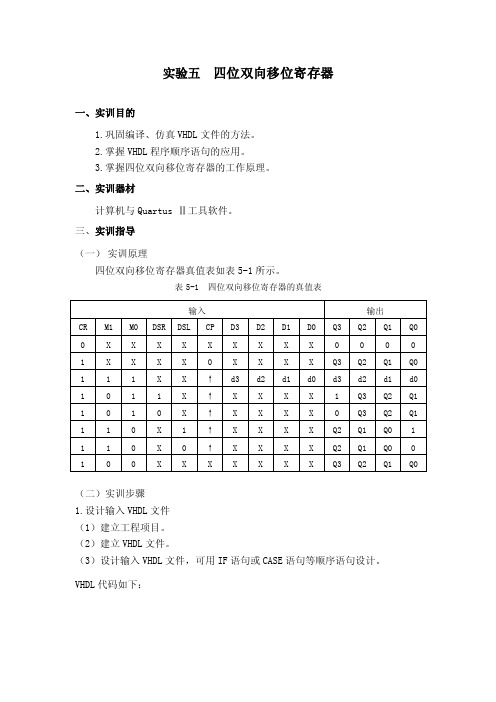

实验五四位双向移位寄存器一、实训目的1.巩固编译、仿真VHDL文件的方法。

2.掌握VHDL程序顺序语句的应用。

3.掌握四位双向移位寄存器的工作原理。

二、实训器材计算机与Quartus Ⅱ工具软件。

三、实训指导(一)实训原理四位双向移位寄存器真值表如表5-1所示。

表5-1 四位双向移位寄存器的真值表输入输出CR M1 M0 DSR DSL CP D3 D2 D1 D0 Q3 Q2 Q1 Q00 X X X X X X X X X 0 0 0 01 X X X X 0 X X X X Q3 Q2 Q1 Q0 1 1 1 X X ↑d3 d2 d1 d0 d3 d2 d1 d0 1 0 1 1 X ↑X X X X 1 Q3 Q2 Q1 1 0 1 0 X ↑X X X X 0 Q3 Q2 Q1 1 1 0 X 1 ↑X X X X Q2 Q1 Q0 1 1 1 0 X 0 ↑X X X X Q2 Q1 Q0 0 1 0 0 X X X X X X X Q3 Q2 Q1 Q0(二)实训步骤1.设计输入VHDL文件(1)建立工程项目。

(2)建立VHDL文件。

(3)设计输入VHDL文件,可用IF语句或CASE语句等顺序语句设计。

VHDL代码如下:LIBRARY ieee;USE ieee.std_logic_1164.ALL;ENTITY YWJCQ4 ISPORT(M:IN STD_LOGIC_VECTOR(1 DOWNTO 0);D:IN STD_LOGIC_VECTOR(3 DOWNTO 0);CR,CP,DSR,DSL:IN STD_LOGIC;Q:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0)); END YWJCQ4;ARCHITECTURE W OF YWJCQ4 ISBEGINPROCESS(CR,CP,DSR,DSL,M,D)BEGINIF CR='0' THEN Q<="0000";ELSIF (CP='1' AND CP'EVENT) THENCASE M ISWHEN "11"=>Q<=D;WHEN "01"=>Q<=DSR&Q(3 DOWNTO 1);WHEN "10"=>Q<=Q(2 DOWNTO 0)&DSL;WHEN OTHERS=>Q<=Q;END CASE;END IF;END PROCESS;END W;2.编译仿真VHDL文件(1)编译VHDL文件。

40194四位双向移位寄存器

40194四位双向移位寄存器40194 为4 位通用移位寄存器,具有并行输入/并行输出,左移、右移等功能。

40194 的工作模式由两个模式选择输入端SELECT0 和SELECT1 确定,当处于SELECT0=SELECT1=“1”时,并行输入端在时钟上升沿并行数据输入端。

D0~D3 的数据置入4 位寄存器中并由Q 端输出。

进行左移或右移操作时,SHIFTRIGHT IN 和SHIFT LEFT IN 端上的数据在时钟上升沿分别串行移入寄存器中,当/RESET 为低电平时,输出全零状态。

引出S1 S00 0 保持不变0 1 实行右移1 0 实行左移1 1 运行置数R 清零;低电平有效40192------十进制同步加/减计数器(有预置端,双时钟)简要说明:40192 为可预置BCD 可逆计数器,其内部主要由四位D 型触发器组成,与一般计数器不同之处在于加计数器和减计数器分别由两个时钟输入端。

40192 具有复位CR、置数控制/LD、并行数据D0~D3、加计数时钟CPu、减计数时钟CP D 等输入,当CR 为高电平时,计数器置零。

当/LD 为低电平时,进行预置数操作,D0~D3 上的数据置入计数器中,计数操作由两个时钟输入控制。

当CP D=“1”时,在CPu 上跳变时计数器加1 计数;当CPu=“1”时,在CP D 上跳变计数器减1 计数。

除四个Q 输出外,40192 还有一个进位输出/CO 和一个借位输出/BO,/CO 和/BO 一般为高电平,只有在加计数模式,当计数器达到最大状态时,/CO 输出一个宽度为半个时钟周期的负脉冲,在减计数模式,当计数器全为零时,/BO 输出一个宽度为半个时钟周期的负脉冲。

引出端符号:CR 清除端;CP D 减计数时钟输入端;CPu 加计数时钟输入端;D0~D3 并行数据输入端;Q0~Q3 计数器输出端;/BO 借位输出端;/CO 进位输出端V DD 正电源;Vss 地引出真值表:40192功能输入端PE R0 0 置数1 0 计数× 1 清零。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

、课程设计的目的与要求

1.设计目的

熟悉MAXPLUS2/Quartus II 软件,掌握软件的VHDL 程序输入、程序编译和程序仿真操作;

学习利用VHDL 语言设计双向移位寄存器电路程序。

2.设计要求根据设计正文提出的双向移位寄存器功能设置,实现电路设计。

、设计正文

双向移位寄存器有三种输入方式: 4 位并行输入、 1 位左移串行输入、 1 位右移串行输

入;

双向移位寄存器有一种输出方式: 4 位并行输出。

双向移位寄存器工作过程如下:

当 1 位数据从左移串行输入端输入时,首先进入内部寄存器最高位,并在并行输出口最高位输出,后由同步时钟的上跳沿触发向左移位。

当 1 位数据从右移串行输入端输入时,首先进入内部寄存器最低位,并在并行输出口的最低位输出,后由同步时钟的上跳沿触发向右移位。

双向移位寄存器的输入、输出端口如下:

CLR :异步清零输入端;

SRSI :串行右移输入端;

SLS I :串行左移输入端;

A 、B、C、D: 4 位并行输入端;

QA、QB、QC、QD: 4 位并行输出端;

SO, S1:两位控制码输入端。

双向移位寄存器的端口功能如下:

当CLR = 0时,4位输出端清0;

当CLK = 0时,4位输出端保持原来状态不变;

当S= 00时,4位输出端保持原来的状态不变;

当S= 01时,允许串行右移输入1位数据;

当S= 10时,允许串行左移输入1位数据;

当S= 11时,允许4位数据从并行端口输入。

VHDL源程序:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL; ——包含库和程序包

entity double_dir_regt is ——定义实体为double_dir_regt

port ( s: in std_logic_vector(1 downto 0);

clr,clk,srsi,slsi,a,b,c,d:in std_logic;

result: out std_logic_vector(3 downto 0)); ——设置端口参数输入控制信号s, 时钟clk, 并行输入abcd, end double_dir_regt; 输出result ARCHITECTURE rtl of double_dir_regt is

signal result1: std_logic_vector(3 downto 0); ——设置信号result1 使result 能作为输入使用begin result<=result1;

process (clk,clr) ——敏感信号为时钟和清零信号begin

if (clr='0')then result1<="0000";

elsif (clk'event and clk='1')then

case s is

when "00"=> ——控制信号为00 时实现保持功能result1(0)<=result1(0);

result1(1)<=result1(1);

result1(2)<=result1(2);

result1(3)<=result1(3);

when"01"=> ——控制信号为01 时实现右移功能result1(3)<=srsi;

result1(2)<=result1(3); result1(1)<=result1(2); result1(0)<=result1(1);

控制信号为10时实现左移功能

end case; end if; end process; end rtl;

三、课程设计总结

1

由上图1看出当sOs 仁01时,寄存器执行右移功能,并可看出 srsi=1100110011001100.

whe n"10"=>

whe n"11"=>

result1(0)<=slsi; result1(1)<=result1(0); result1(2)<=result1(1); result1(3)<=result1(2);

控制信号为11时实现并行输入功能

result1(0)<=a; result1(1)<=b; result1(2)<=c; result1(3)<=d;

程序结束

输出结果result 依次由初始状态 0000,逐渐右移左端输入端口输入 srsi=1100110011001100, 此时result 依次会出现1000:移入1; 1100:移入两个1; 0110:移入两个1 一个0;再有 以后出现的结果

能。

0011,1001,1100,0110,0011,1001,1100……••此结果符合真值表要求的右移功

M 已成訓Time

10.6 n?

*\¥

\ PoHer :

45.53 rte

Iriteivat | 37.83 ns 5臥:

EM

J ps

10 0 BS EQ.g ns

30. HE

40.0 ns : 50 0 DE

60 0 DE

10. Q ns

Till

畑岂

nr

dk

n r"L r L r L TT r

L n

Hr 1 1

0 0

1 1

0 0 1 1 0 0 1 1

slsi

1 1 1

ETsil

r

1 1

国M

ID

a

!>•

b

e

LZ

i

H result :oooo X

ioorx ooii x

■onTHioTl iwnrooTT^^TTnniM - Ciooi ^3510711^0^0^0;

图表2双向移位寄存器左移仿真波形图

由上图2看出当s0s1=10时,寄存器执行左移功能,并可看出 slsi=1100110011001100, 输出结果result 依次由初始状态 0000,逐渐右移左端输入端口输入

slsi=1100110011001100,

此时result 依次会出现0001 :移入1; 0011 :移入两个1 ; 0110:移入两个1 一个0;再有 以后出现的结果 1100,1001, 0011,0110, 1100,1001, 0011……..此结果符合真值表要求的左移 功能。

图表3双向移位寄存器并行输入仿真波形图

如图3中控制信号s0s1=11,寄存器执行四位并行输入功能, 输入端为图中a,b,c,d=0110,

当时钟脉冲到来后,寄存器输出端 result 输出结果应为并行输入数据

abcd=0110,根据仿真

波形图可知,输出结果

result 先出现0000的初始结果,经过一段时间的延迟,输出

result=0110,为并行输入数据,实现了并行输入的功能。

M aster Tim 占 Bar:

0 p$

< 卜]Pointis 匚

Interva l:

0 ps

由图4中当控制信号sOs1=1O时实现左移功能,得到0000,0001 , 0011, 0110的输出结

果,当s0s仁00时,输出result 一直保持0110不变,实现保持功能,根据仿真波形图可知,寄存器实现了保持的功能。

综合以上四波形图,寄存器实现了实验要求的保持,右移,左移,并行输入的功能。