Verdi培训整理笔记

Verdi使用小技巧(一)

Verdi使⽤⼩技巧(⼀)对于做数字集成电路的⼯程师来说,Verdi可以说是最常⽤的代码和波形观察⼯具了。

这⾥列⼏个使⽤中的⼩技巧,说不上⾼明,不过⾃⼰⽤着感觉还是蛮有效率的。

1分析波形的时候有时候需要把⼀个多⽐特的bus拆分成⼏个位宽较⼩的bus,以⽅便观察数值。

例如把⼀个20⽐特的bus拆成两个10⽐特的bus,可以右键点击这个bus,在弹出的菜单中点击Bus Operation,在弹出的对话框中的Every后⾯的输⼊框,输⼊10,意思是每10⽐特拆成⼀个bus,点击ok,就会看到出现了两个10⽐特的bus信号以及对应的波形。

2、统计统计出某个信号在特定时间段内的跳变的次数。

这个结合下⼀节的逻辑运算,可以把⼀些复杂的波形分析⽤直观的形式表现出来。

还是右键点击波形窗⼝左边的某个信号名字,在弹出菜单中选择Signal Event Report。

在弹出的对话框中,可以关注感兴趣的内容,⽐如Rising#,指的是默认Markers标定的时间段内,该信号的上升沿次数。

这样就不⽤很⾟苦的放⼤波形,⽤眼睛⼀个⼀个去数了。

3在⼀个频繁变化的信号、尤其是多⽐特的bus信号中观察是否出现了某个值,有时候可以通过搜索来追踪。

但是如何⼀⽬了然地看到呢?通过右键点击该信号,在弹出的菜单上点击Logical Operation,通过新建⼀个信号,该信号是待观察信号的某种逻辑表达式。

⽐如,想知道这个state等于0x7的分布情况,就可以新建⼀个信号state_is_7等于state==0x7,这样看这个新信号什么时候为1,就可以了解特定状态的分布情况了。

4、manage.rc可以管理多个rc⽂件,实现每次启动Verdi都能载⼊预设的设置,同时不受上次启动Verdi后保存的设置影响。

还可以保存本次使⽤过程中更改过的设置,以便更新预设设置。

这个略微有些复杂。

在启动Verdi时,需要加个参数。

-managercFile some_path/manage.rc这个manage.rc的内容⼤概是这样的:1@Manage rc file Version 1.02[File]3default_file = ~/load_only.rc4working_file = ./novas.rc56[Load]7default_file89[Save]10working_file = MODIFIED_KEY例⼦中作为只读的default_file⽂件,可以放⼀些⾃⼰习惯或者喜欢的设置。

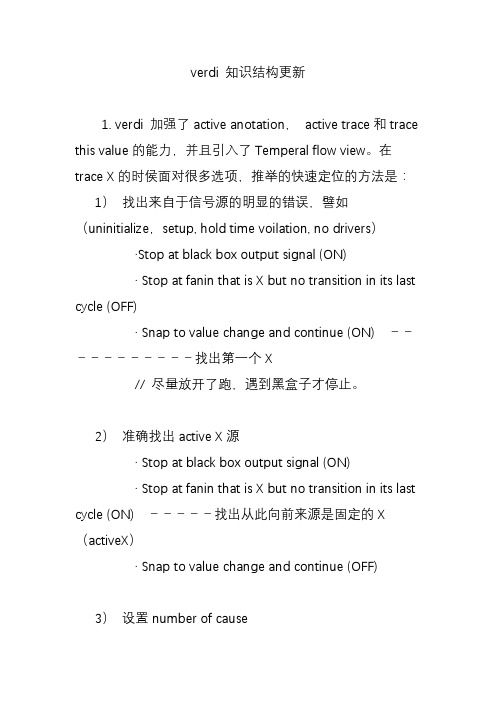

verdi 知识结构更新

verdi 知识结构更新1. verdi 加强了active anotation,active trace和trace this value的能力,并且引入了Temperal flow view。

在trace X的时侯面对很多选项,推举的快速定位的方法是:1)找出来自于信号源的明显的错误,譬如(uninitialize,setup, hold time voilation, no drivers)·Stop at black box output signal (ON)· Stop at fanin that is X but no transition in its last cycle (OFF)· Snap to value change and continue (ON) -----------找出第一个X// 尽量放开了跑,遇到黑盒子才停止。

2)准确找出active X源· S top at black box output signal (ON)· Stop at fanin that is X but no transition in its last cycle (ON) -----找出从此向前来源是固定的X (activeX)· Snap to value change and continue (OFF) 3)设置number of cause· Use the default setting : S top after finding 1 cause· 如果遇到很多类似的cause,那么设为trace all causes2. 当碰到ntrace和fsdb的hierarchy层次不一样时,不能联动。

解决方案set virtual topvritual top/map file:CPU =system.i_cpu3. 在VMM中引入fsdbLog[c-sharp] view plain copy `ifdef FSDB class log2fsdb extends vmm_log_format; virtual function string format_msg(string name, string inst, string msg_typ, string severity, ref string lines[$]); string text = ""; string stream = $psprintf("%s(%s)", name, inst);string label = $psprintf("%s[%s]", severity, msg_typ); foreach(lines[i]) text = {text, "/n", lines[i]};$fsdbLog(label, text, , stream ); format_msg = super.format_msg(name, inst, msg_typ, severity, lines); endfunction endclass `endif `ifdef FSDBif($test$plusargs("fsdb=")) begin log2fsdbl2f = new; this.log.set_format(l2f);end `endif4. 波形比较找出mismatch point,然后在定位发生mismatch的原因如果是相同的design view,Waveform comparison -> behavior trace for fsdb mismatch---》适合RTL和RTL的比较,定位引起错误的源头如果是不同的design view,Waveform comparison -> Trace this value in flow view for different design5. 利用siloti减少波形记录文件大小,进而加快仿真速度步骤如下:1. 生成主要信号的列表文件esa -bas tb_CPUsystem -f run.f -all_eslistfullchip.list// -bas 指明了work scope,即一旦design 加载就立刻进行behavior analyse的范围// -all_eslist 指明了生成hierachy 和plain list 两种形式的信号列表文件2. dump 主要信号的波形· $fsdbDumpfile("ess.fsdb");· $fsdbDumpvarsToFile("fullchip.list");3. 启动verdi,在必要时打开visibility的相关选项Tools -> Visibility -> Data Expansion -> Enable Data Expansion6. ntrace 可以吃进prime time 的STA report 文件并自动将其转为XML文件,用以形象的debug timing的关键路径为何出现问题File -> Import Path Data File -> Select the violate_path.rpt· Show this path on nSchema· Show this path on File Viewer· D&D the 42.860 delay from File Viewer into nSchema· Debug the reason of this huge delay on schematic window· Tools-> New Schematic ->Connectivity7. 当gate level和rtl level 的波形不一致时可以采用“tracetriggering path,based on transition,来找到由于时序问题产生错误的根源”steps:1. compare rtl and gate simulation mismatch,以gate wave form 为主导2. 在产生变化的地方(transition发生处),产生TFV3. trace triggering path 并设为stop at Register Boundary4. 找到源头后,ctrl+K把clock放入waveform中加以分析。

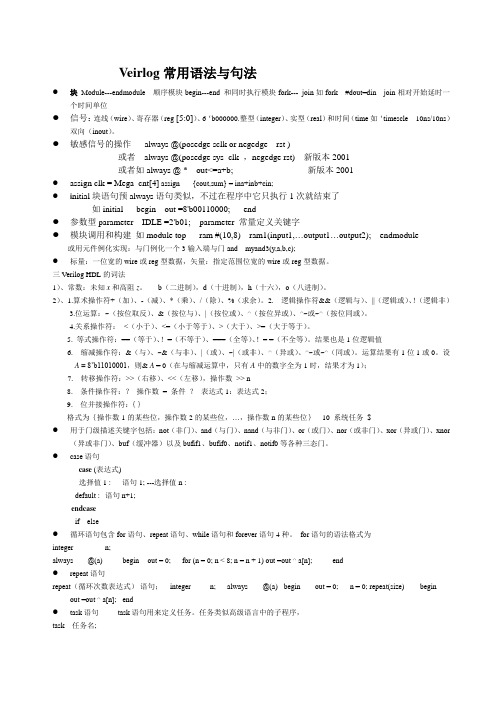

veirlog常用的关键字及应用

Veirlog常用语法与句法●块Module---endmodule 顺序模块begin---end 和同时执行模块fork--- join如fork #dout=din join相对开始延时一个时间单位●信号:连线(wire)、寄存器(reg [5:0])、6‘b000000.整型(integer)、实型(real)和时间(time如‘timescle 10ns/10ns)双向(inout)。

●敏感信号的操作always @(posedge sclk or negedge rst )或者always @(posedge sys_clk ,negedge rst) 新版本2001或者如always @ * out<=a+b; 新版本2001●assign clk = Mega_cnt[4] assign {cout,sum} = ina+inb+cin;●i nitial块语句预always语句类似,不过在程序中它只执行1次就结束了如initial begin out =8'b00110000; end●参数型parameter IDLE =2'b01; parameter 常量定义关键字●模块调用和构建如module top ram #(10,8) ram1(input1,…output1…output2); endmodule或用元件例化实现:与门例化一个3输入端与门and myand3(y,a,b,c);●标量:一位宽的wire或reg型数据,矢量:指定范围位宽的wire或reg型数据。

三Verilog HDL的词法1)、常数:未知x和高阻z。

b(二进制),d(十进制),h(十六),o(八进制)。

2)、1.算术操作符+(加)、-(减)、*(乘)、/(除)、%(求余)。

2. 逻辑操作符&&(逻辑与)、||(逻辑或)、!(逻辑非)3.位运算:~(按位取反)、&(按位与)、|(按位或)、^(按位异或)、^~或~^(按位同或)。

verdi的基本操作 -回复

verdi的基本操作-回复如何使用verdi进行基本操作。

Verdi是一个用于开发和验证分布式系统的工具集。

它提供了许多功能,包括交互式命令行界面、验证引擎和模型检查器等。

本文将引导您一步一步学习如何使用Verdi进行基本操作。

步骤一:安装Verdi首先,您需要在本地计算机上安装Verdi工具集。

您可以从Verdi的官方网站或开发者社区的GitHub页面上下载最新版本的Verdi。

安装完成后,请确保Verdi所依赖的所有软件和库已正确安装。

步骤二:启动Verdi一旦您成功安装了Verdi,您可以在终端中输入“verdi”命令来启动Verdi。

如果一切正常,您将看到一个交互式命令行界面。

步骤三:导入项目在Verdi中,您可以使用“cd”命令导航到您的项目目录中。

一旦在项目目录中,您可以使用“import”命令来导入您的项目。

例如,如果您的项目位于“/home/user/myproject”目录下,您可以输入“import myproject”来导入该项目。

步骤四:构建项目在导入项目后,您需要构建该项目以准备进行后续操作。

您可以使用“build”命令来构建项目。

例如,输入“build myproject”将构建名为“myproject”的项目。

步骤五:加载模型在Verdi中,您可以使用模型来描述和验证您的系统。

您可以使用“load”命令来加载一个模型。

例如,输入“load mymodel.v”将加载名为“mymodel.v”的模型文件。

步骤六:模型检查一旦您加载了模型,您可以使用Verdi的模型检查器来验证该模型。

Verdi提供了一些内置的模型检查器,可以帮助您检测并发性错误、死锁等问题。

您可以使用“check”命令来启动模型检查器。

例如,输入“check -deadlock mymodel”,Verdi将检查该模型是否存在死锁。

步骤七:交互式调试在Verdi中,您可以使用交互式调试器来调试您的分布式系统。

verdi使用手册

verdi使用手册Verdi是一款功能强大的EDA工具,主要用于数字电路设计和仿真。

本文将为您提供一份简明的Verdi使用手册,帮助您快速上手并充分利用该软件的各项功能。

一、Verdi简介Verdi是由Synopsys公司开发的一款集成电路设计和验证工具。

它具有直观的用户界面和强大的调试功能,可帮助工程师快速定位和解决设计中的问题。

以下是Verdi的一些主要功能特点:1. 信号跟踪:通过Verdi,用户可以轻松跟踪信号路径,并进行信号的波形查看和分析。

这有助于快速定位设计中的错误或故障。

2. 波形分析:Verdi提供了多种波形查看和分析工具,包括信号波形、时序波形等。

用户可以通过这些工具对波形进行详细的观察和分析。

3. 内存调试:对于复杂的设计,内存中的数据往往难以查看和分析。

Verdi提供了内存调试功能,可以帮助用户直观地查看和分析内存中的数据。

4. 时序分析:时序是数字电路设计中的重要因素之一。

Verdi支持对时序进行全面的分析,并提供了各种时序相关的调试工具。

二、Verdi的基本操作1. 安装和启动:首先,确保您已经成功安装了Verdi软件。

双击Verdi的图标,或通过命令行输入“verdi”命令即可启动该软件。

2. 工程管理:在Verdi中,您可以创建一个工程来管理您的设计文件。

通过选择“文件”->“新建工程”,然后按照提示来设置工程的名称、路径等信息,即可创建一个新的工程。

3. 导入设计文件:选择“文件”->“导入文件”,然后选择您的设计文件,点击“导入”按钮即可将文件导入到Verdi中。

4. 信号跟踪:在Verdi的主界面上,选择“工具”->“信号跟踪”,然后通过鼠标点击需要跟踪的信号线路,即可实现信号路径的跟踪。

5. 波形查看:选择“工具”->“波形查看器”,然后选择需要查看的波形文件,即可在波形窗口中查看和分析信号波形。

三、Verdi高级功能1. 时序分析:Verdi提供了丰富的时序分析功能,包括时钟周期分析、时序违规检查等。

verdi基础命令

verdi基础命令(原创实用版)目录1.Verdi 基础命令概述2.Verdi 基础命令的具体内容3.Verdi 基础命令的使用方法4.Verdi 基础命令的应用场景5.总结正文1.Verdi 基础命令概述Verdi 是一款功能强大的分布式版本控制系统,它采用了分布式架构,具有高性能、可扩展性强、安全性高等特点。

Verdi 提供了丰富的命令来满足用户的各种需求,这些命令可以分为基础命令和高级命令。

本文将介绍 Verdi 的基础命令。

2.Verdi 基础命令的具体内容Verdi 的基础命令主要包括以下几类:(1)版本控制操作命令:这类命令主要用于版本控制,包括提交、更新、合并等操作。

例如:- commit:提交更改,将当前分支的更改提交到版本库。

- update:更新当前分支,将远程仓库的更改合并到本地分支。

- merge:合并分支,将指定分支的更改合并到当前分支。

(2)分支管理命令:这类命令主要用于分支管理,包括创建、切换、删除分支等操作。

例如:- create:创建新分支,将当前分支的更改复制到新分支。

- switch:切换分支,将当前分支切换到指定分支。

- delete:删除指定分支。

(3)标签管理命令:这类命令主要用于标签管理,包括创建、切换、删除标签等操作。

例如:- tag:创建新标签,将当前分支的更改打上标签。

- switch:切换标签,将当前分支切换到指定标签。

- delete:删除指定标签。

(4)权限管理命令:这类命令主要用于权限管理,包括授权、撤销权限等操作。

例如:-授权:为指定用户或组分配权限。

-撤销权限:撤销指定用户或组的权限。

3.Verdi 基础命令的使用方法Verdi 基础命令的使用方法较为简单,通常遵循以下格式:```verdi <command> [options] [arguments]```其中,`<command>`表示要执行的命令,`[options]`表示可选的参数,`[arguments]`表示必须的参数。

Verdi培训整理笔记

Verdi思源科技股份有限公司Verdi基本培训基于Verdi 2010.01版权©2009 Spring Soft.Inc.保留所有版权没有思源科技股份有限公司的书面许可,不得以任何形式或任何方式复制这个培训的内容。

商标文件中所用到的产品名称是他们各自的所有商标或注册商标。

机密文件中的信息是机密的,并且适用于思源科技与贵组织之间的许可协议。

使用和公开是受限制的。

目标帮助你理解复杂设计当发现bug时,帮助你快速追踪到根源在一个统一且友好的环境中做调试和验证目标受众结构工程师开发工程师验证工程师必要条件基本的HDL/HVL编程能力:Verlog,VHDL,System Verilog,SVA熟悉标准的仿真器摘要技术背景建立环境理解FSDB Dumping(存储)任务和重用性输入设计在源代码界面调试在波形界面调试在原理图界面调试在FSM界面调试在时序界面调试附录:常用参数术语:RMB Right Mouse Button 鼠标右键MMB 鼠标中键LMB 鼠标左键DC 双击D&D 拖拽KDB 知识数据库模块FSDB 快速信号数据库TFV 时序界面BA 行为分析技术背景在设计流程中调试ESL RTL Gate设计 SCAN 时序构建行为 设计(定位) Testbench 验证交互正式回归 编译器 扫描 收敛 验证交互方式IP遗产 断言属性 仿真/加速你知道你的团队调试花费多少时间吗?你会用那个时间做什么?阻碍有效调试复杂设计更难理解复杂的行为复杂设计引起并影响方案增加验正条件复杂的多用工具、多组环境混合方法复杂性Novas解决艰难的调试问题问题复杂环境复杂行为复杂设计理解 自动化 统一增加自动化 Verdi强大的理解和调试Novas技术编译器和接口 数据库 分析引擎 形象化→知识数据库→行为分析 时序界面↓ 结构分析 源代码工具的全范围→FSDB →断言评价 → 波形/事件事件数据库 事务/信息分析 原理/结构FSM/流表断言/信息/事务理解调试系统——不只简单的形象化结构/事件调试过程当前过程包括比较时间、代码和结构在多种窗口跟踪可能的问题。

verdi 使用技巧

verdi 使用技巧Verdi(Visual Environment for Remote Debugging)是一款开源的调试工具,可以帮助我们更轻松地进行远程调试。

如果你作为一个Python开发者,使用verdi几乎是必不可少的。

在本篇文章中,我们将分享一些有关verdi的使用技巧,以帮助您更好地利用它。

一、安装verdiVerdi可以通过pip install命令进行安装,如下所示:pip install aiida-core[verdi]二、登录到远程计算机如果您使用的是verdi进行远程调试,那么首先需要使用verdi登录到远程计算机。

您可以使用以下命令:verdi computer configure三、查看当前计算机状态您也可以使用verdi命令查看当前计算机的状态和可用的任务。

您可以使用以下命令:verdi computer list四、查看工作流信息使用verdi debug命令可以查看正在运行的工作流,如下所示:verdi debug info五、停止正在运行的工作流如果您需要停止正在运行的工作流,请使用以下命令:verdi process kill [process_id]六、调用远程函数如果您想在远程计算机上调用某个函数,则可以使用以下命令:verdi run [remote_function]七、查看计算状态如果您需要了解计算的当前状态,可以使用以下命令:verdi process status [process_id]八、查看计算输出如果您需要查看计算的输出文件,请使用以下命令:verdi process show [process_id]九、查看计算结果如果您需要查看计算的结果,在verdi中有两种方法可以实现。

第一种方法是使用以下命令:verdi process report [process_id]第二种方法是使用以下命令:verdi process show-result [process_id]十、总结通过使用verdi,您可以更轻松地进行远程调试,并了解计算的当前状态和结果。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Verdi思源科技股份有限公司Verdi基本培训基于Verdi 2010.01版权©2009 Spring Soft.Inc.保留所有版权没有思源科技股份有限公司的书面许可,不得以任何形式或任何方式复制这个培训的内容。

商标文件中所用到的产品名称是他们各自的所有商标或注册商标。

机密文件中的信息是机密的,并且适用于思源科技与贵组织之间的许可协议。

使用和公开是受限制的。

目标帮助你理解复杂设计当发现bug时,帮助你快速追踪到根源在一个统一且友好的环境中做调试和验证目标受众结构工程师开发工程师验证工程师必要条件基本的HDL/HVL编程能力:Verlog,VHDL,System Verilog,SVA熟悉标准的仿真器摘要技术背景建立环境理解FSDB Dumping(存储)任务和重用性输入设计在源代码界面调试在波形界面调试在原理图界面调试在FSM界面调试在时序界面调试附录:常用参数术语:RMB Right Mouse Button 鼠标右键MMB 鼠标中键LMB 鼠标左键DC 双击D&D 拖拽KDB 知识数据库模块FSDB 快速信号数据库TFV 时序界面BA 行为分析技术背景在设计流程中调试ESL RTL Gate设计 SCAN 时序构建行为 设计(定位) Testbench 验证交互正式回归 编译器 扫描 收敛 验证交互方式IP遗产 断言属性 仿真/加速你知道你的团队调试花费多少时间吗?你会用那个时间做什么?阻碍有效调试复杂设计更难理解复杂的行为复杂设计引起并影响方案增加验正条件复杂的多用工具、多组环境混合方法复杂性Novas解决艰难的调试问题问题复杂环境复杂行为复杂设计理解 自动化 统一增加自动化 Verdi强大的理解和调试Novas技术编译器和接口 数据库 分析引擎 形象化→知识数据库→行为分析 时序界面↓ 结构分析 源代码工具的全范围→FSDB →断言评价 → 波形/事件事件数据库 事务/信息分析 原理/结构FSM/流表断言/信息/事务理解调试系统——不只简单的形象化结构/事件调试过程当前过程包括比较时间、代码和结构在多种窗口跟踪可能的问题。

——浪费时间,容易出错,复杂自动调试过程决定生产力的提高在调试过程方面利用基于行为调试来自动化时间消耗时间和结构在一个界面中设计行为的直接行为自动的起因/影响追踪快速理解问题区域缩短你用传统方法调试的时间建立环境目标建立环境完成这一章节后,你应该能够……运行之前建立环境指定路径和环境变量二进制、许可、符号库使用建立文件——novas.rc指定参数理解FSDB转存任务重用性快速信号数据库介绍(FSDB)用仿真器链接Novas项目文件为了FSDB转存FSDB重用指定路径和环境变量二进制文件设置环境变量NOVAS_INST_DIR<Novas安装路径>设置路径=($NOVAS_INST_DIR/bin $path)许可文件设置环境变量 NOVAS_LICENSE_FILE<licence_file>:$NOVAS_LICENSE_FILE或者使用LM_LICENSE_FILE搜索优先权比NOVAS_LICENSE_FILE低符号库背景为什么使用符号库?提供源代码和逻辑元件之间的映射。

没有符号映射活跃的扇入锥,扇入锥和扇出锥原理不会正常工作原理图将仅展示方框而不是逻辑单元。

使用符号库使用下列任一方法创建符号库:syn2SymDB:对于Synopsys逻辑库文件用ASCⅡ格式(.lob)map2SymDB:对于准备好的映射文件从<verdi_install>/doc/Symbol_Library.pdf查看开发人员指南文件得到详细格式。

设置符号库环境变量setenv NOVAS_LIBS"<LIB ROOT#1><LIB ROOT#2>..."setenv NOVAS_LIBPATHS"<Directory#1><Drectory#2>..."通过GUI(图形用户界面)设置符号库调用Tools→Preferences命令来打开参数格式;选择文件夹Schematics→SymbolLibrary在Symbol Library Names 区域输入符号库名称在Symbol Library Paths输入区域该设置将会保存到novas.rc源文件使用创建文件——novas.tc包括:为预编译的设计映射信息映射一个库文件名到一个物理定位映射格式[library]logical name=物理地址(例pack=./work)pack=./library/pack (例vital=./work)用户参数(设置方式Tools→Preferences)指定路径使用NOVAS_RC环境变量。

setenv NOVAS_RC <path>/novas.rc在命令行直接通过 -rcFile<文件名>搜索顺序:1.-rcFile<文件名>命令行选项(读/写指针)2.NOVAS_RC 环境变量(读/写指针)3../novas.rc4.$HOME/novas.rc5.<Verdi instal>/etc/novas.rc指定参数摘要1.通过从窗口调用Tools→Preferences打开参数设置(1)修改被保存在novas.rc源文件中的格式(2)在Find栏搜索关键词2.参考目录以得到常用参数快速信号数据库(FSDB)介绍1.包含仿真信号数据的压缩二进制文件格式2.开放文件格式以便其他支持工具能转存数据,例如:Verisity、Vera、Ikos等。

3.VHDL和Verilog都可以在仿真期间使用系统任务来转存数据;常用系统任务1.fsdbDumpfile——指定FSDB文件名,限制FSDB文件大小(1)通过用户滑动窗口机制来保留FSDB文件中的最后信号值,如果文件大小超过了限制就扇出旧的值。

2.fsdbDumpvars——转存信号指定实例和深度的变化。

(1)也能够指定FSDB文件名,在每个fsdbDumpvars命令中可以指定不同的FSDB文件名3.fsdbDumpon/fsdbDumpoff——开/关FADB转存(1)能指定FSDB文件名来开/关FSDB文件4.fsdbSwitchDumpfile——转换转存到其他FSDB文件5.fsdbAutoSwitchDumpFile——限制FSDB文件大小并自动转换转存到新FSDB文件注1:以上任务是对VHDL仿真而言的,在Verilog仿真中要加上“$"前缀注2:要得到更多的系统任务,请参考Linking Novas Files with Simulators和Enabling FSDB Dumping(<NOVAS_INST_DIR>/doc/linking_dumping.pdf)为FSDB转存链接Novas项目文件1.创建工具环境变量(1)setenv LM_LICENSE_FILE<simulator_license_file>(2)<Simulator>_INST_DIR(3)NOVAS_INST_DIR(4)使用LD_LIBRARY_PATH来指定适合被分享的项目文件,常用库放在 ${NOVAS_INST_DIR}/share/PLI/libsetenv LD_LIBRARY_PATH${NOVAS_INST_DIR}/share/PLI/<simulator>/<platform>;${NOVAS_INST_DIR}/share/PLI/lib/<platform>;支持的仿真器:VCS/IUS/MODELSIM2.创建工作裤并为仿真编译设计3.在仿真器命令提示符上运行并调试FSDB转存函数。

注意:要得到更多的仿真器链接细节,请参考<NOVAS_INST_DIR>/doc/linking_dumping,pdf文件FSDB重用批处理FSDB文件1.vfastVCD文件转换成FSDB文件2.fsdb2vcdFSDB文件转换成VCD文件3.fsdbextract从现有的没有再仿真的FSDB文件提取信号、范围、时间周期4.fsdbmerge将几个FSDB文件合并为1个5.fsdbreport生成一个指定信号值变化的报告注:使用<utility> -h 列出所有选项或查看Verdi Command Reference 获取更多信息注:参考Verdi Command Reference中的Utilities章节获取完整的实用列表总结在这一节,你学到了:1.在运行Verdi之前怎样建立环境;2.怎样指定参数3.怎样理解FSDB转存任务和实用。

输入设计:目标输入设计完成本节后,你应该能够:1.在命令行输入设计(1)从文件(2)从库(3)通过重复运行一个TCL(终端控制语言)命令文件2.从GUI(图形用户界面)导入设计(1)从文件(2)从库在命令行导入设计从文件Verdi [Verdi 选项] [你的Verilog选项]1.在命令行参考源文件(仅Verilog)2.Verdi所有的Verilog命令行选项%verdi -f <文件列表> +定义+充分利用你的时间%verdi <源文件1> <源文件2> ...* 文件列表有一个包含Verilog源文件和任何命令行转换器的文件。

%verdi -ssv -v lib.v +libext+.v -ssy -y/src/abc-y/src/def top.v* -ssv和-ssy对于指定的带有-v和-y的设计文件只需要一次,top.v是设计文件。

在命令行导入设计从库1.编译一次,加载多次;2.保存加载时间和全部记忆;3.对于混合语言或VHDL设计是有必要的,对于仅用Verilog语言设计是可选择的;4.预编译设计进入库:vericom用于Verilog代码,vhdlcom用于VHDL代码$ vericom -lib <库名> block1.v block2.v block3.v$ vhdlcom -lib <库名> block1.vhd block2.vhd block3.vhd5.然后导入编译后的库并指定顶层模块$ verdi -lib <库名> -top TopBlock例:$ verdi -lib work -top system在命令行导入设计通过重复运行一个TCL命令文件1.在VVerdi中每一个被执行的TCL命令都有一个相对应的TCL命令被保存在./verdiLog/verdi.cmd文件 (1)该文件能被复制和修改到自动化常用命令;(2)随后新文件能够使用:% verdi -play <文件>.cmd 在Verdi中再次运行。