基于FPGA的宽带信号数字下变频设计与实现

宽带信号数字下变频技术的FPGA实现

• 189•两路供电一路是NORMAL POWER,一路是ESS POWER,线路图上也是两路供电但实际操作中按要求拔出跳开关后DEU 上还有电,带电拆装容易损坏DEU ,所以在进行拆装时还要整机断电(图1)。

AMM 23-73-00-22700-00-B 。

2)DEU 的联接端和终端:DEU 上的终端/联接端盒是根据DEU 在飞机上的安装位置决定的IPC23-73-09-08H 图而且两者件号是不同的(图2、图3)。

航后报告有故障信息CAM NOT LOADED 或OBRM/CIDS(101RH)-SDF1之类故障一般就要重新安装CAM 或OBRM 卡然后进行测试。

注意COM 卡和OBRM 及PRAM 卡在FAP上会显示件号,拔出后会显示图2图3NONE ,重新安装后要做一遍上电测试才会出现件号。

航后报告有信息SMOKE 一般情况下要更换DIRECTOR,因为烟雾探测是有CIDS 计算机SDF 部分的功能。

总结:CIDS 系统功能强大涉及到的部件及故障多种多样,引起的原因也各不相同,排故时要考虑到的东西很多,我们平时要本着从易到难,从简单到复杂的思路进行排故,尽量不要把问题搞大。

因为虽然CIDS 系统大都是客舱内的故障但有些还是影响飞行或者是根本就无法放行,所以对CIDS 系统还是要有一定的了解,对我们在航前,过站能快速准确的对相应的故障有一个正确处理措施保障航班的正常运行有很大的帮助。

引言:雷达发射信号的带宽直接决定雷达的距离分辨率,高分辨率目标识别雷达要求更高的信号带宽,以实现对目标型号的具体识别。

对于要求信号实时处理的雷达系统,高速的ADC 采样速率与低速的FPGA 流水处理速率,需要引入多相滤波理论,通过并行多相分解实现FPGA 低速处理高速的ADC 采样信号,并且通过合适的抽取速率以降低数字下变频后信号的处理速率。

1 数字下变频的多相分解传统的窄带信号数字下变频理论是将信号混频、低通滤波、抽取。

基于FPGA的超宽带数字下变频设计

1 引 言

随 着 雷 达 应 用 需 求 的 提 高和 数 字 信 号 处 理 技 术 的 迅 速 发 展 ,对 雷达 接 收 系 统 的设 计 也越 来越希望符合软件无 线电的设计思想 ,即将A D C 尽可能靠近天线 ,将接 收到的模 拟信号尽早数

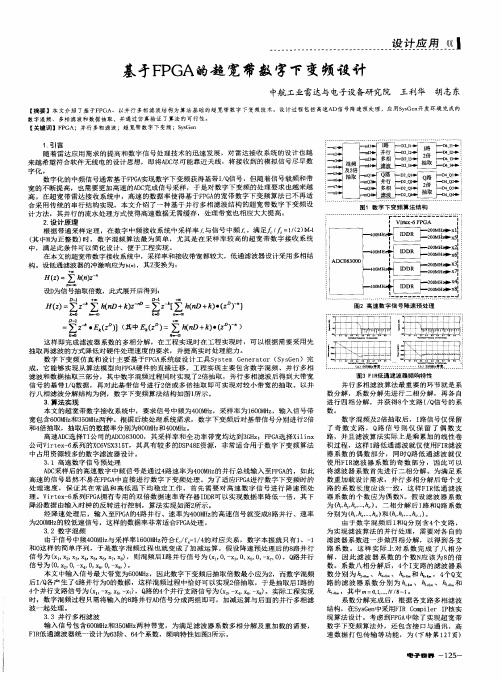

字化 。 数 字 化 的 中 频信 号 通 常 基 于F P G A 实现 数 字 下 变 频 获 得 基 带 I / Q 信 号 , 但 随 着 信 号 载 频 和 带 宽 的不 断提 高 , 也 需 要 更 加 高 速 的 A D C 完 成 信 号 采 样 ,于 是 对 数 字 下 变频 的 处 理 要 求 也 越 来 越 高 。在 超 宽 带 雷 达 接 收 系 统 中 , 高速 的 数 据 率 使 得 基 于 F P G A 的宽 带 数 字 下 变 频 算 法 己 不 再 适 合 采 用 传 统 的 串 行 结 构 实 现 ,本 文 介 绍 了一 种 基 于 并 行 多 相 滤 波 结 构 的 超 宽 带 数 字 下 变 频 设 计 方法 , 其 并 行 的 流 水 处 理 方 式 使 得 高 速 数 据 无 需缓 存 , 处理 带 宽 也 相 应 大 大 提 高 。 2 . 设 计原 理 根 据 带 通 采 样 定 理 ,在 数 字 中 频 接 收 系 统 中 采样 率 与 信 号 中频 。满 足 / =1 / ( 2 ) M- 1

日 ( z ) :∑ h ( n ) z

月-

设D 为信 号 抽 取 倍 数 , 此式 展 开 后 得 到 :

D- J + ∞ D- 1 - 嘲

—4 0 0 M H I D D R _; l o 0 M H

图 2 高 一2 0 0 MH m l I  ̄ X 4

基于FPGA的数字下变频器的设计与应用

s Pd h s p fqe y dMd dn 1 r g adf 1酗 . 七 u Oi i a l r u c a e ya c e n o e P n g m 吨 e n n g h m a n g n n 丁e 幼re r e etho g h be d e i fmd i b ead d i I e se i en l ae n vl n r i t a n t i t F ls cv c o s r y e Og o g s P l a b o g . l a Tu i ps et iP e t 诫d b d d i 11 r i r a o 七s s o i o m l n h e a w t g I e v b e n t i l b m e ie n i hd t F c e s a e d b da s Pn t o n s m i e a P sa l h 移 g

程性和灵活性,从而满足不同的工程设计需求。

本文章首先阐述了软件无线电中关键的数字信号处理技术,包括中频处理中

的下变频技术、 抽取技术以 及带通采样技术。 利用 M J A 八I B的 s u 完成了 il mi k n

对系统 设 仿 验证了 计的 确 之后用Qa s 进行了 的 计与 真, 设 正 性. utl x l o 基于FG PA

朋dh es P. sg P o d i m t dt w o D C nt i id c n lh e i T ・ 姗 e g e ,h h1 D f co s v e a a U no D s n h e o e o i d id n o ay 苗 m l n dr ce t m n u t lP et e e v卜胡dO a 笙dt t m dl ir ‘ 飞 n s m e e st Pi r 叮 o h ou b r 认 e g J e ela y

数字下变频电路的FPGA实现

数字下变频电路的FPGA实现随着数字化时代的到来,数字信号处理技术已经成为了许多领域中不可或缺的一部分。

其中,数字下变频技术是一种非常重要的数字信号处理技术,被广泛应用于雷达、通信、音频处理等领域。

本文将介绍数字下变频电路的FPGA实现。

数字下变频电路的基本原理数字下变频电路的基本原理是将输入信号进行混频,将高频信号转换为低频信号,并对低频信号进行采样和滤波,得到一个纯净的低频信号。

数字下变频电路通常由数字信号处理器、数字乘法器和数字低通滤波器等组成。

FPGA实现数字下变频电路的优势 FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,能够根据需要实现各种数字电路。

与传统的数字信号处理芯片相比,FPGA具有以下优势:高速并行处理能力:FPGA内部具有大量的可编程逻辑器件,可以实现高速并行处理,提高处理速度和效率。

灵活性:FPGA可以通过重新编程实现不同的数字电路,方便灵活,可以快速适应不同的应用场景。

可靠性:FPGA内部具有严格的质量保证措施,保证了数字电路的可靠性和稳定性。

设计数字下变频电路的算法:根据具体应用场景和要求,利用MATLAB 等软件设计数字下变频电路的算法。

将算法转换为硬件描述语言:将设计的数字下变频电路算法转换为硬件描述语言(如VHDL或Verilog),并利用EDA工具进行仿真和验证。

将硬件描述语言编译成二进制文件:将生成的硬件描述语言编译成二进制文件,以便在FPGA上实现。

将二进制文件下载到FPGA中:将生成的二进制文件下载到FPGA中,通过调试和测试,最终实现数字下变频电路。

结论数字下变频电路的FPGA实现具有高速并行处理能力、灵活性和可靠性等优势,已经被广泛应用于雷达、通信、音频处理等领域。

通过设计算法、转换为硬件描述语言、编译成二进制文件以及下载到FPGA中等步骤,可以实现数字下变频电路的高效、快速和可靠实现。

数字下变频电路是一种重要的信号处理单元,它在通信、雷达、电子对抗等领域有着广泛的应用。

基于FPGA的软件无线电数字下变频技术的研究的开题报告

基于FPGA的软件无线电数字下变频技术的研究的开题报告1. 研究背景近年来,随着无线通信技术的快速发展,软件无线电技术已经成为了无线通信领域的一个重要研究方向。

数字下变频技术是软件无线电技术中的一个重要环节,它能够将高频信号转换成低频信号,使其能够被数字信号处理器所接收和处理。

目前,数字下变频技术已经得到了广泛的应用,例如在卫星通信、广播电视、雷达及无线局域网等领域。

FPGA技术,作为一种新型的可编程逻辑器件,具有低功耗、高性能、灵活性强等特点,已经被广泛应用于数字信号处理、通信系统等领域。

因此,基于FPGA的软件无线电数字下变频技术的研究具有非常重要的意义。

2. 研究内容本文将基于FPGA平台,研究软件无线电数字下变频技术的实现。

具体的研究内容如下:(1)研究数字下变频技术的基本原理,了解其在无线通信中的应用及其优势;(2)设计基于FPGA的软件无线电数字下变频系统方案,包括系统的硬件架构和软件设计;(3)针对系统中的核心算法进行深入研究,例如数字混频、I/Q解调等,并对其进行优化;(4)进行系统的仿真测试,验证系统的正确性和性能,例如系统时延、功耗等方面的测试。

3. 研究意义本研究对于推动软件无线电技术的发展具有重要的意义。

具体的研究意义如下:(1)基于FPGA的软件无线电数字下变频技术具有很大的应用前景,该研究可为相关行业提供新的技术手段,提高无线通信领域的技术水平;(2)FPGA技术在本研究中得到了广泛应用,该研究可拓宽FPGA技术的应用领域和深度应用;(3)本研究的研究成果能够为软件无线电技术的研究提供新的思路和方向,促进其发展壮大。

4. 研究方法本研究采用实验法、仿真法和理论分析法相结合的方法进行研究。

具体的研究方法如下:(1)采用实验法,设计并构建出基于FPGA的软件无线电数字下变频系统,完成系统的调试和测试,并获取实验数据;(2)采用仿真法,运用软件仿真工具对系统进行仿真测试,并获取系统的性能参数;(3)采用理论分析法,对系统中的核心算法进行分析和优化。

基于FPGA的宽带信号数字下变频设计与实现

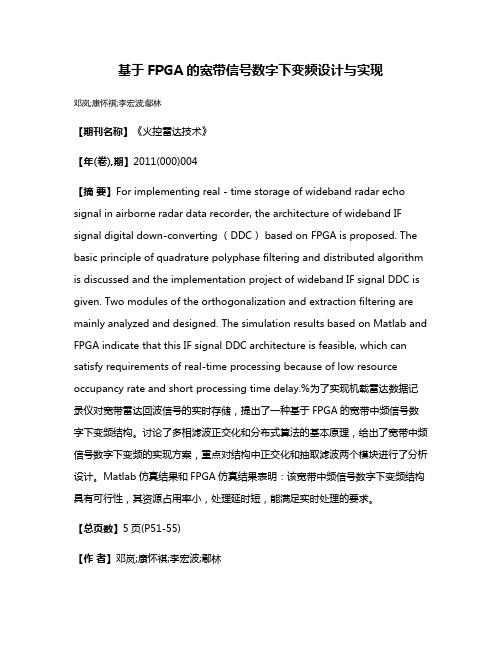

基于FPGA的宽带信号数字下变频设计与实现邓岚;康怀祺;李宏波;鄢林【期刊名称】《火控雷达技术》【年(卷),期】2011(000)004【摘要】For implementing real - time storage of wideband radar echo signal in airborne radar data recorder, the architecture of wideband IF signal digital down-converting (DDC) based on FPGA is proposed. The basic principle of quadrature polyphase filtering and distributed algorithm is discussed and the implementation project of wideband IF signal DDC is given. Two modules of the orthogonalization and extraction filtering are mainly analyzed and designed. The simulation results based on Matlab and FPGA indicate that this IF signal DDC architecture is feasible, which can satisfy requirements of real-time processing because of low resource occupancy rate and short processing time delay.%为了实现机载雷达数据记录仪对宽带雷达回波信号的实时存储,提出了一种基于FPGA的宽带中频信号数字下变频结构。

基于FPGA的超宽带数字下变频设计

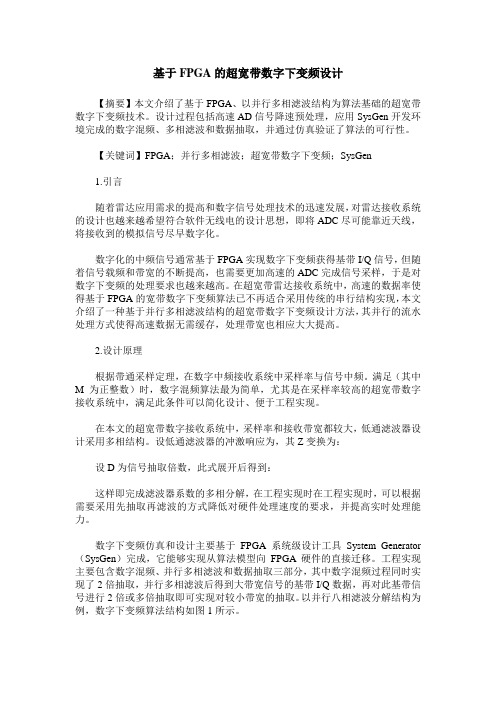

基于FPGA的超宽带数字下变频设计【摘要】本文介绍了基于FPGA、以并行多相滤波结构为算法基础的超宽带数字下变频技术。

设计过程包括高速AD信号降速预处理,应用SysGen开发环境完成的数字混频、多相滤波和数据抽取,并通过仿真验证了算法的可行性。

【关键词】FPGA;并行多相滤波;超宽带数字下变频;SysGen1.引言随着雷达应用需求的提高和数字信号处理技术的迅速发展,对雷达接收系统的设计也越来越希望符合软件无线电的设计思想,即将ADC尽可能靠近天线,将接收到的模拟信号尽早数字化。

数字化的中频信号通常基于FPGA实现数字下变频获得基带I/Q信号,但随着信号载频和带宽的不断提高,也需要更加高速的ADC完成信号采样,于是对数字下变频的处理要求也越来越高。

在超宽带雷达接收系统中,高速的数据率使得基于FPGA的宽带数字下变频算法已不再适合采用传统的串行结构实现,本文介绍了一种基于并行多相滤波结构的超宽带数字下变频设计方法,其并行的流水处理方式使得高速数据无需缓存,处理带宽也相应大大提高。

2.设计原理根据带通采样定理,在数字中频接收系统中采样率与信号中频。

满足(其中M为正整数)时,数字混频算法最为简单,尤其是在采样率较高的超宽带数字接收系统中,满足此条件可以简化设计、便于工程实现。

在本文的超宽带数字接收系统中,采样率和接收带宽都较大,低通滤波器设计采用多相结构。

设低通滤波器的冲激响应为,其Z变换为:设D为信号抽取倍数,此式展开后得到:这样即完成滤波器系数的多相分解,在工程实现时在工程实现时,可以根据需要采用先抽取再滤波的方式降低对硬件处理速度的要求,并提高实时处理能力。

数字下变频仿真和设计主要基于FPGA系统级设计工具System Generator (SysGen)完成,它能够实现从算法模型向FPGA硬件的直接迁移。

工程实现主要包含数字混频、并行多相滤波和数据抽取三部分,其中数字混频过程同时实现了2倍抽取,并行多相滤波后得到大带宽信号的基带I/Q数据,再对此基带信号进行2倍或多倍抽取即可实现对较小带宽的抽取。

基于FPGA的高速数字下变频系统设计

基于FPGA的高速数字下变频系统设计摘要:基于FPGA设计了一高速数字下变频系统,在设计中利用并行NCO和多相滤波相结合的方法有效的降低了数据的速率,以适合数字信号处理器件的工作频率。

为了进一步提高系统的整体运行速度,在设计中大量的使用了FPGA中的硬核资源DSP48。

Xilinx ISE14.4分析报告显示,电路工作速度可达360MHz。

最后给出了在Matlab和ModelSim中仿真的结果,验证了各个模块以及整个系统的正确性。

数字下变频(Digital Down Conversion,DDC)是软件无线电系统的关键模块之一,其可将高频数据流信号变成易于后端数字信号处理器(Digital Signal Processor,DSP)设备实时处理的低频数据流信号。

在数字下变频实现中,随着信号采样率的不断提高,数据率也会相应的提高,但是实际应用中随着数据速率的不断提高,数据处理器件(如FPGA)的处理速度会无法满足要求而不能正常工作,从而带来了数字信号处理的瓶颈问题。

本设计就是以多路并行NCO技术为基础,研究了如何在FPGA中用多路并行采样数据的方式来解决数据处理器件无法提供高速率的匹配信号的问题,并给出了高速DDC实现的架构和仿真结果。

1 数字下变频基本原理数字下变频主要由频谱搬移和抽取两部分组成,如图1所示,其中频谱搬移包含数控振荡器(Numerically Controlled Oscillators,NCO)、乘法器和低通滤波器(LPF,Low Pass Filter);抽取包含抽取滤波器(LPF2)和D倍的抽取,LPF2是为了限制信号的频谱,以免抽取后发生混叠。

模拟信号经过A/D转换后分成两路信号,一路信号和NCO输出的正弦信号相乘(同相分量),一路和NCO输出的余弦信号相乘(正交分量),之后经过低通滤波器(LPF1)将高频分量滤除,然后信号经过抽取滤波以降低速率,最终输出的两路信号就可以送往后续的数字信号处理器中做进一步的处理。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

De g L n,Ka g Hu i i iHo g o,Y h L n n a n a q ,L n b a i

( nv syo l t n c nea dTcn l yo C ia hn d 17 1 U i r t e r i Si c n eh o g hn ,C eg u6 1 3 ) e i fE c o c e o f

wh c a aif e u r me t fr a —i r c si g be a s fl w e o r e o c p n y r t n h r r c s i g ih c n s tsy r q ie n so e ltme p o e sn c u e o o r s u c c u a c ae a d s otp o e sn tme d l y i ea . Ke wo d y r s:p lph s le ;d srb t d a g rt m ;DDC;FPGA o y a e f tr it u e lo h i i i

1 引言

针对数字化雷达接收机采样前端 , 目前市面上 已经 出现 了很 多超 高速 多 比特 的 AI 采样 芯片 , D 其

采样 速度 可达 到几 个 Gp , 由此 带来 的 问题 就 是 ss而

搬 移 , 由低 通滤 波 器 滤 波后 , 行 多 倍 抽取 , 到 再 进 达

降速的效果 。对于宽带信 号, 经过 高速 A D采样 / 后, 数据速率可达几 Gp , ss 由于常规的数字 下变频 方法 , 工作速 率 与 A C输 出数据 的速 率一致 , D 而

FG P A器 件 无 法 达 到 如 此 高 的运 行 速 度 , 因此 采 用 常规 的数 字 下变频 方法无 法 实现对 宽带 中频信 号 的

s nd i e .T e smu ai n r s l a e n Malb a d F G n iae t a h sI i n lD r h t cu e i f a i l , g h i l t e u t b s d o t n P A i dcs a t g e

第4 0卷 第 4期 ( 总第 18期 ) 5 21 年 1 0 1 2月

火控雷达技术

F r o t lRa a e h oo y ie C n r d rT c n lg o

V 1 0N . ( e e 5 ) o. o4 S r s 8 4 i 1

De . 2 1 e 01

I ina F sg lDDC s gv n.Two mo u e ft e o t o o aiai n a xr c in fl rn r i l n lz d a d de i i e d l so h rh g n lz t nd e ta t ti g a e man y a ay e n — o o i e

关键词 : 多相滤波 ; 分布式算法; D F G D C;P A 中图分类号 :N 1. 2 T 9 17 文献标志码 : A 文章编号 :0 885 (0 1 0 -5 -5 10 —6 2 2 1 )40 1 0

De in a d I lm e tto fW i e a d Sg a gt l wn — s n mp e n ai n o d b n in l g Di i a Do —

o u da r o p aeft n n ir u da oi m i dsusda dtei pe ett npo c o ie ad f art ep l h s l r ga dds b t l rh i se n lm nai r e t f d bn q u y ie i t e g t s c i h m o j w

Ab t a t s r c :Fo mp e n i g r a ri lme tn e l—t tr g fwi b n a a c o sg a n ar o n a a aa r c r e i so a e o de a d r d re h in li ib r e r d rd t e o d r,t e me h

基于 FG P A的宽 带 信 号数 字下 变 频 设计 与实 现

邓 岚 康 怀祺 李宏波 鄢 林

( 电子科技 大学 成都 6 13 ) 17 1

【 摘要】 为了实现机载雷达数据记 录仪对宽带雷达回波信号的 实时存储 , 出了一种基 于 F G 提 P A的

宽带 中频信 号数 字下 变频 结 构。讨论 了多相滤 波正 交化 和 分布 式 算 法 的基本 原 理 , 出了 宽带 中 给

频信 号数 字 下变频 的 实现 方案 , 重点 对 结构 中正 交化 和抽 取 滤 波 两个 模 块进 行 了分析 设计 。 M t a .

1 仿真结果和 F G a b P A仿真结果表明: 该宽带中频信号数字下变频结构具有可行性, 其资源占用率 小, 处理延 时短 , 满足 实时 处理 的要 求 。 能

aci cueo ie adI i a dg a d w —o vrn D C)b sdo P A i pooe .T e ai pic l rht tr f db n s n l i t o ncn et g( D e w F g il i ae nF G rp sd h s r i e s b c np